热门标签

热门文章

- 1docker错误 download failed after attempts=6 :net/http :tls handshake timeout_docker: error pulling image configuration: downloa

- 2[附源码]java+ssm计算机毕业设计医院药品进销存系统【源码+数据库+LW+部署】_公立医院的进销存数据需要本地部署吗?

- 3Netbeans的编译和打包ant脚本----英文版_netbeans ant

- 4操作系统内核概念

- 5关于计算机如何区分有符号数与无符号数_有符号数和无符号数的区别

- 6mybatis动态SQL对数据库执行增删改查学习笔记_getusercountbyroleid为根据角色id查询该角色下是否有用户信息。返回该角色id下的

- 7西南科技大学数字电子技术实验一(数字信号基本参数与逻辑门电路功能测试及FPGA 实现)FPGA部分_大学数电实验

- 8SAP HR 工资核算异常的一些处理方式_sap 重新入职人员工资核算 报错期间开始 2023.10.01 早于最早可能的 ra 运行日期

- 9Windows 源码编译 MariaDB_mariadb odbc 驱动源码 windows 下 如何编译

- 10报错:The installer has encountered an unexpected error installing this package 使用超管运行安装文件

当前位置: article > 正文

利用74LS138实现4-16译码器,并在QuartusⅡ上进行仿真_4-16线译码器74ls138

作者:小蓝xlanll | 2024-05-18 15:00:30

赞

踩

4-16线译码器74ls138

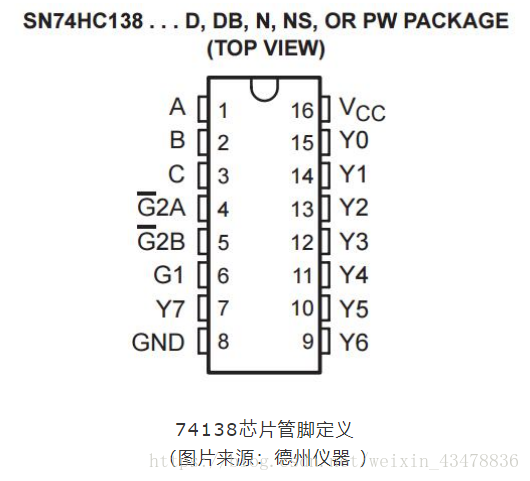

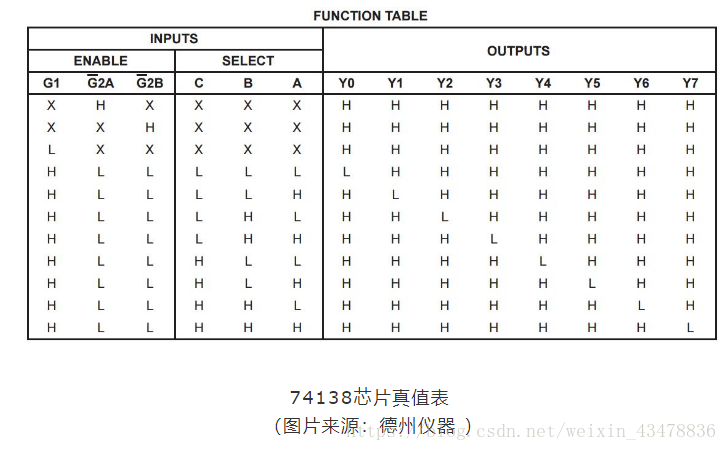

一.74LS138芯片基本功能介绍

在数字集成电路的早期时代, 对于一些常用的小型逻辑, 比如3-8 译码器 会被集成进一颗芯片, 例如74138芯片就是一颗实现3-8译码器的常用组合逻辑芯片。 下图分别是74138芯片的管脚定义、真值表以及内部逻辑结构

二.利用74LS138实现4-16译码器

设计要求:

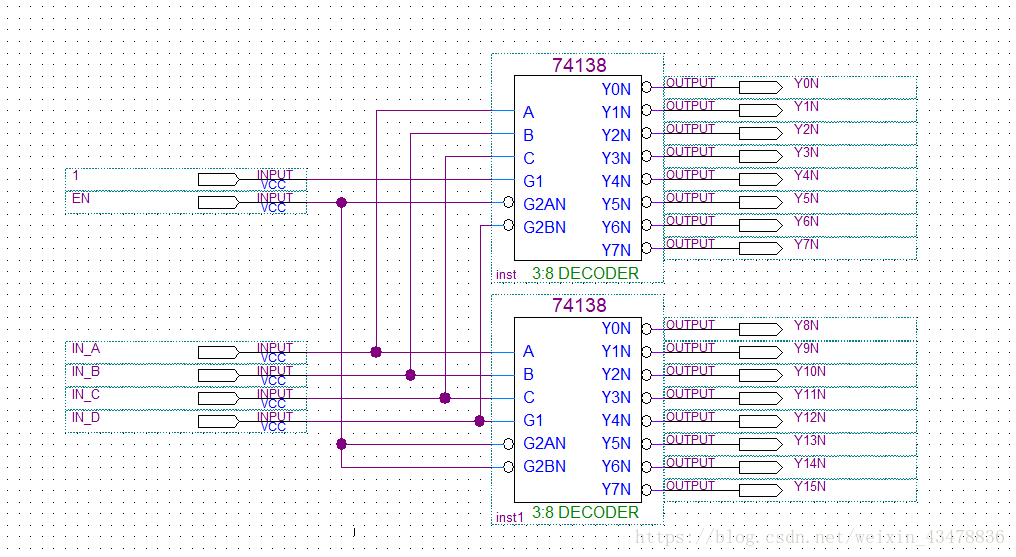

· 用2片3-8 译码器拼接成4-16 译码器

· 仿真验证电路的正确性

· 注意观察输出信号的毛刺(竞争冒险)

设计思路:

如下图所示,我们让最高位输入IN_D接到片1的G2BN,接到片2的G1,这样若IN_D=0,则上方的芯片被选中,下方芯片被禁用,若IN_D=1,则相反。

电路逻辑设计如下:

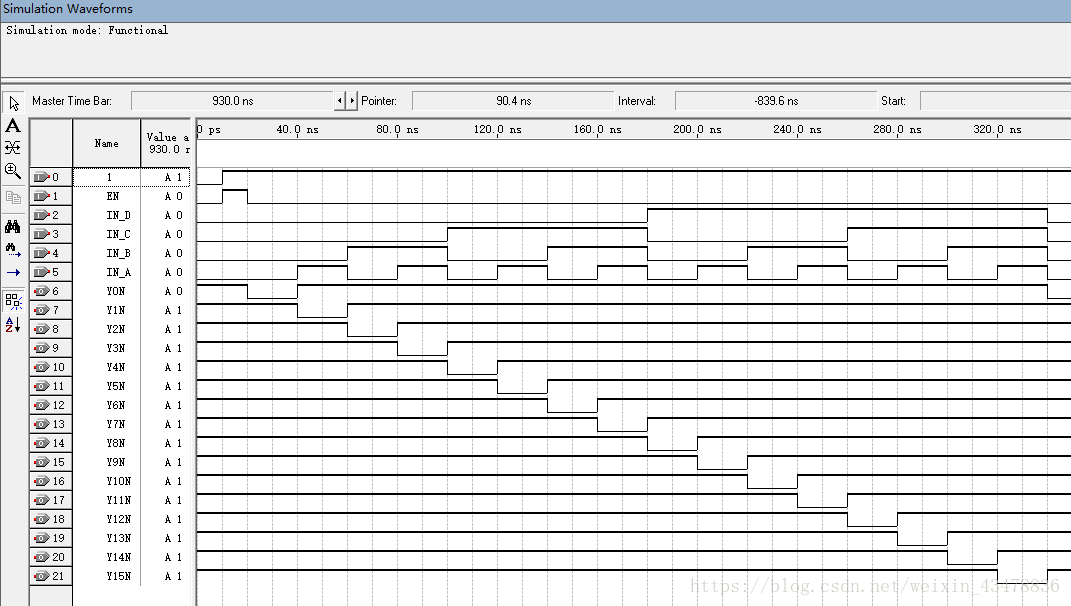

用QuartusⅡ进行功能性仿真后得:

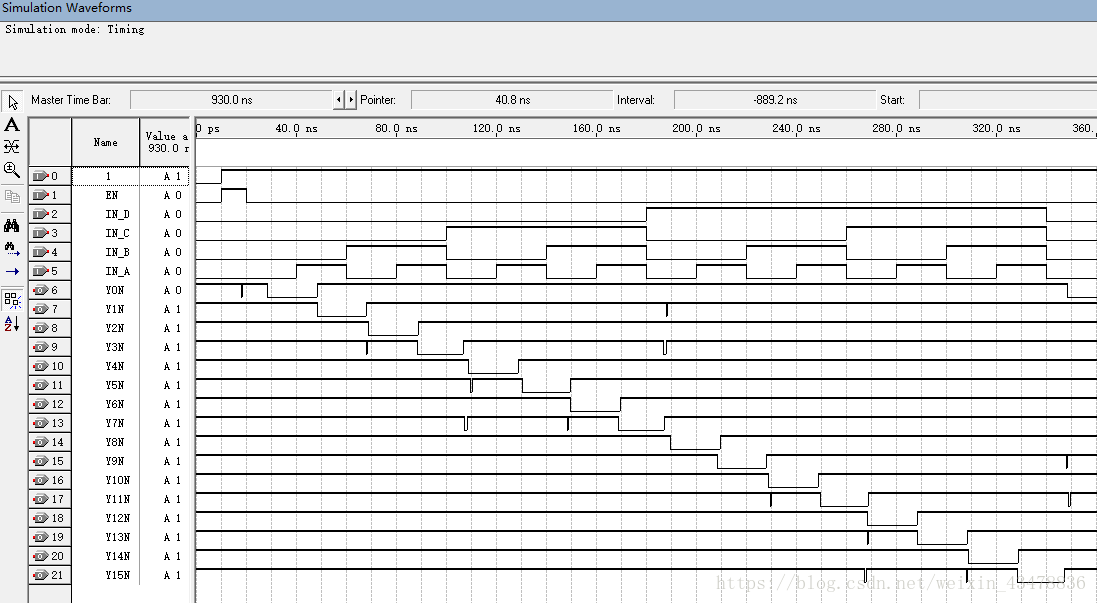

用QuartusⅡ进行时序性仿真后得:

仿真结果符合预期,且出现了“毛刺”,即电路的冒险与竞争现象,这是由于逻辑门存在延迟以及信号的传输路径不同造成的,当输入信号电平发生瞬时变化时,电路就可能产生与稳态时不一致的错误输出。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/588779

推荐阅读

相关标签