热门标签

当前位置: article > 正文

systemverilog中的全局变量与局部变量public、local、protected的探索与代码验证_systemverilog 全局变量

作者:我家小花儿 | 2024-04-21 11:11:40

赞

踩

systemverilog 全局变量

1、背景

最近转行IC验证中,在学习systemverilog,发现有些方面sv和C++非常相似,比如类class、静态变量、全局变量和局部变量的继承等等方面。为了保证这些逻辑是一样的,特别做了几个小的case用于验证这些相关的特性。

2、public、local、protected

这三个关键字,熟悉C++的同学一定不会陌生。在systemverilog中这个功能是一致的。分为三个方面:

(1)public:首先,变量在无修饰情况下默认为是public类型,此类型也是最“暴露”的类型。用此关键字修饰(或者无修饰默认此修饰)的变量或者方法都可以被外部调用或者类继承;

(2)local:此关键字意味着这个变量或者方法只能在这个类class中使用,不能被外部调用或者类继承;

(3)protected: 此关键字意味着这个变量或方法可以被类继承使用,但是不能被外部调用。

字数太多,看表:

| key word | 类中可调用 | 继承类可调用 | 外部可调用 |

| public/NULL | 是 | 是 | 是 |

| local | 是 | 否 | 否 |

| protected | 是 | 是 | 否 |

2.1 验证public

先验证public关键字是否如分析一致。代码如下。

- `timescale 1ns/1ps

- `include "uvm_macros.svh"

-

- import uvm_pkg::*;

-

- module top_tb;

-

- my_test test;

- sub_test s_test;

-

- initial begin

- test = new();

- s_test = new();

- $display("hello, UVM!!!");

- test.play_something();

- s_test.play_parents_para();

- $display("top_tb display a: %0d!!!",test.a);

- $display("top_tb display a: %0d!!!",s_test.a);

- end

-

- endmodule

-

- class my_test;

- bit[7:0] a = 8'h4;

- protected bit[7:0] b = 8'b1111;

- local bit[7:0] c = 8'b1010;

- function void play_something();

- $display("my_test display a: %0d!!!",a);

- $display("my_test display b: %0d!!!",b);

- $display("my_test display c: %0d!!!",c);

- endfunction

- endclass

- class sub_test extends my_test;

- function void play_parents_para();

- $display("sub_test display a: %0d!!!",a);

- endfunction

- endclass

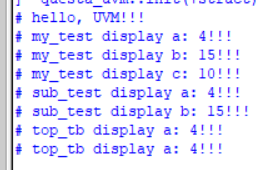

结果如下图所示:

可以看出来a在三个场景的使用都是正常的。

2.2 验证protected

在sub_test的function中加入打印b,这个也是可以的。

但是外部打印b就报错了。

由此可以看出来跟表格中的描述是一致的。

2.3 验证local

跟上述一样去验证local, 分别在外部和继承类中加入打印,发现结果如下:

和预料的一致,说明表格是正确的。这块C++和SV是一致的,从C++转SV还是很友好的。

和预料的一致,说明表格是正确的。这块C++和SV是一致的,从C++转SV还是很友好的。

继续学习中,欢迎交流指正。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/462703

推荐阅读

相关标签