热门标签

热门文章

- 1微信小程序监听键盘变化改变textarea位置_wx.onkeyboardheightchange

- 2Ubuntu18.04误删/lib/x86_64-linux-gnu/libc-2.27.so抢救记录(九十二)

- 3【Linux】nginx安装,及安装SSL_nginx ssl模块安装

- 4linux apache用户密码,Linux下Apache 服务器网页密码设置

- 5机器人:使用模拟器完成自动采石任务_使用模拟器自动做任务

- 6【Git】项目源码迁移到另一个gitlab(保留原来提交历史记录)_第三方的代码迁移到自己的gitlab上保持分支和log记录

- 7使用OLLVM在Windows 10上进行编译和使用_ollvm windows

- 8Krpano学习:在javascript中动态添加/删除/修改(位置)热点(向后端写入)_krpano screentosphere

- 9sublime text 4 4121注册(亲测可用)_sublimetext注册机

- 10python小游戏开心消消乐制作4-点击消除事件

当前位置: article > 正文

vivado 查看模拟波形、总线图查看器_vivado波形图怎么让水平线在中间

作者:我家小花儿 | 2024-05-26 21:46:58

赞

踩

vivado波形图怎么让水平线在中间

查看模拟波形

要将数字波形转换为模拟波形

,

请执行以下操作

:

1.

在“波形

(Waveform)

”窗口的“名称

(Name)

”区域中

,

右键单击总线。

2.

选择“

Waveform Style

”

,

然后选择“

Analog Settings

”

,

以选择合适的绘制设置。

这样即可将总线的数字波形图转换为模拟格式。

您可通过选中然后拖拽各行来调整模拟波形或数字波形的高度。

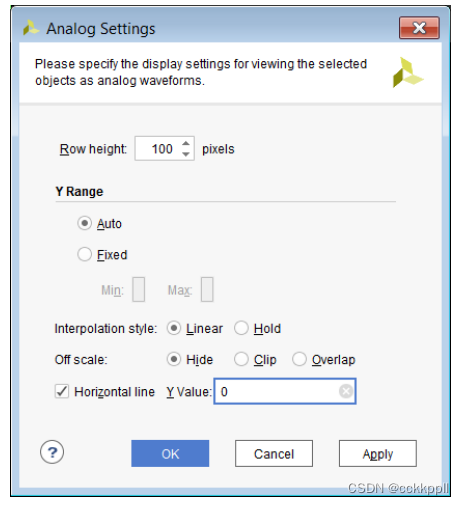

下图所示“模拟设置

(Analog Settings)

”对话框包含对应模拟波形图的设置。

“

Analog Settings

”对话框选项如下

:

• 行高

(Row Height)

:

指定所选波形对象的高度

(

以像素为单位

)

。更改行高不会影响垂直方向显示或隐藏的波形

,

而只是对波形高度进行伸缩。

在“模拟波形”与“数字波形”之间进行切换时

,

行高会设置为对应波形的相应默认值

(

针对数字波形为

20

,

针对

模拟波形为

100

)

。

•

Y

范围

(Y Range)

:

指定波形区域内显示的数字值范围。

• 自动

(Auto)

:

指定只要发现窗口内可见时间范围超出当前范围

,

此范围就持续扩展。

• 固定

(Fixed)

:

指定时间范围保持固定间隔不变。

• 最小值

(Min)

:

指定波形区域底部显示的值。

• 最大值

(Max)

:

指定波形区域顶部显示的值。

这两个值均可指定为浮动值

,

但如果波形对象基数为整数

,

则这些值将被截断至整数。

• 内插样式

(Interpolation Style)

:

指定用于连接数据点的线的绘制方式。

• 线性

(Linear)

:

指定

2

个数据点之间为直线。

• 保持

(Hold)

:

指定在

2

个数据点之间

,

从左侧点绘制

1

条水平线到右侧点的

X

坐标

,

然后绘制另一条线以将前

一条线连接到右侧数据点

,

构成

L

形。

• 超标度

(Off Scale)

:

指定超出波形区域的

Y

范围的波形值的绘制方式。

• 隐藏

(Hide)

:

指定不显示超出范围的值

,

例如

,

达到波形区域上限或下限的波形将消失

,

直至值重新恢复到范

围内为止。

• 剪切

(Clip)

:

指定更改超出范围的值

,

使其位于波形区域顶部或底部

,

这样达到波形区域的上限或下限的波形就

会沿边界呈现为水平线

,

直至值重新恢复到范围内为止。

• 重叠

(Overlap)

:

指定在波形值达到波形窗口本身上限的任意位置都需绘制波形

,

即使其值在波形区域边界外并

与其它波形重叠。

• 水平线

(Horizontal Line)

:

指定是否在给定值绘制水平规则。如果开启此复选框

,

则会在指定

Y

值的垂直位置绘制

1

条水平网格线

,

前提是该值在波形的

Y

范围内。

就像“

Min

”和“

Max

”一样

,

Y

值接受浮点值

,

但如果所选波形对象的基数为整数

,

则会被截断为整数。

重要提示

!

模拟设置保存在波形配置中

;

但由于

Y

维度内缩放控制具有高度交互性

(

不同于基数等其它波形对

象属性

),

因此不影响波形配置的修改状态。因此

,

缩放设置不随波形配置一起保存。

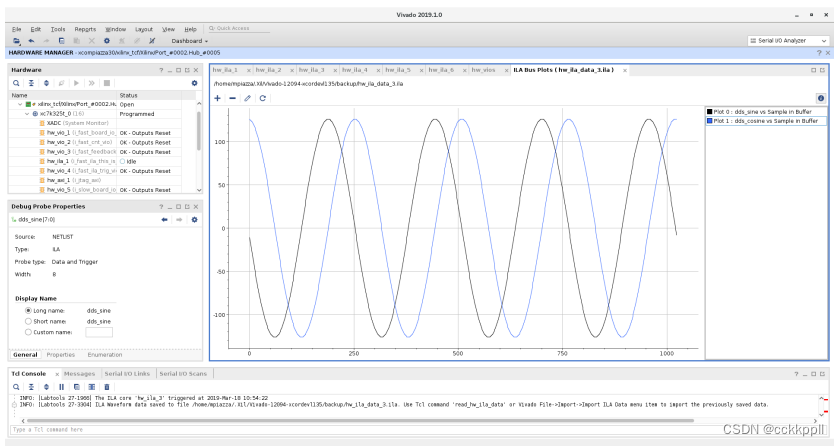

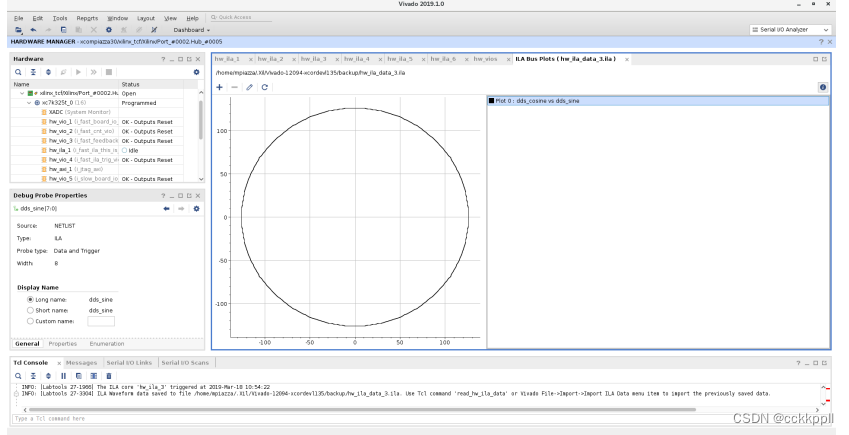

总线图查看器

除模拟波形查看器外

,

Vivado

®

硬件管理器还支持总线图查看器

(Bus Plot Viewer)

,

此查看器允许查看总线值随时间的

变化

,

或者在

X

轴对比

Y

轴上所绘制的

2

个不同总线值的比较。

如需执行以下任一操作

,

则查看“总线图

(Bus Plot)

”很有用

:

• 绘制模拟样本数据与时间的对比

• 绘制模拟样本数据与模拟样本数据的对比

创建总线图

“总线图

(Bus Plot)

”查看器可用于绘制先前采集的

ILA

走线数据。因此

,

它需要指向

ILA

总线图数据文件

(

.csv

或

.ila

)

的路径。默认情况下

,

“显示总线图

(Show Bus Plot)

”对话框会选择最近自动保存的

ILA

触发数据。

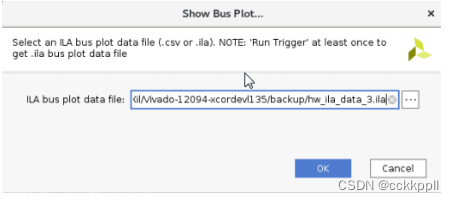

总线图创建示例

1.

要创建总线图

,

请打开

Vivado

硬件管理器并选中“

Tools

” → “

Show Bus Plot

”。

2.

这样会显示“显示总线图”对话框

,

允许选择先前保存的

ILA

数据文件。默认情况下

,

会自动选中对应于最近一次

ILA

追踪的自动保存的

ILA

数据文件。要选择先前保存的

ILA

数据文件

,

请输入指向对应

.ila

或

.csv

文件的路

径。

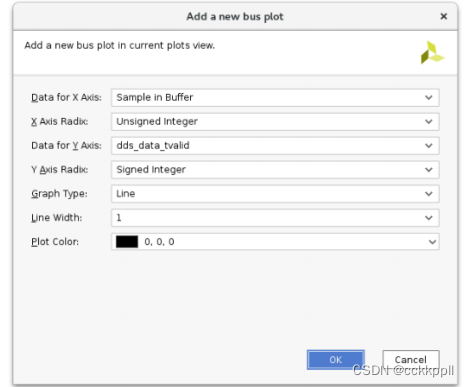

3.

单击“

OK

”

,

这样即可显示空白“总线图

(Bus Plot)

”窗口。要添加总线图

,

请单击“

+

”符号

,

这样会显示

1

个

对话框

,

其中包含配置新总线图的选项。

“添加新总线图

(Add New Bus Plot)

”选项如下所示

:

•

X

轴数据

(Data for X Axis)

:

指定用于

X

轴的总线数据。

○

缓存中的样本数

(Sample in Buffer)

:

ILA

采集缓存中的

ILA

样本数。

○

窗口中的样本数

(Sample in Window)

:

采集窗口中的

ILA

样本数。如果选中任一采集窗口

,

那么此数值与

缓存中的样本数相同

,

但如果使用多个采集窗口

,

那么此数值表示给定采集窗口中的样本数。

○

触发器

(TRIGGER)

:

采集窗口中的触发器位置。

•

X

轴基数

(X Axis Radix)

:

指定绘制

X

轴数据时要使用的基数。

○

有符号整数

(Signed Integer)

。

○

无符号整数

(Unsigned Integer)

。

•

Y

轴数据

(Data for Y Axis)

:

指定用于

Y

轴的总线数据。

○

缓存中的样本数

(Sample in Buffer)

:

ILA

采集缓存中的

ILA

样本数。

○

窗口中的样本数

(Sample in Window)

:

采集窗口中的

ILA

样本数。如果选中任一采集窗口

,

那么此数值与

缓存中的样本数相同

,

但如果使用多个采集窗口

,

那么此数值表示给定采集窗口中的样本数。

○

触发器

(TRIGGER)

:

采集窗口中的触发器位置。

•

Y

轴基数

(Y Axis Radix)

:

指定绘制

Y

轴数据时要使用的基数。

○

有符号整数

(Signed Integer)

。

○

无符号整数

(Unsigned Integer)

。

•

Graph

类型

(Graph Type)

○

线图

(Line)

:

将总线图显示为连接离散样本的连续线段。

○

点图

(Point)

:

将总线图显示为表示离散样本的点。

• 线宽

(Line Width)

:

指定用于在总线图查看器中绘制信号的宽度。

• 图色

(Plot Color)

:

允许选择不同颜色以绘制总线图。

4.

配置总线图后

,

单击“

OK

”以将总线图添加到

Vivado

硬件管理器中。这样即可显示总线图。

注释

:

退出

Vivado

硬件管理器时

,

不保存总线图设置。关闭

Vivado IDE

前

,

请确保所需测量已全部完成。

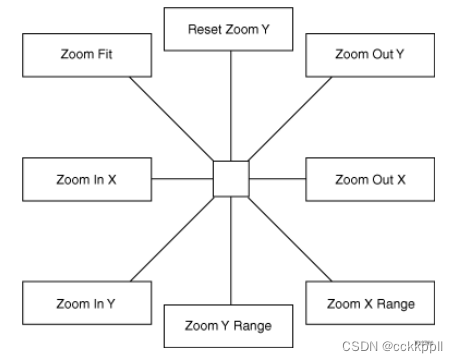

缩放手势

除了支持在

X

维进行缩放的缩放手势外

,

在模拟波形上还可使用额外的缩放手势

,

如下图所示。

要调用缩放手势

,

请按住鼠标左键并按图中所示方向拖动

,

其中起始鼠标位置即图中的中心点。

其它缩放手势如下所示

:

• 沿

Y

轴缩小

(Zoom Out Y)

:

沿

Y

维度按

2

次幂缩小

,

幅度由释放鼠标按键的位置与起点的距离决定。执行缩放

时

,

起始鼠标位置的

Y

值保持静止。

• 沿

Y

轴缩放范围

(Zoom Y Range)

:

绘制垂直幕布

,

以指定松开鼠标时要显示的

Y

范围。

• 沿

Y

轴放大

(Zoom in Y)

:

沿

Y

维度按

2

次幂放大

,

幅度由释放鼠标按键的位置与起点的距离决定。

执行缩放时

,

起始鼠标位置的

Y

值保持静止。

• 沿

Y

轴复位缩放

(Reset Zoom Y)

:

将

Y

范围复位至波形窗口中当前显示的值对应的

Y

范围

,

并将

Y

范围模式设置

为“自动

(Auto)

”。

Y

维度的所有缩放手势都可设置

Y

范围模拟设置。“

Reset Zoom Y

”可将“

Y Range

”设置为“

Auto

”

,

其它手势可将

“

Y Range

”设置为“固定

(Fixed)

”。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/628535

推荐阅读

相关标签