- 1大模型八股文_glm num_beams

- 2Vue 3.2+Vite2 + Element-Plus 开发的后台管理系统(后台模板)_vue3 + javascript + elementplus后台框架教程

- 3前端开发必须要会的:macos启动一个本地web服务器访问本地html文件并在手机上访问html文件_python前端 macos

- 4raid5坏了一块盘怎么办_机械硬盘的坏道处理——屏蔽之

- 5“GPG 错误导致没有公钥,无法验证签名”的问题解决_由于没有公钥,无法验证下列签名: no_pubkey f42ed6fbab17c654

- 6js伪随机数,每次运行都产生相同的随机数_js math.seed

- 7webassembly003 MINISIT mnist/convert-h5-to-ggml.py

- 82024最强版软件测试面试攻略,助你直通大厂!

- 9对称二叉树_如果二叉树的左右子树的结构是对称的,即两棵子树皆为空,或者皆不空,则称该二叉树

- 10matlab 求解目标规划的序贯算法_matlab 求解目标规划的序贯式算法

ZYNQ7045从flash启动linux vivado配置

赞

踩

ZYNQ7045从flash启动linux vivado配置

准备工作

VIVADO(文中使用的版本为vivado 2018.3)、xilinx sdk

- 1

hdf配置流程

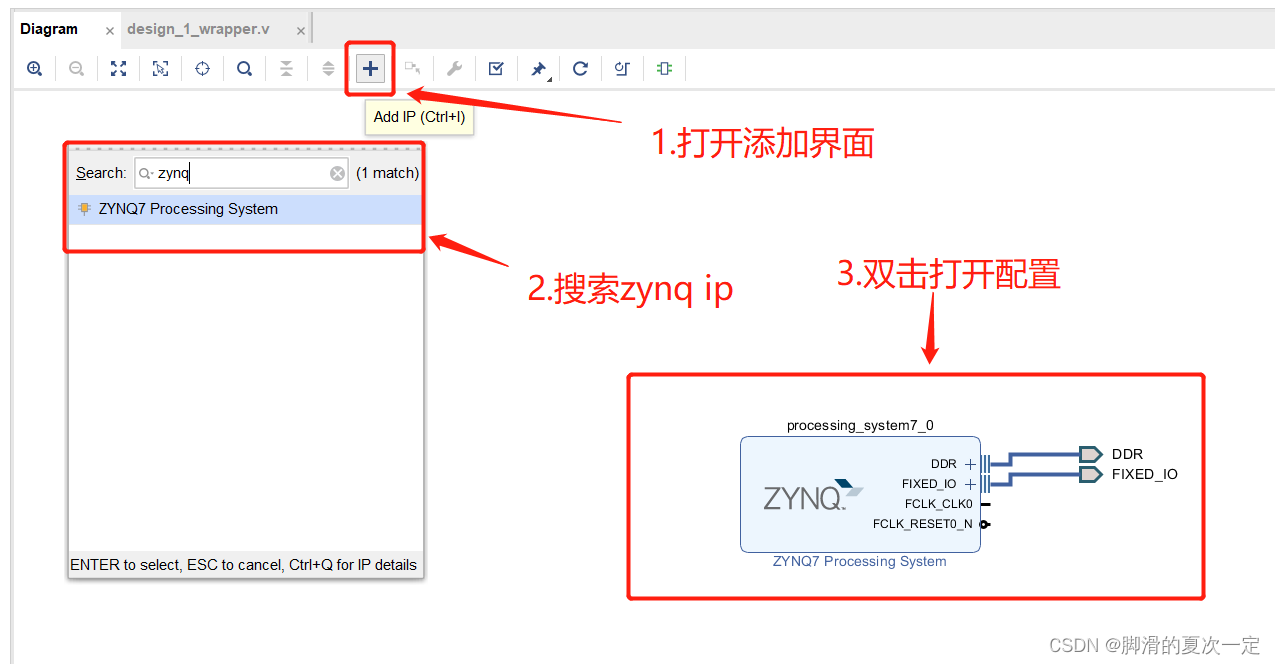

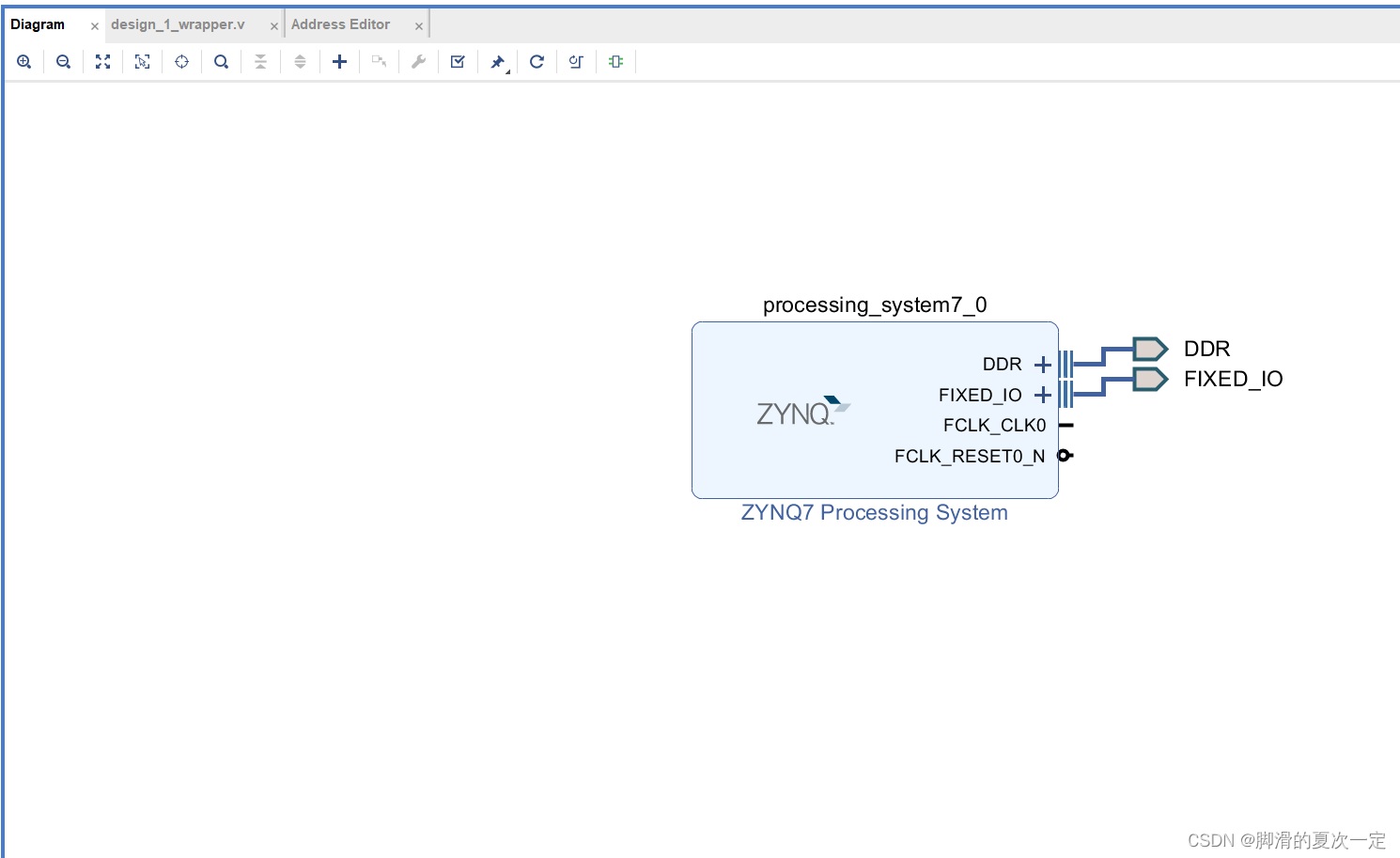

创建Block Design,添加ZYNQ ip

配置相关参数

双击打开上图中"processing_system7_0",配置相关参数:

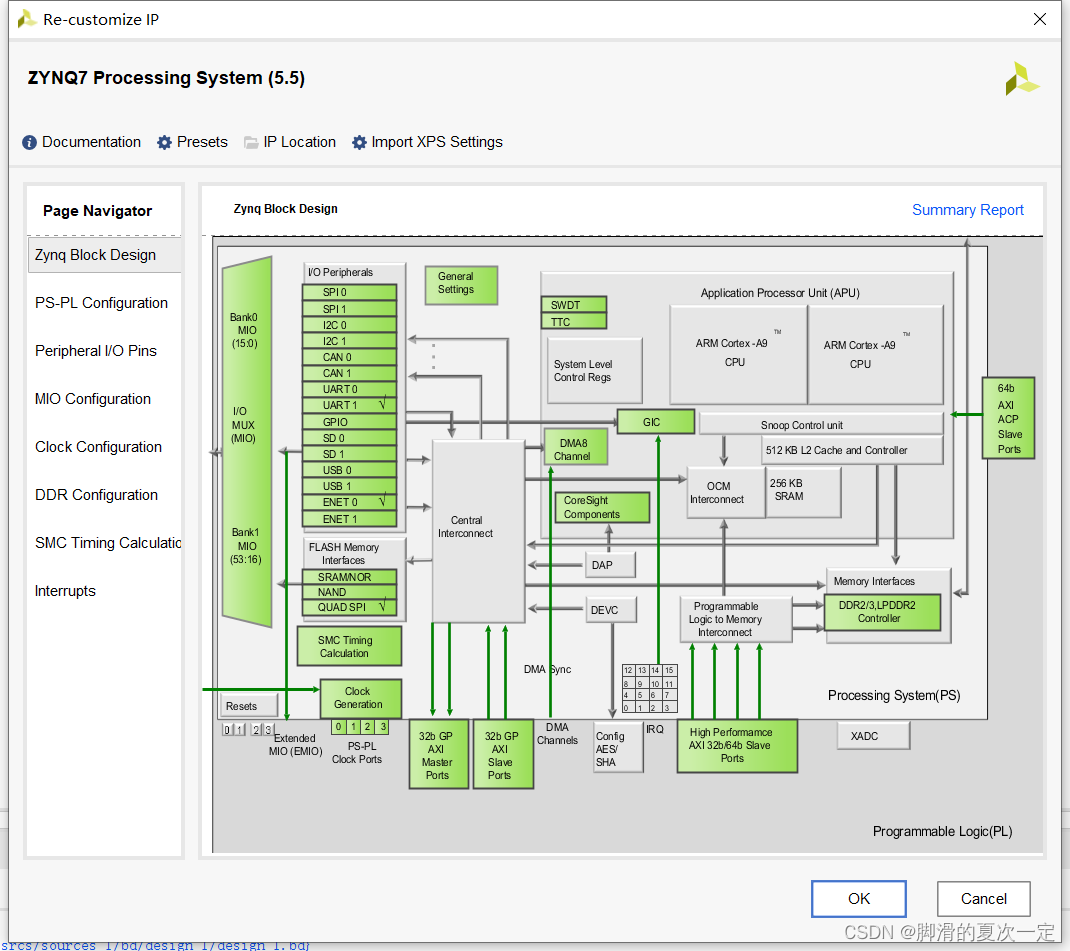

首先显示的是ZYNQ硬核架构,可看到ZYNQ所拥有的外设,绿色部分为可配置模块,可点击进入相应配置界面,初次使用可参考ug585文档,里面会对ZYNQ有详细的介绍。

本文仅针对PS端linux启动做配置,不涉及其余PL端功能配置:

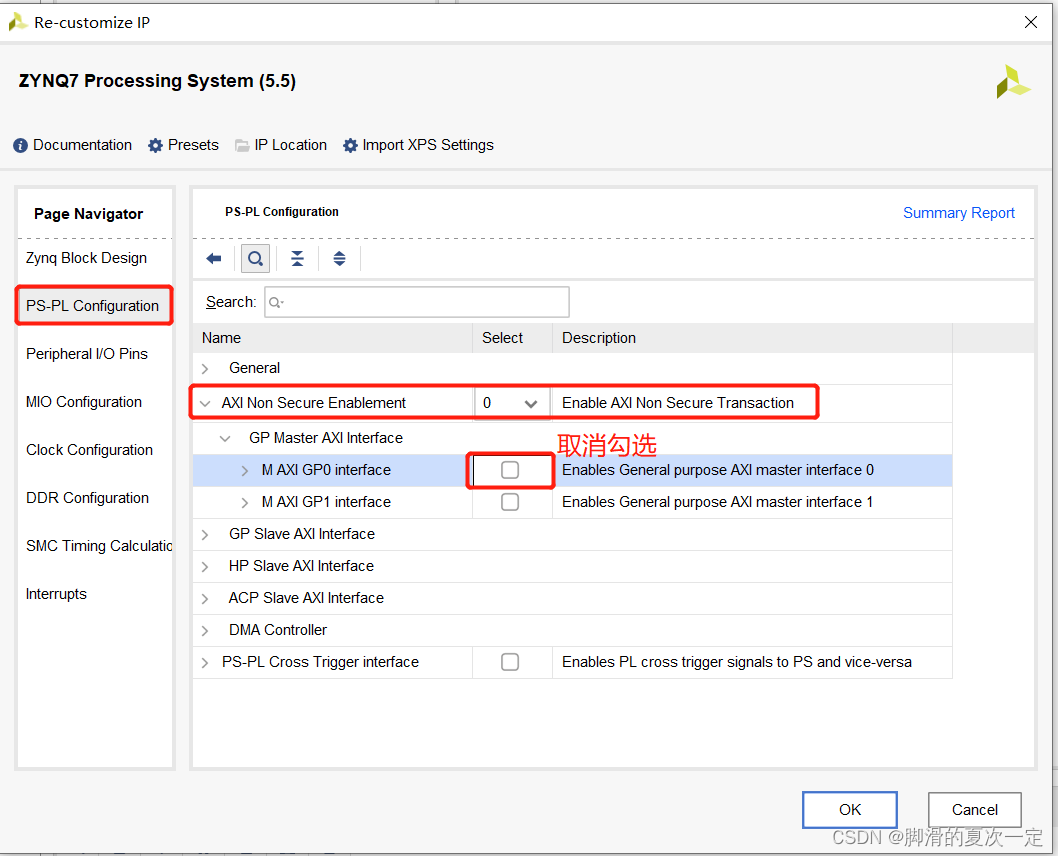

1、首先取消 M AXI GPx interface 接口选择

PS-PL Configuration 界面主要是进行PS与PL之间接口的配置,主要是AXI接口。

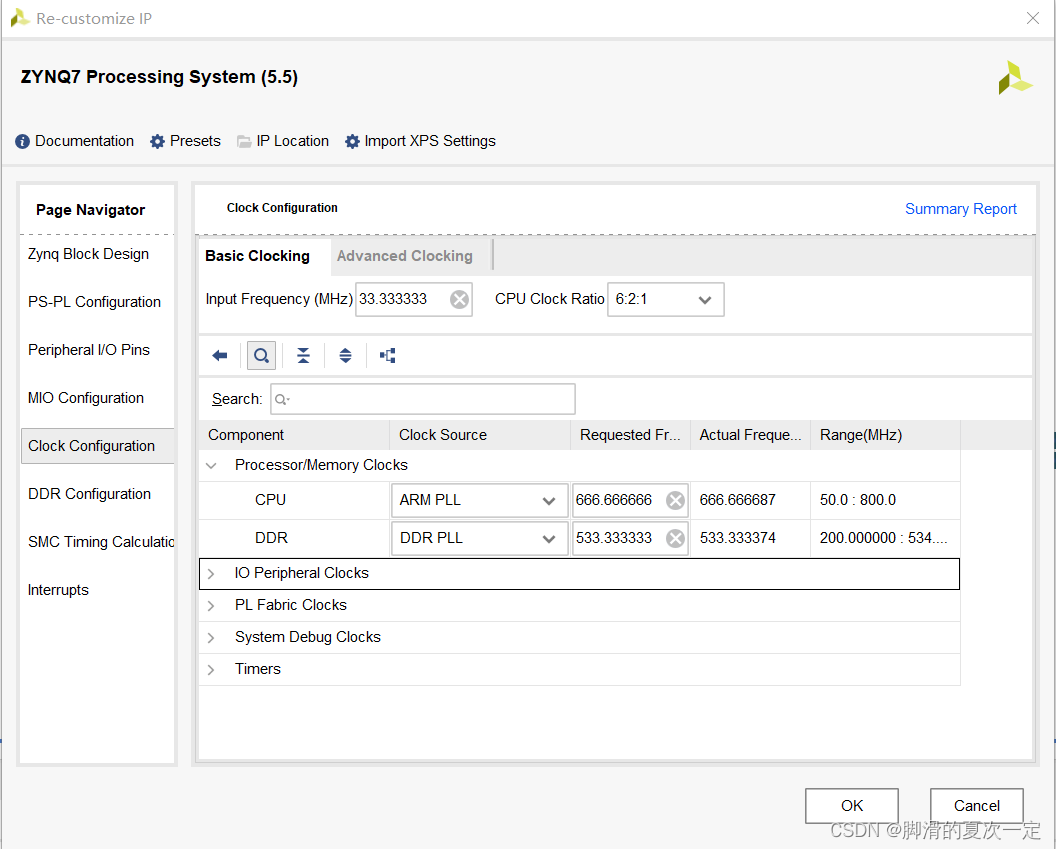

2、依据原理图对时钟进行配置

在“Clock Configuration”选项卡中,依据原理图中提供的时钟和外设所需时钟,对时钟进行配置

本文中配置与默认配置契合,所以不进行修改。

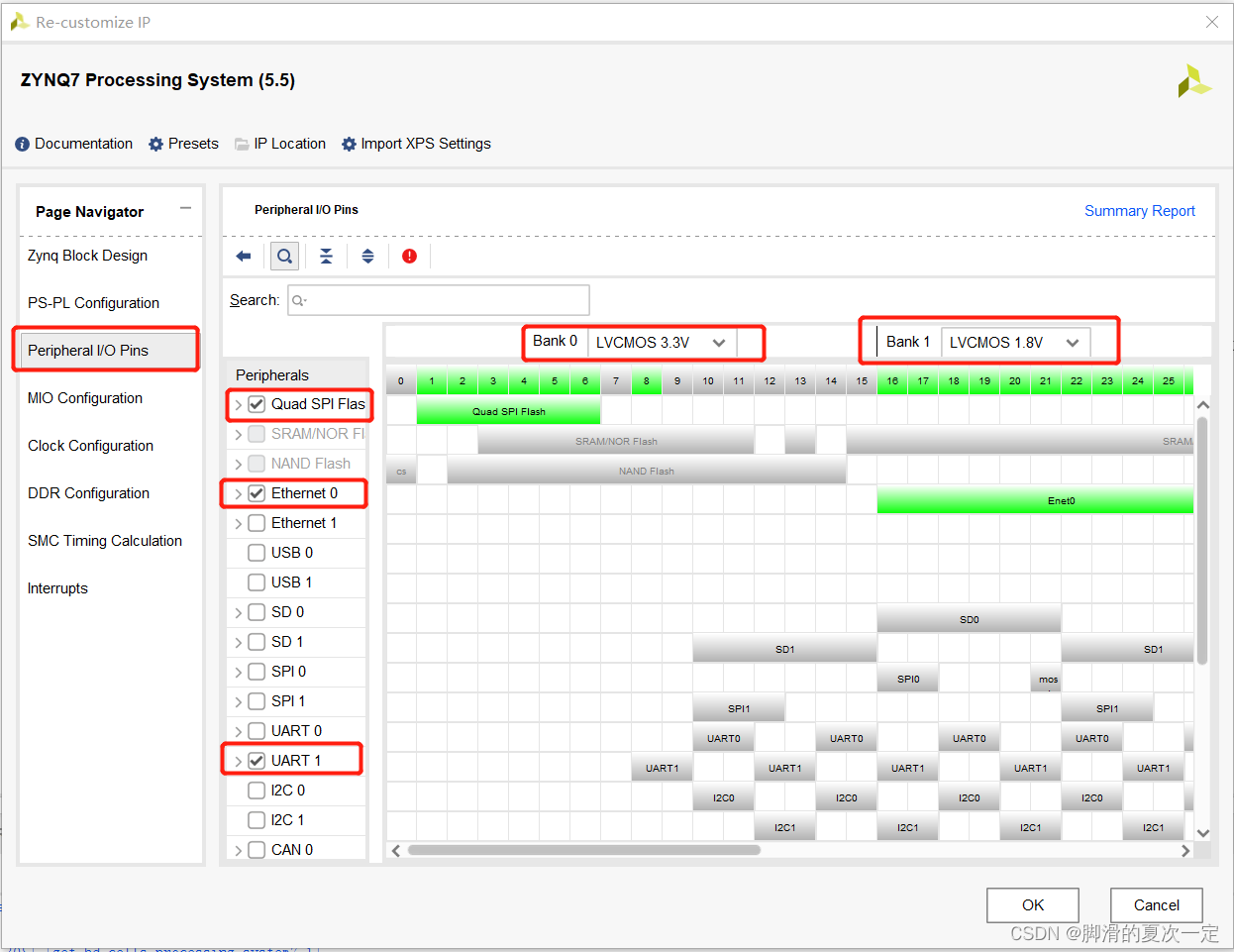

3、对外设进行配置

依据硬件原理图和所使用到的外设,对ZYNQ硬核进行外设配置,注意原理图中对与bank的电平标准配置。本文使用的是通过QSPI flash方式启动ZYNQ所以按照原理图中flash型号对flash类型进行选择;本文只用到串口和以太网两个外设接口,所以依据原理图只需配置Eth0和UART1两种外设即可。

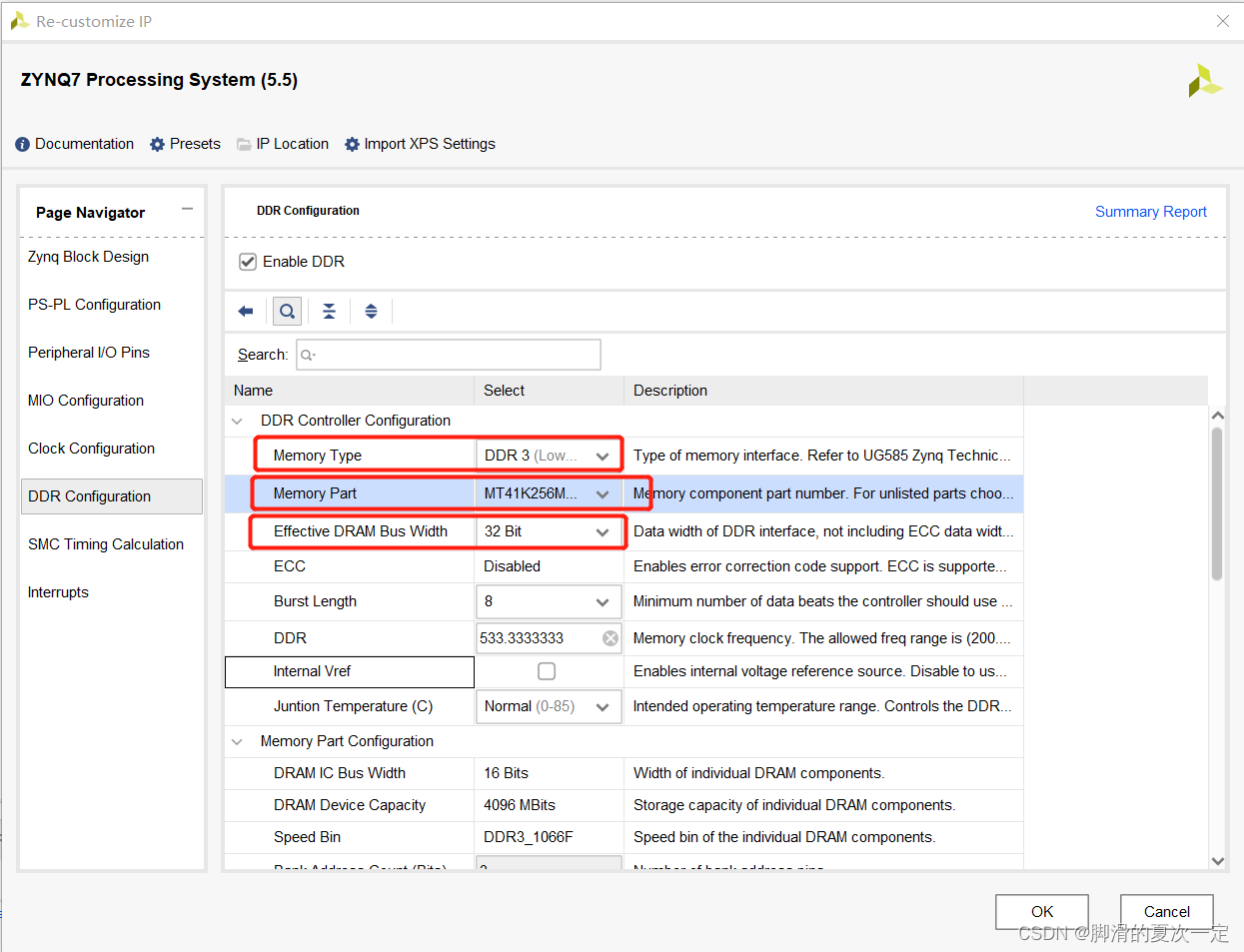

4、对DDR进行配置

DDR的配置是必须的,因为ZYNQ的启动必须借助DDR,在此处DDR的作用就像PC中内存条的作用。依据原理图DDR的型号对配置DDR的参数,若Memory part选项中无相匹配的DDR型号,可选择型号相近的即可(关键信息必须一致),此外更推荐通过DDR的用户手册自定义DDR的参数配置(Memory part选项中Custom选项即为自定义配置)

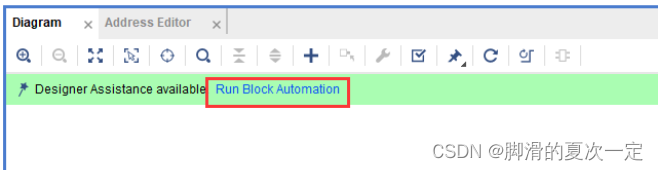

点击OK,其余选项保持默认,ZYNQ核配置结束。点击Run Block Automation,VIVADO会自动完成端口导出工作。

之后流程保持默认点击OK。

至此为止,本项目中所需要的环境已经配置结束。接下来生成bit流文件和所以要的HDL文件

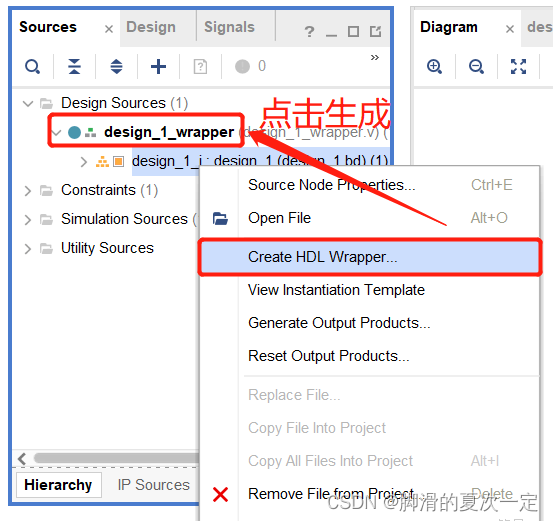

所需文件生成

1、选择 Block 设计,右键“Create HDL Wrapper…”,创建一个 Verilog 文件,为 block design生成 HDL 顶层文件。点击后提示框选项保持默认。

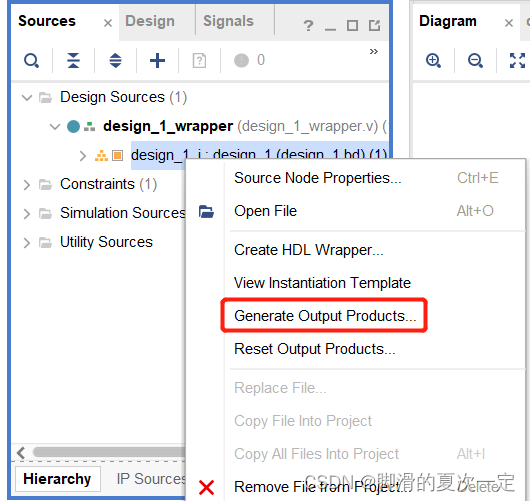

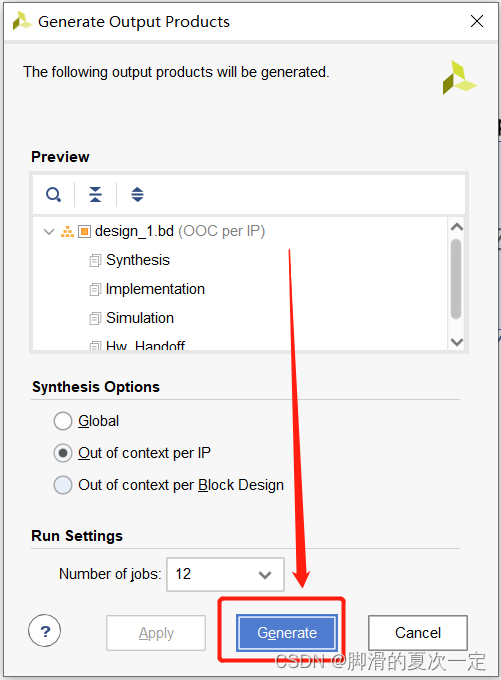

2、选择 block 设计,右键“Generate Output Products”,此步骤会生成 block 的输出文件,包括 IP,例化模板, RTL 源文件, XDC 约束,第三方综合源文件等等。供后续操作使用。

点击Generate,生成。

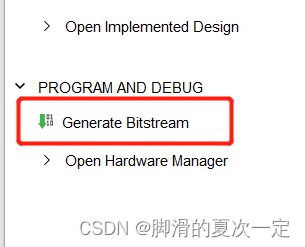

3、点击左选项卡中 Generate Bitstream 生成BIT流文件

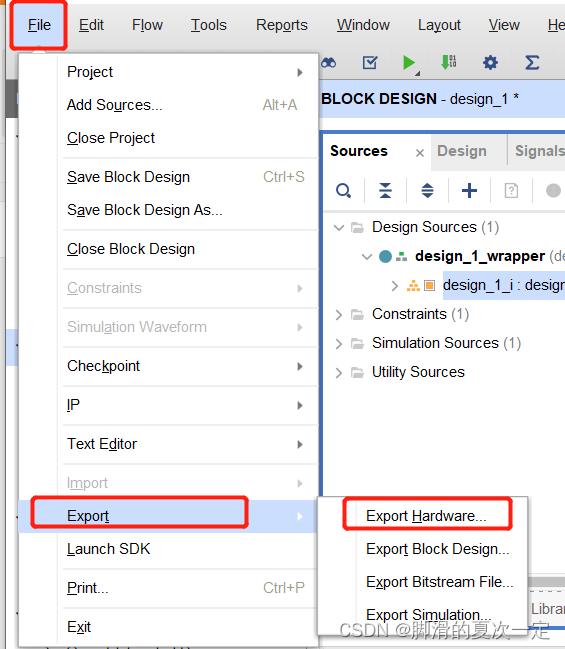

4、点击菜单栏File -> Export -> Export Hardware… 到处硬件配置信息

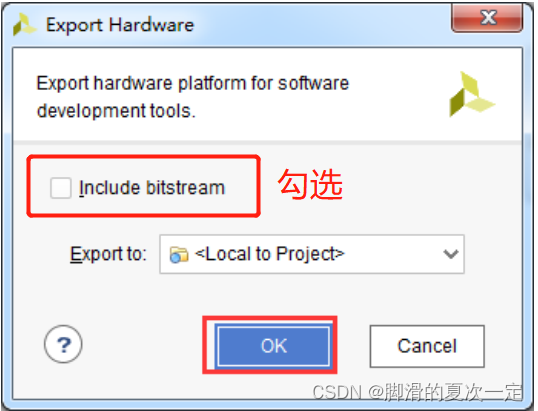

在弹出的对话框中勾选 Include bitstream ,点击ok完成生成

到此vivado中的配置已经结束,接下来打开SDK生成fsbl

打开SDK

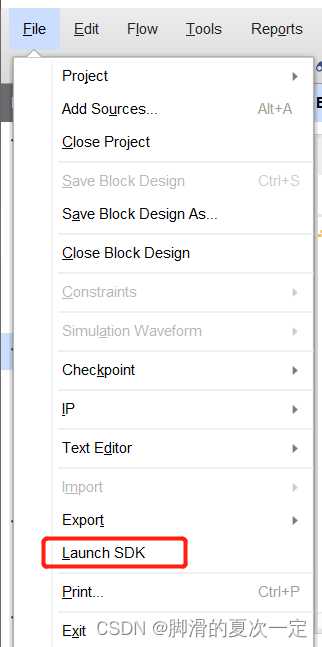

点击Launck SDK打开sdk

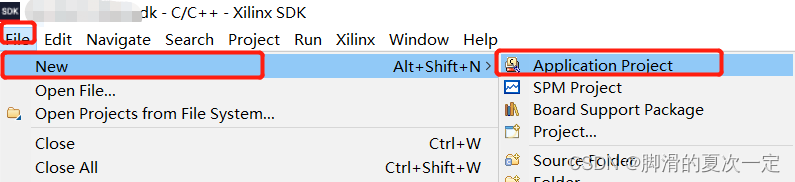

点击File -> New -> Application Project 建立一个新的APP工程

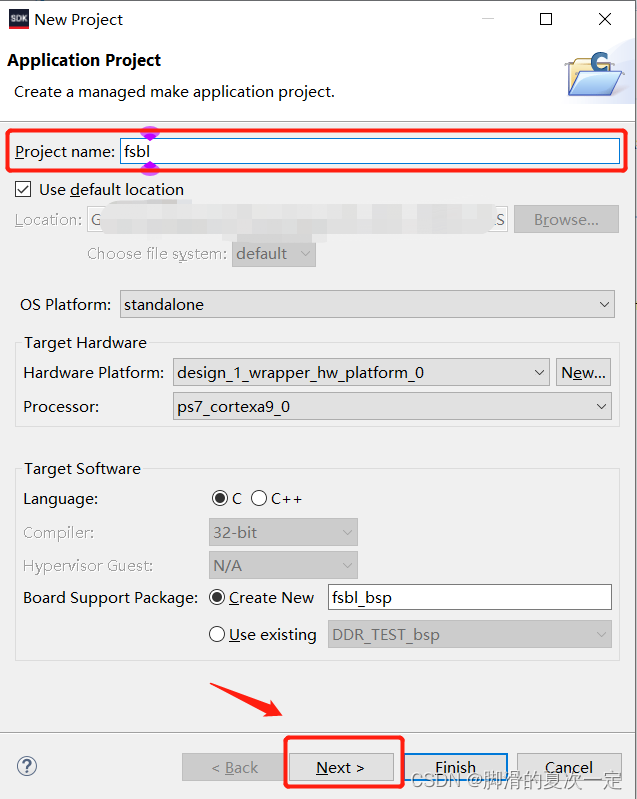

Project name :填写为fsbl -> 点击 next

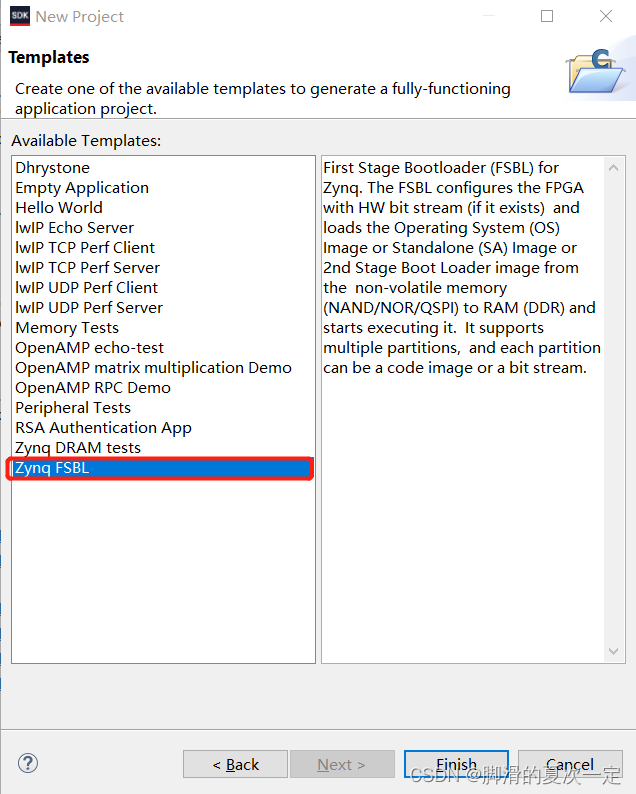

选择Zynq FSBL 点击Finish 完成配置

到此所有的配置都已完成,为以防万一,关闭所有相关应用,找到工程所在目录选择 xxxxxxx.sdk文件夹交由软件工程师,工作结束!