- 1如何去掉流氓网站http://www.2345.com/?177

- 2关于tomcat不能启动的问题(NB:JAVA_HOME should point to a JDK not a JRE)

- 3JAVA面试题28

- 4einj 注入内存ue/ce故障_内存uce错误是什么意思

- 5详解Python中sys模块的功能与应用

- 6第10章Tcl脚本编程(一)

- 7【私有云盘】搭建PHP轻量文件管理器 - TinyFileManager「公网远程访问」_php 文件管理系统

- 8ps -ef | grep 命令详解

- 9protobuf安装步骤---ubuntu_ubuntu安装protobuf

- 10【最新版】Python全网最全、蕞详细的库都这里了,需要的赶紧码住!_python函数库

ARMv8-AArch64 的异常处理模型详解之异常处理概述Handling exceptions

赞

踩

一,异常处理相关概念

在介绍异常处理之前,有必要了解一些关于异常处理状态的术语:

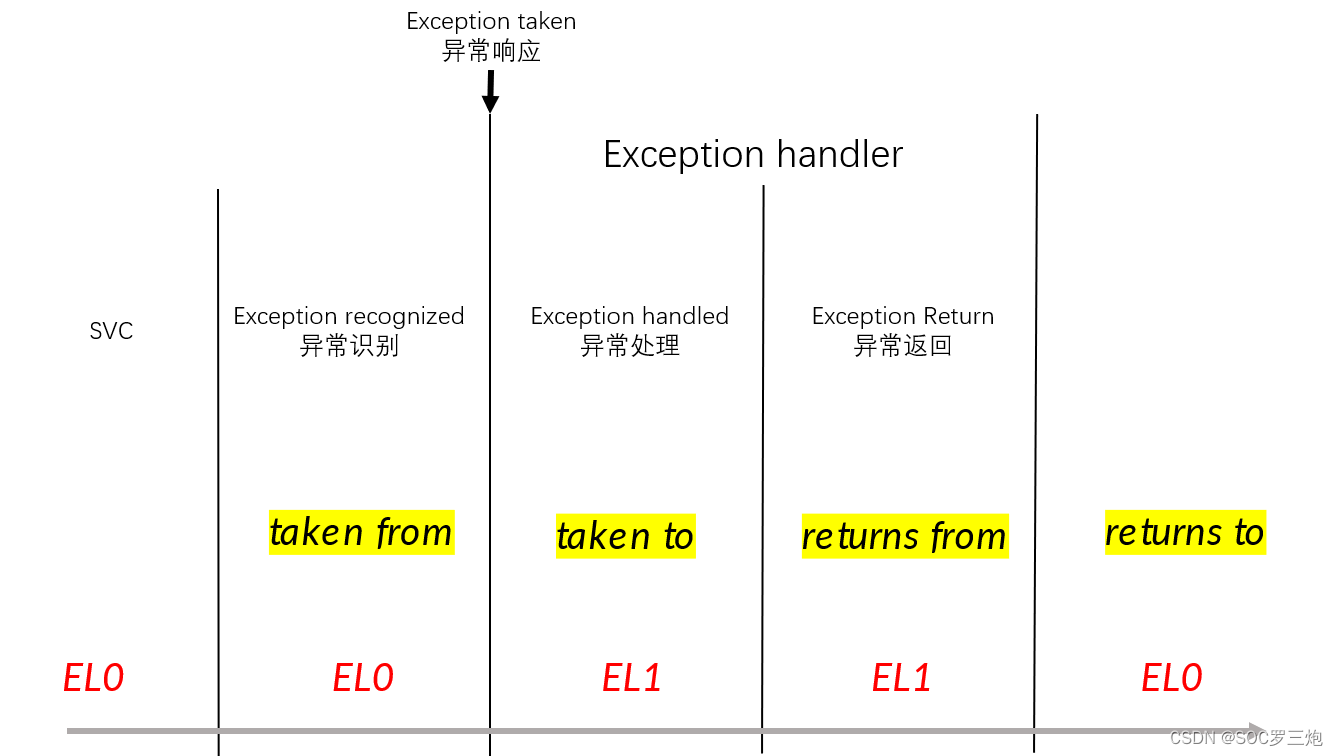

- 当处理器响应一个异常时,我们称该异常被获取了( taken )。

- 处理器响应异常之前的状态被称为 taken from。

- 处理器响应异常之后的状态被称为 taken to。

因此,当处理器识别到异常时,此时处理器处于 taken from。在异常之后的状态称为 taken to。

当异常处理完成后,处理器需要返回到异常发生前的状态,这个过程称为 exception return。并且在ARM架构中有专门的指令用于异常返回(ERET):

- 处理器在执行异常返回指令之前的状态,称为 returns from。

- 处理器在执行异常返回指令之后的状态,称为 retruns to。

如下图所示,为处理器异常状态转换 : EL0 -> EL1-> EL0的全过程:

- 先执行 SVC指令,从EL0切换到 EL1,这个过程也称为 taken a exception from EL0 to EL1.

- 在 EL1的exception handler里处理完异常。

- 处理完异常后执行 ERET(exception retrun)指令,从EL1返回到 EL0.此过程也称为 return a exception from EL1 to EL0.

二,异常处理概述

当异常发生时,处理器会先保存处理器当前的状态(CPSR,也称为PSTATE)以及异常返回地址。然后进入一个特殊的状态来处理改异常。

当前处理器的状态信息来自于PSTATE寄存器,也就是CPSR,处理器会将异常发生前的PSTATE的值写入到SPSR(Saved Program Status Register)中。而异常返回的地址,将会写入到异常链接寄存器ELR(Exception Link Register)。

此外,对于同步异常以及SError异常,处理器还会更新异常综合寄存器ESR(Exception Syndrome Register),该寄存器记录了异常产生的原因。

总结如下,当异常发生并进入一个AArch64的异常等级(ELx)时,处理器会有如下操作:

- 在异常被处理前的PSTATE寄存器的内容会被写入到SPSR_ELx寄存器中。

- 异常返回地址会被写入到ELR_ELx寄存器中。

此外:

- 对于同步异常和SError异常,异常发生的原因也会被记录到ESR_ELx寄存器中。

- 对于地址相关的同步异常,比如MMU错误,导致异常发生的虚拟地址也会被写入到错误地址寄存器(Fault Address Register,FAR_ELx)中。

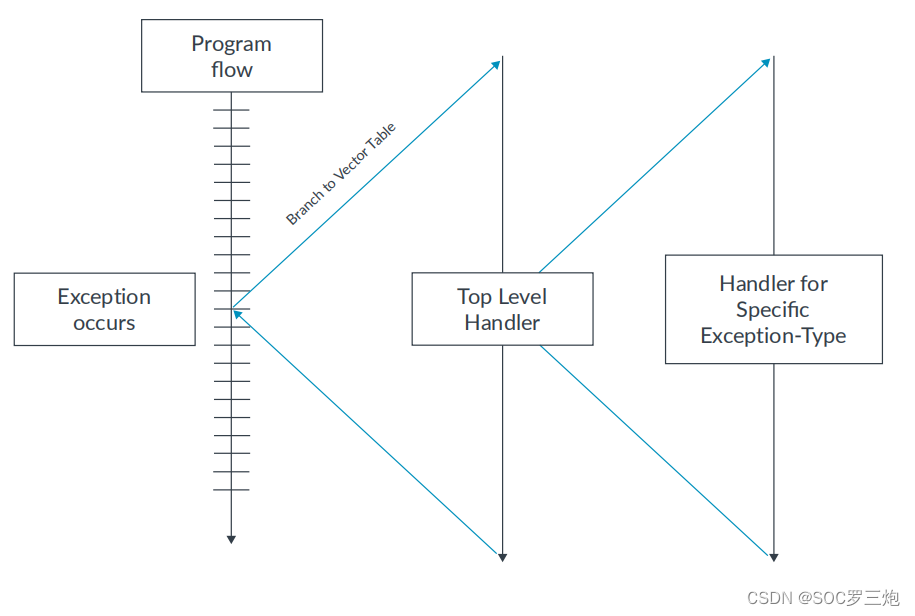

对任何给定异常的异常处理都从一个称为异常向量(exception vector)的固定内存地址开始,当异常发生时,处理器将会跳转到异常向量表的某个地方。

AArch64中的向量表与许多其他处理器体系结构不同,因为它们包含指令,而不是地址。每个条目最多包含32条指令;刚好足以执行基本堆叠和调用特定于异常的处理代码。

向量表的位置通常被配置为异常处理程序代码,以执行通用操作,并根据异常类型跳转到进一步的异常处理代码,如下图所示的top level 处理函数。这个top level向量代码被限制为32个字(word)大小。异常处理程序包含处理请求操作的代码,并可以从异常状态返回。

当一个异常被识别时,它同时也对应着一个异常等级EL,因此在处理异常的过程中,可以路由到一个不同的EL中。这也是处理器提高特权的唯一方法:通过异常等级切换,从低的异常等级切换到高的异常等级。同理,处理器若是想降低特权,惟一的方法就是通过异常返回,这意味着:

- 当异常发生时,处理器的EL可以不变,或者提高。

- 当异常返回时,处理器的EL可以不变,或者降低。

异常的目标异常等级可以和当前的异常等级保持一致,目标异常等级可以根据异常类型或者系统寄存器的配置bit隐式地指定。

需要注意的是,对于AArch64的EL0,我们只能产生异常从EL0切换到更高等级的异常,绝对不能通过产生异常的方式进入EL0,因此,异常向量表里也没有关于EL0的向量。

在之前的文章中 ARMv8-AArch64 的异常处理模型详解之异常等级、执行状态以及安全状态我们提到过,处理器要想切换执行状态,只有两种方法:

- reset

- 异常等级切换或者返回。

在AArch32和AArch64之间的交互被称为 interprocessing。关于执行状态的改变,有如下规则需要牢记:

- 当从一个低的EL切换到更高的EL时,处理器的执行状态可以保持不变,或者切换到AArch64。

- 当从一个高的EL切换到更低的EL时,处理器的执行状态可以保持不变,或者切换到AArch32。

这也说明了:

- 如果某个异常等级正在使用AArch32,则比它更低的异常等级必须使用AArch32模式。

- 如果某个异常等级正在使用AArch64,则比它更高的异常等级必须使用AArch64模式。

比如处理器在EL3中正在使用AArch32,则可以推断出此时处理器的EL0、EL1以及EL2也只能使用AArch32,而不能是AArch64。

在ARMv9-A架构和一些ARMv8-A架构中,AArch32状态只在EL0中被支持,并且不能通过产生异常的方式进入EL0。这说明,在这种情况下如果想改变EL0的执行状态,只能使用规则2,从一个更高的异常等级返回到EL0,支持处理器的执行状态可以保持不变(AArch64),或者切换到AArch32。

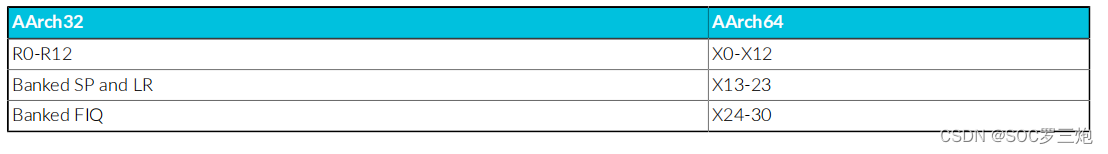

由于可以通过切换异常等级的方式从AArch32进入到AArch64,所有AArch64的异常处理函数可能需要访问AArch32的寄存器,AArch32的通用寄存器是直接映射到AArch64通用寄存器中的,这样AArch64的异常处理函数就可以直接访问AArch32的通用寄存了,映射关系如下:

当从AArch32切换到AArch64时,之前在AArch32状态下无法访问的那些寄存器将会保留它们之前在AArch64状态下的值。对于那些既可以在AArch32和AArch64下访问的寄存器:

- 高32bit:未知,可能为0。

- 低32bit:映射到AArch32寄存器的值。

关于AArch64寄存器的详细描述,可以参考文档: AArch64 Instruction Set Architecture guide.