热门标签

热门文章

- 1基于Java spring boot框架+微信开发者工具+MySQL数据库的高校课外管理系统 计算机毕业设计 微信小程序开发_微信开发者工具用的是什么框架

- 2ROS机器人开发实战代码案例详解:从入门到精通

- 3[毕设记录]@Vscode插件推荐:git graph_vscode git graph

- 4C语言实现简单的哈希表_c语言 哈希表 不用malloc

- 5GAN:对抗生成网络【通俗易懂】

- 6show processlist 命令详解_show processlist;

- 7快速排序-c\c++版、java版、python版、JavaScript版_c, c++, java, python快速排序

- 8Leetcode —— 886. 可能的二分法_力扣题目链接: 886: 可能的二分法

- 9M1安装OpenPLC Editor_openplc editor for windows

- 10【论文笔记】Video Vision Transformer(ViViT)_video vit

当前位置: article > 正文

根据状态转移表实现时序电路

作者:我家自动化 | 2024-04-10 17:20:47

赞

踩

根据状态转移表实现时序电路

描述

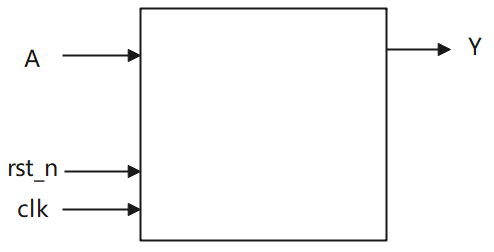

某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

电路的接口如下图所示。

输入描述

- input A ,

- input clk ,

- input rst_n

输出描述

output wire Y 解题分析

本想着用状态机,不过题目要求使用D触发器,差点没想出来。

参考代码

- `timescale 1ns/1ns

- module seq_circuit(

- input A ,

- input clk ,

- input rst_n,

-

- output wire Y

- );

- reg q0, q1;

-

- always@(posedge clk or negedge rst_n) begin

- if(~rst_n) begin

- q1 <= 0;

- end

- else begin

- q1 <= A ^ q0 ^ q1;

- end

- end

-

- always@(posedge clk or negedge rst_n) begin

- if(~rst_n) begin

- q0 <= 0;

- end

- else begin

- q0 <= ~q0;

- end

- end

- assign Y = q0 & q1;

- endmodule

注:解题分析来源于网友,如有侵权,请告删之。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/400035

推荐阅读

相关标签