- 1谈谈响应式布局或移动端适配_响应式布局,移动端适配方案

- 2Vivado简单调试技能_vivado 调试

- 3数据结构之队列(顺序队和链队)(C语言附完整代码)_数据结构队列入队函数代码

- 4运用维纳滤波实现图像去模糊(OpenCV实现)_维纳滤波去模糊

- 5队列的实现(完整代码+详细注释版)【数据结构】_数据结构顺序队列完整代码

- 6python 列表形式字符串 转列表_python eval列表

- 7DevExpress WPF的电子表格组件,让您更快获得Excel体验(二)_wpf操作excel

- 8Vue3_对接腾讯云COS_大文件分片上传和下载

- 9华为OD机试 - 伐木工(Java & JS & Python & C & C++)_od 伐木工

- 10数据结构——队列的实现_数据结构队列代码

数电实验(四)——四位乘法器_四乘四位乘法器的vhdl设计

赞

踩

工程文件:https://download.csdn.net/download/qq_45645521/18839451

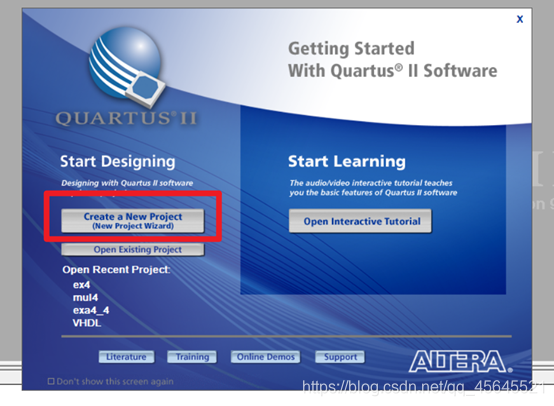

1.打开Quartus,create a new project(笔者用的Quartus是9.1版本)

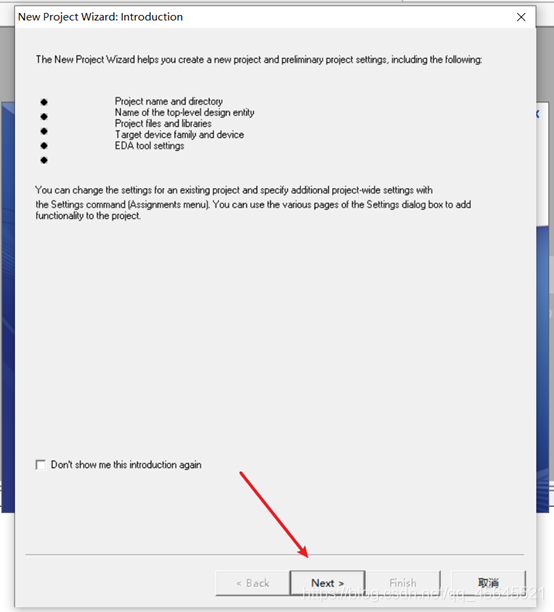

2.点击next:

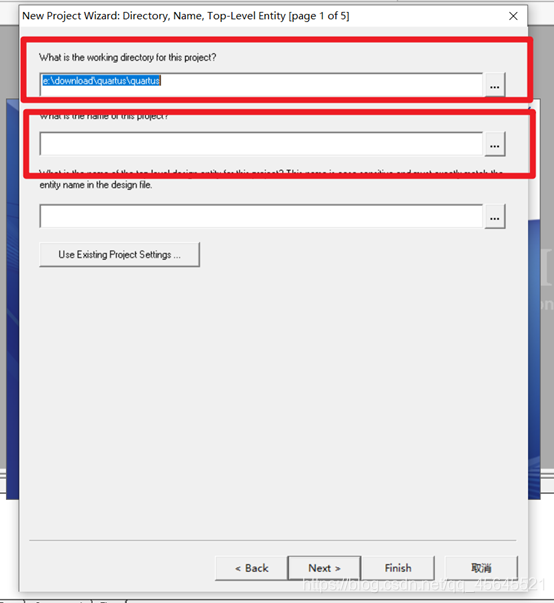

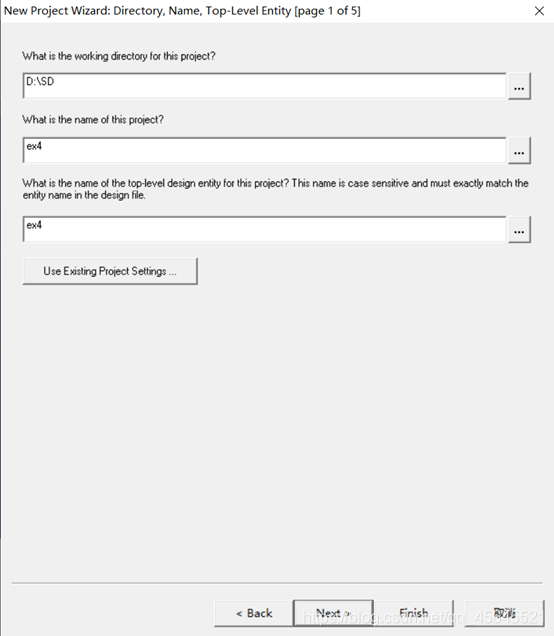

3.更改工作路径以及给Project命名

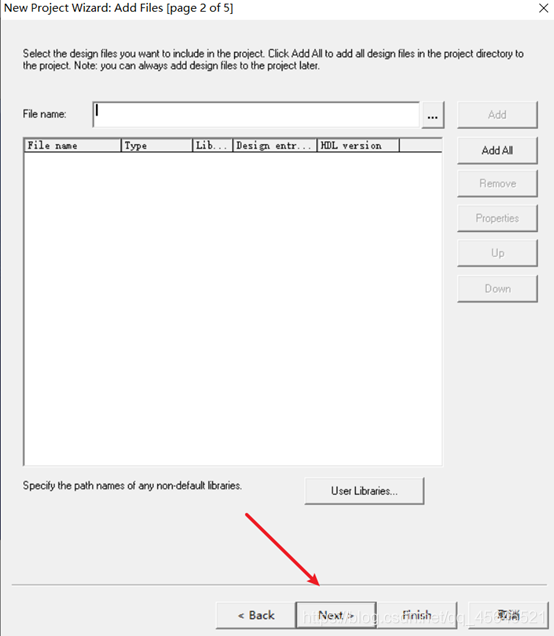

4.点击next

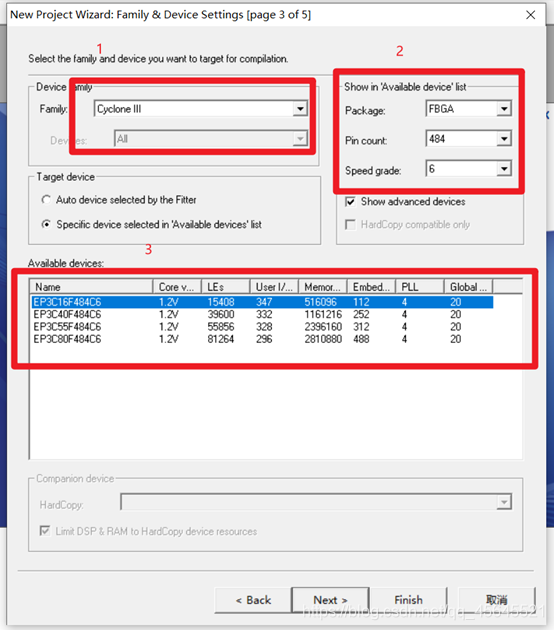

5.配置FPGA相关参数

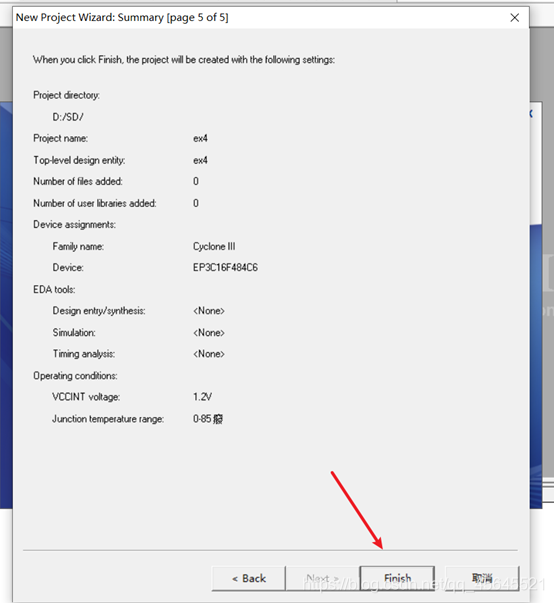

6.一路next,最后finish

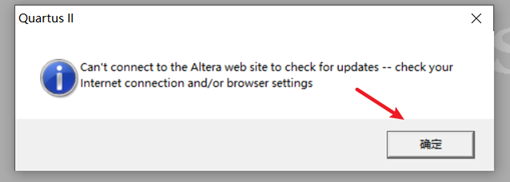

最后可能会有一个弹窗弹出,点击确定就好.

7.最后界面如图:

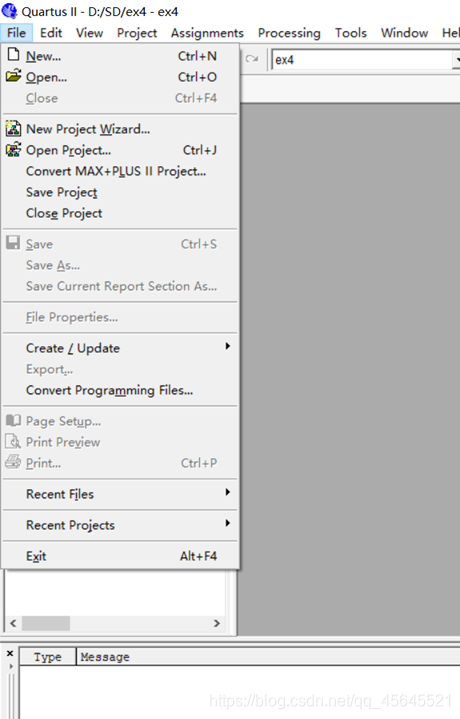

8.新建一个VHDL文件

点击File→new

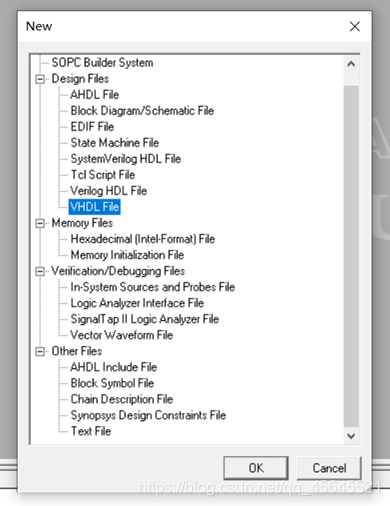

在弹窗中选择,VHDL File,点击OK

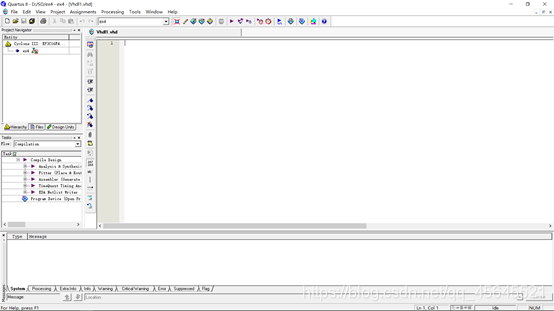

最终界面如图:

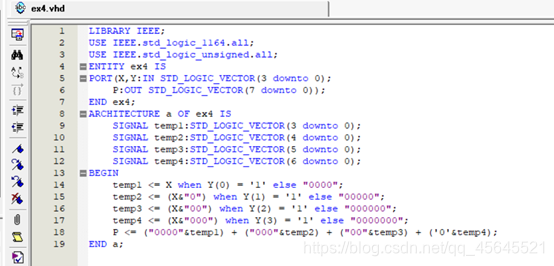

9.编写VHDL程序

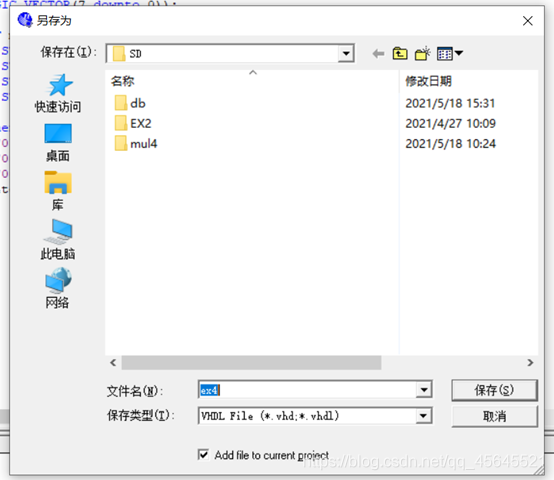

点击Ctrl+S保存

点击保存。

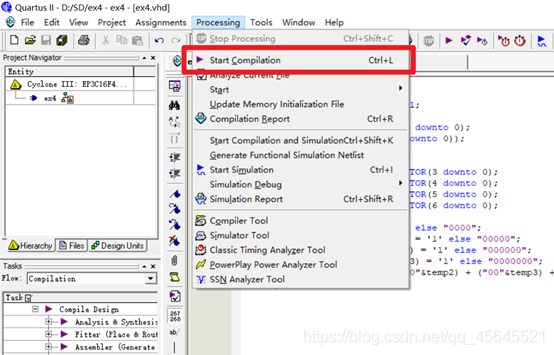

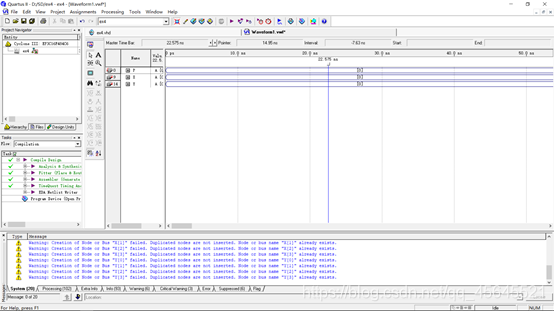

点击Processing中的Start Complilation进行编译。

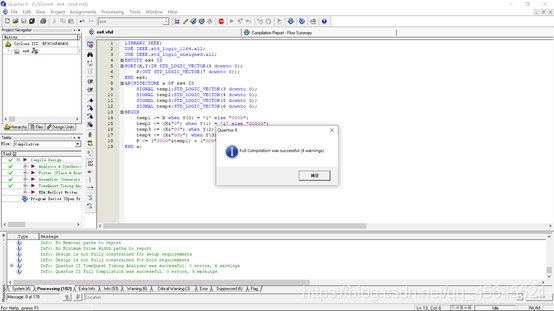

0error 9warnings 可以继续,无需管warning,点击确定

10.进行仿真

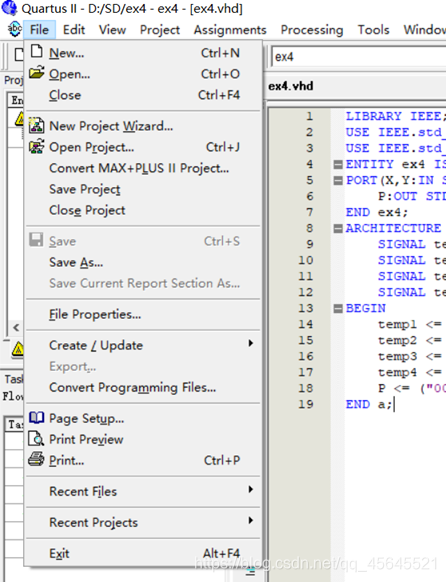

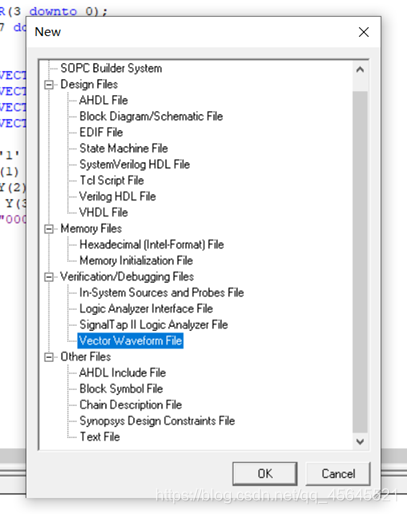

点击file→new

在弹出的窗口中选择Vector Waveform File,点击OK

在弹出的窗口中选择Vector Waveform File,点击OK

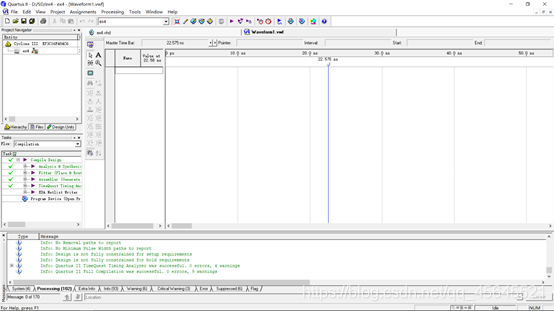

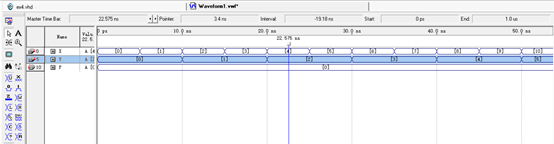

出现如图界面

导入节点

Edit中选择Insert 在下拉菜单中选择Insert Node or Bus

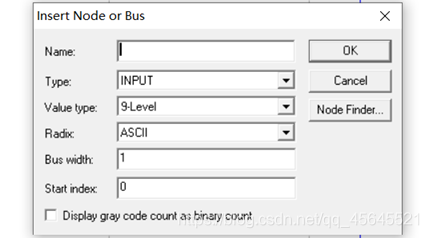

出现如图弹窗

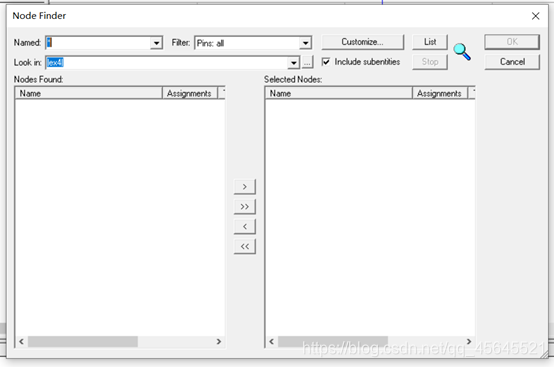

点击Node Finder

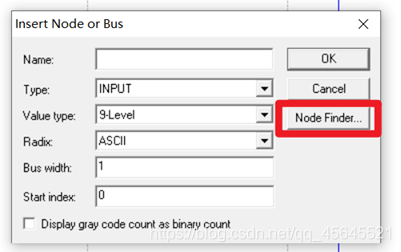

出现如图弹窗

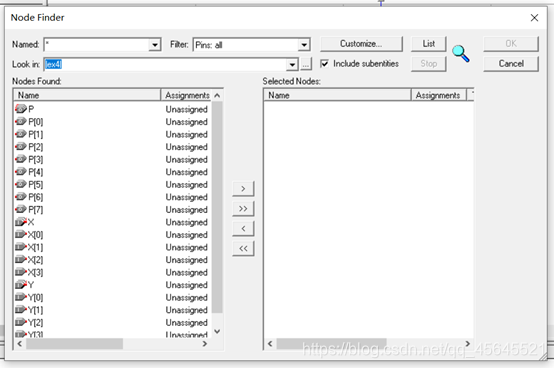

点击list

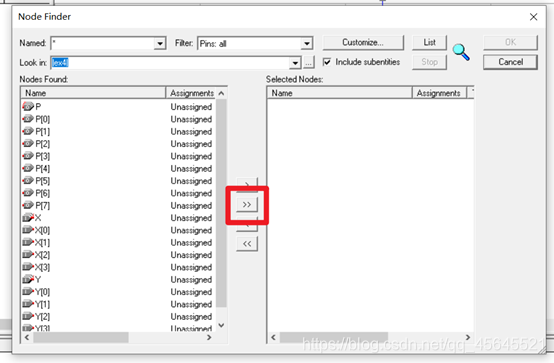

点击 >>

结果如图所示

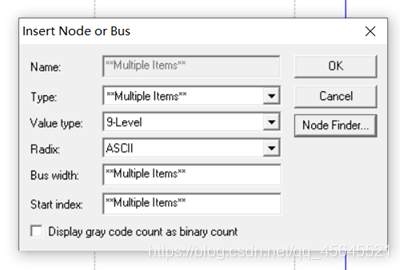

点击OK

点击OK,如图:

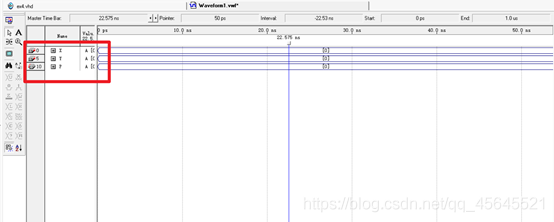

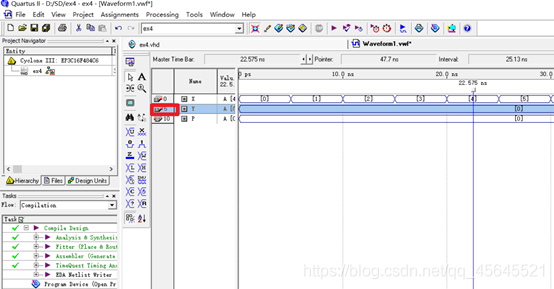

为了方便,拖动X,Y在上面,也可以不拖动,但操作对象要一样

点击如图:

可以看到左侧的蓝色标签,点击如图所圈选标记,

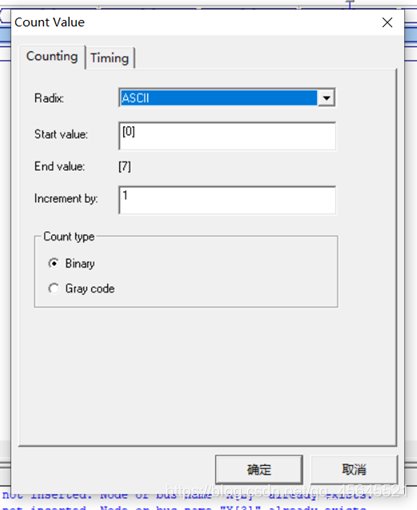

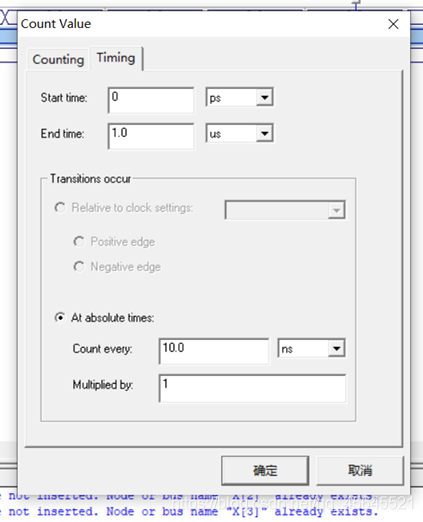

出现如图:

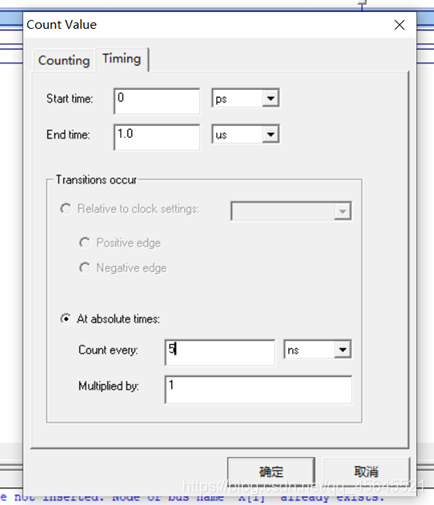

点击timing,将10.0改为5.0

点击确定,出现如图:

同样的,对Y进行操作

同样的,对Y进行操作

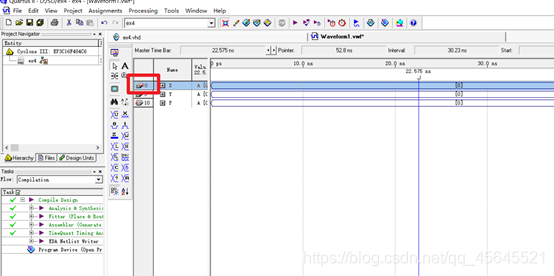

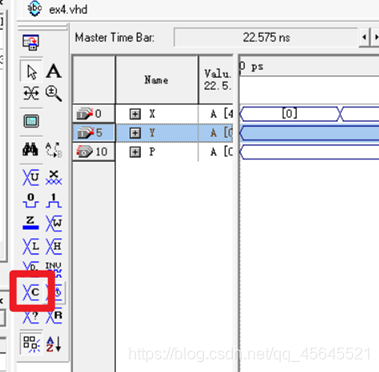

点击如图圈选

需要改变的是点击timing

将5.0改为10.0

点击确定

结果如图:

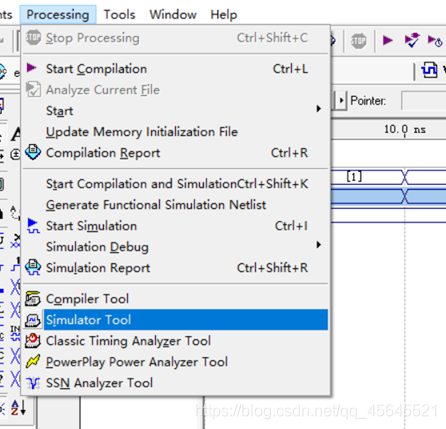

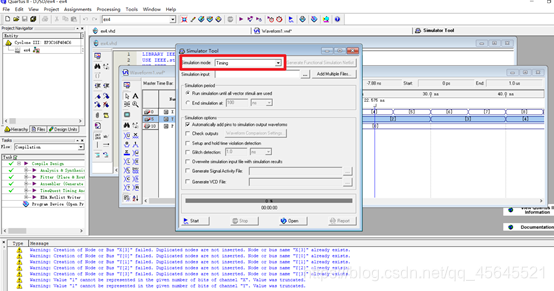

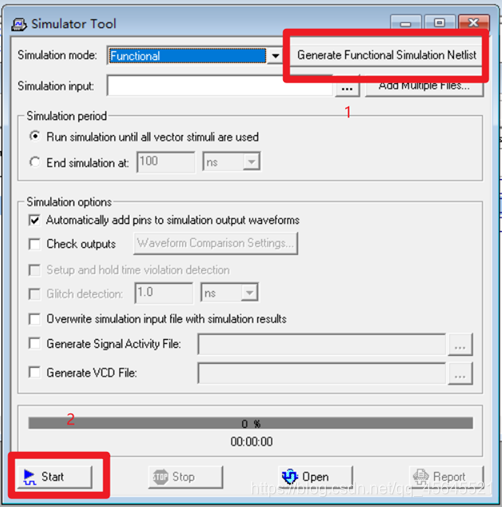

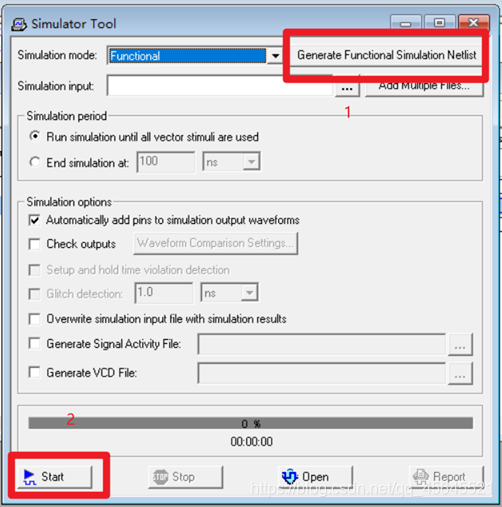

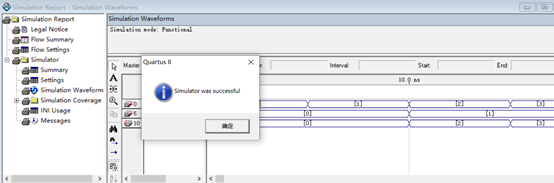

在Processing中找Simulator Tool,点击

出现如图弹窗

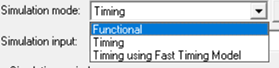

把timing改为:

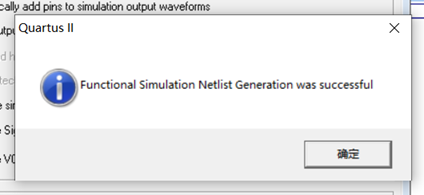

再点击1,

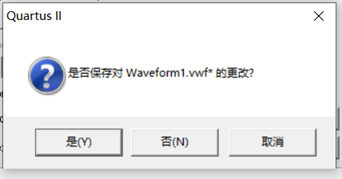

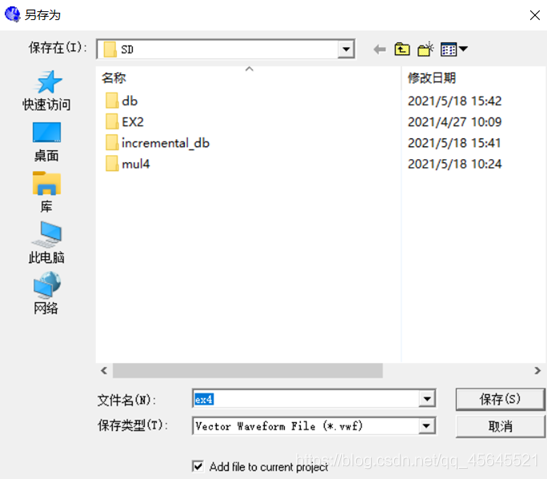

会弹出保存弹窗

全部默认就好

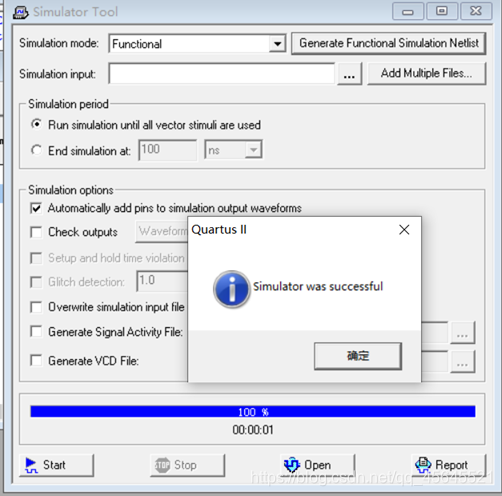

点击确定后,再点击2 start

点击确定

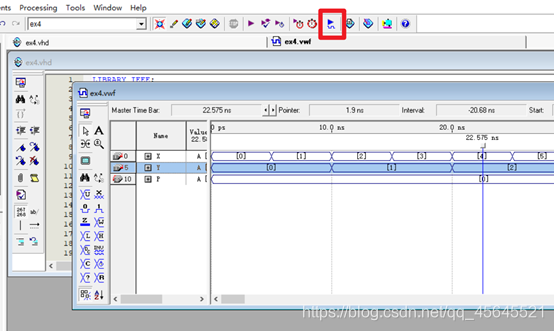

点击如图所示的按钮

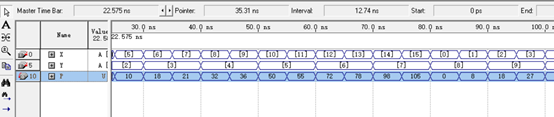

仿真成功!

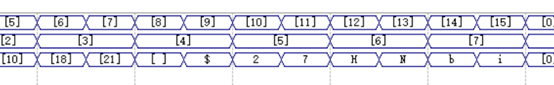

需要注意的是,有些数显示不全

这是编码格式的问题

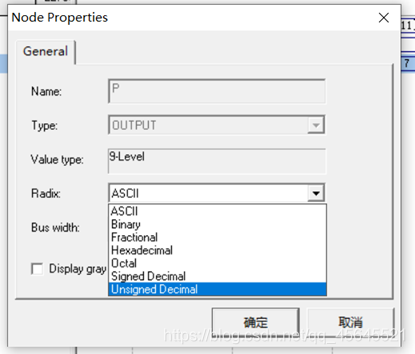

右击P,选择Properties

选择Unsigned Decimal,点击确定

则所有数显示完全

实验完毕

原创不易,欢迎支持!