- 1Xinhui学习NLP的笔记本:基于注意力机制的机器翻译

- 2发布 AI 后,苹果股价创历史新高

- 3详解Java中设计模式28种方式_java设计模式

- 4探索 Tauri:打造高效、安全的桌面应用程序的新框架

- 5苹果 testflight上架讲解_testflight 上架教程

- 6低代码平台及模块化开发对于前端程序员的影响-个人见解_低代码平台 对程序员的影响

- 7Fiddler入门:下载、安装、配置、抓包、customize rules_fiddler安装包

- 8GienTech品牌亮相香港金融科技周,“源启”人气高涨

- 9SSL_ERROR_SYSCALL in connection to github.com:443

- 10猫狗分类——yolo模型_猫狗分类模型

STM32F4以太网 (ETH)之精简介质独立接口:RMII_rmii接口

赞

踩

目录

概述

本文主要介绍STM32F4以太网 (ETH)之精简介质独立接口:RMII的相关内容,包括接口特性,收发数据的时序,以及典型的硬件应用电路。

1 以太网简介

1.1 介绍

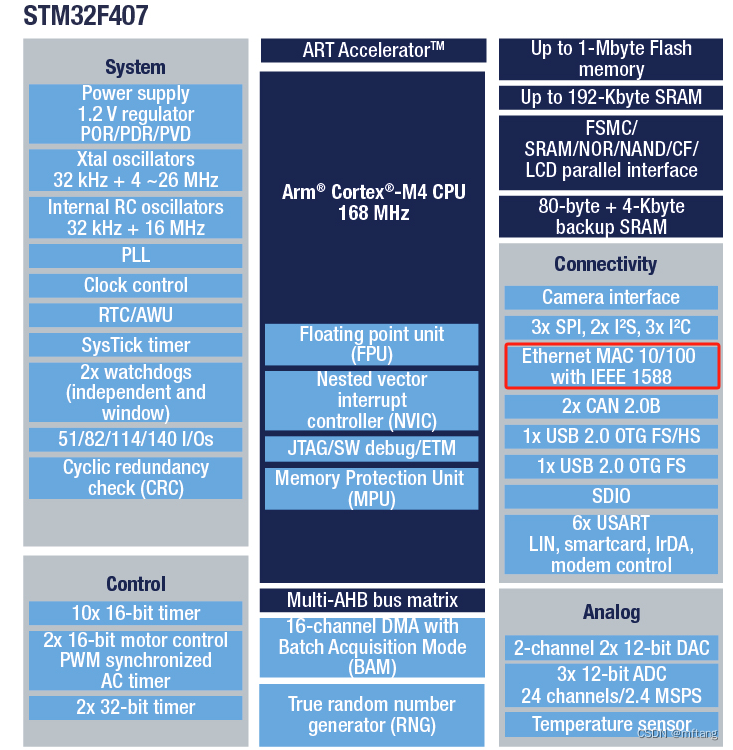

STM32F4xx 可以通过以太网按照 IEEE 802.3-2002 标准发送和接收数据。以太网提供了可配置、灵活的外设,用以满足客户的各种应用需求。它支持与外部物理层(PHY) 相连的两个工业标准接口:默认情况下使用的介质独立接口 (MII)(在 IEEE 802.3规范中定义)和简化介质独立接口 (RMII)。它有多种应用领域,例如交换机、网络接口卡等。

以太网遵守以下标准:

● IEEE 802.3-2002,用于以太网 MAC

● IEEE 1588-2008 标准,用于规定联网时钟同步的精度。

● AMBA 2.0,用于 AHB 主/从端口

● RMII 联盟的 RMII 规范

1.2 特征

MAC 内核特性

● 支持外部 PHY 接口实现 10/100 Mbit/s 数据传输速率

● 通过符合 IEEE 802.3 的 MII 接口与外部快速以太网 PHY 进行通信

● 支持全双工和半双工操作

● 可逐帧控制 CRC 和 pad 自动生成

● 接收帧时可自动去除 pad/CRC

● 可编程帧长度,支持高达 16 KB 的巨型帧

● 可编程帧间隔( 40-96 位时间,以 8 为步长)

2 以太网功能说明: RMII

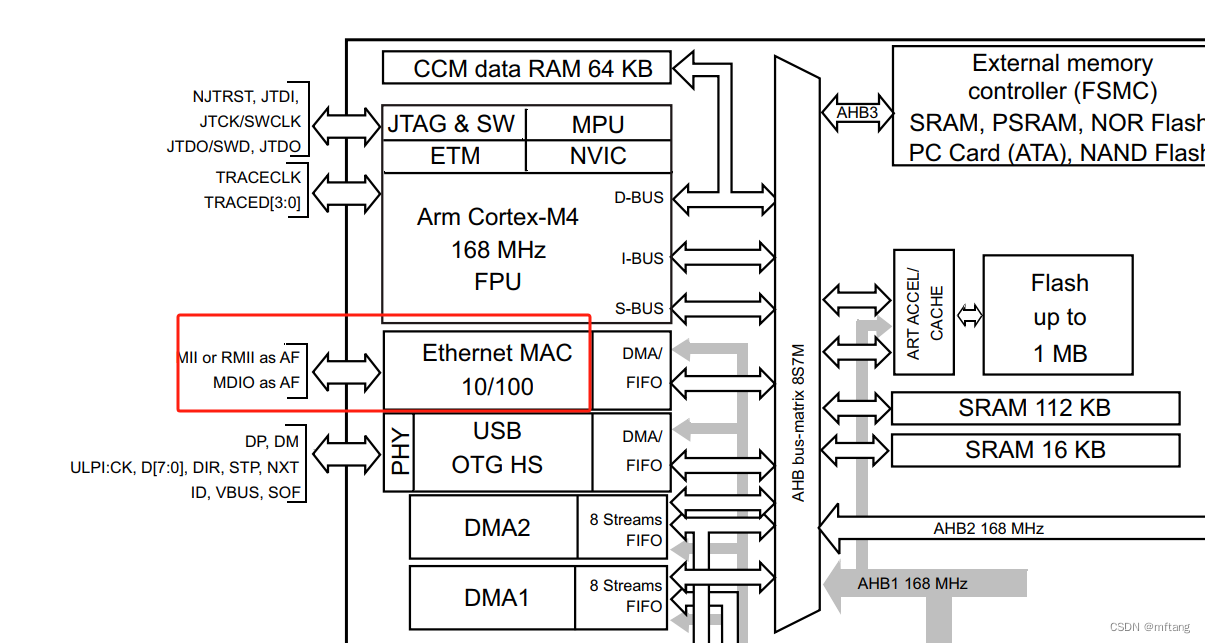

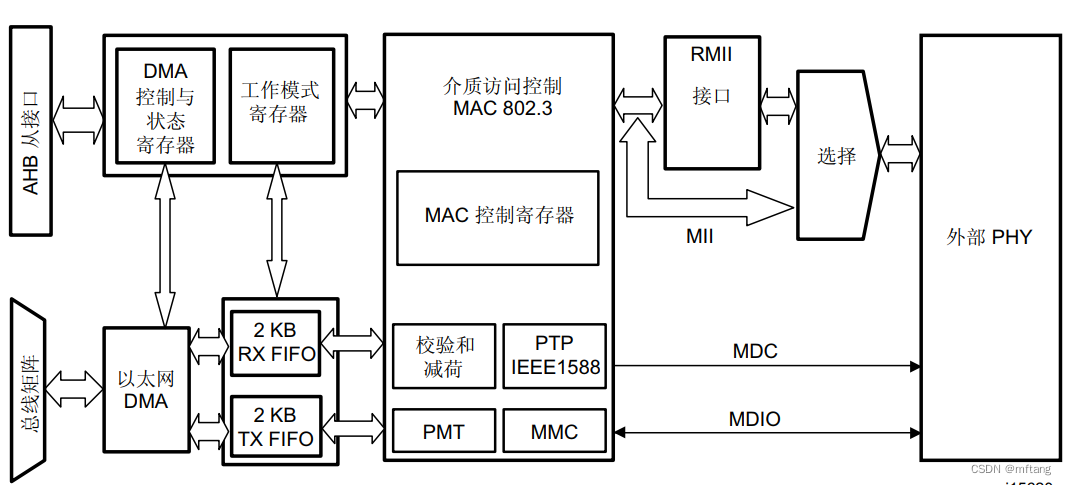

以太网外设包括带专用 DMA 控制器的 MAC 802.3(介质访问控制)。它支持默认情况下使用的介质独立接口 (MII) 和简化介质独立接口 (RMII),并通过一个选择位在两个接口间进行切换(请参见 SYSCFG_PMC 寄存器)。DMA 控制器通过 AHB 主从接口与内核和存储器相连。 AHB 主接口用于控制数据传输,而AHB 从接口则用于访问“控制和状态寄存器” (CSR) 的空间。在进行数据发送时,首先将数据由系统存储器以 DMA 的方式送至发送 FIFO (Tx FIFO) 进行缓冲,再通过 MAC 内核发送。同样,接收 FIFO (Rx FIFO) 则存储通过线路接收的以太网帧,直到这些帧通过 DMA 传送到系统存储器。以太网外设还包括用于与外部 PHY 通信的 SMI。通过一组配置寄存器,用户可以为 MAC 控制器和 DMA 控制器选择所需模式和功能。

3 RMII接口

3.1 接口介绍

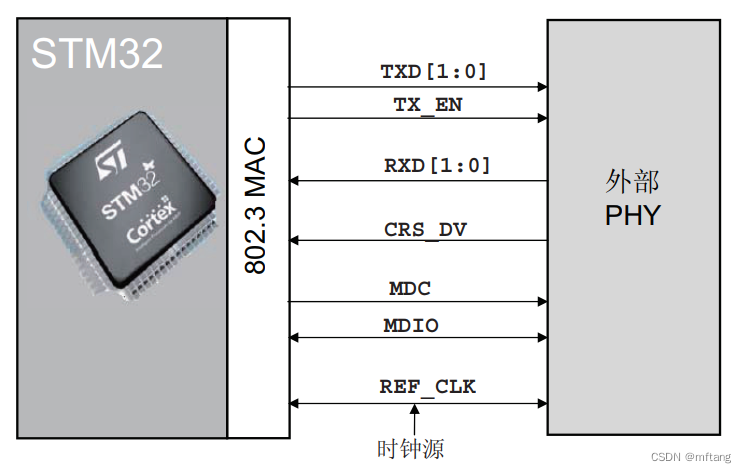

精简介质独立接口 (RMII) 规范降低了 10/100 Mbit/s 下微控制器以太网外设与外部 PHY 间的引脚数。根据 IEEE 802.3u 标准, MII 包括 16 个数据和控制信号的引脚。 RMII 规范将引脚数减少为 7 个(引脚数减少 62.5%)。

RMII 接口是 MAC 和 PHY 之间的实例化对象。这有助于将 MAC 的 MII 转换为 RMII。 RMII具有以下特性:

1)支持 10-Mbit/s 和 100-Mbit/s 的运行速率

2)参考时钟必须是 50 MHz

3)相同的参考时钟必须从外部提供给 MAC 和外部以太网 PHY

4)它提供了独立的 2 位宽(双位)的发送和接收数据路径

3.2 精简介质独立接口信号

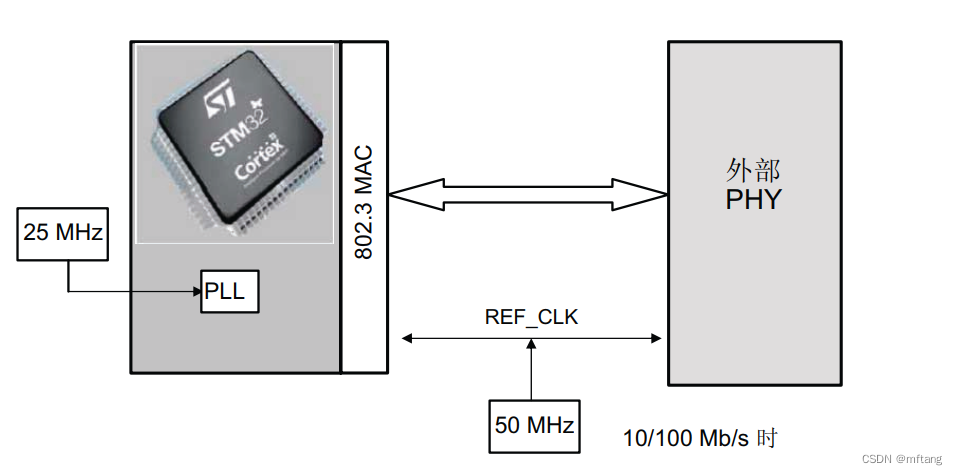

3.3 RMII 时钟源

使用外部 50 MHz 时钟驱动 PHY 或使用嵌入式 PLL 生成 50 MHz 频率信号来驱动 PHY。

3.4 RMII 选择

使用 SYSCFG_PMC 寄存器中的配置位 23 MII_RMII_SEL 选择 MII 或 RMII 模式。以太网控制器处于复位模式或使能时钟前,应用程序必须设置 MII/RMII 模式。

用于 STM32F405xx/07xx 和 STM32F415xx/17xx 的 SYSCFG 外设模式配置寄存器 (SYSCFG_PMC)

SYSCFG peripheral mode configuration register

偏移地址: 0x04

复位值: 0x0000 0000

位 23 MII_RMII_SEL:以太网 PHY 接口选择 (Ethernet PHY interface selection)

由软件置 1 和清零。这些位控制以太网 MAC 的 PHY 接口。

0:选择 MII 接口

1:选择 RMII Why 接口

注意: 必须在 MAC 处于复位状态且在使能 MAC 时钟之前完成此配置。

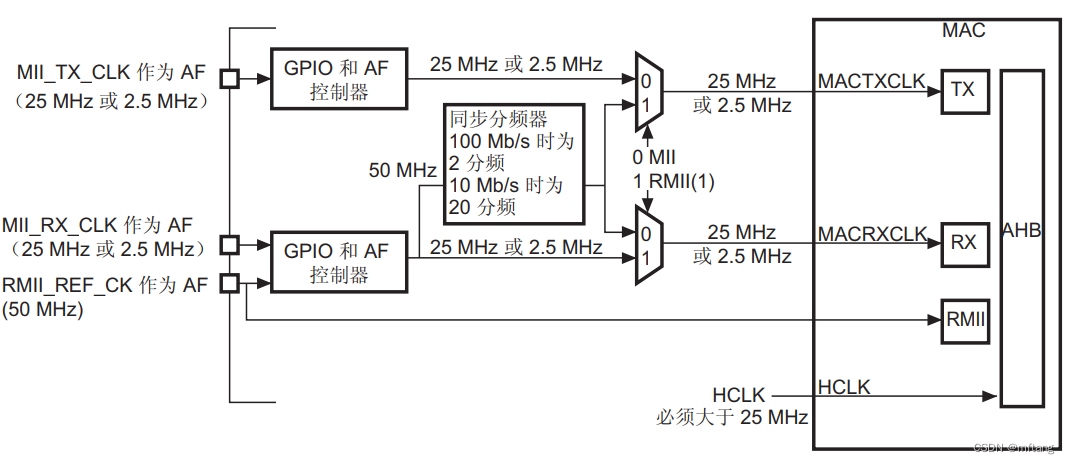

3.5 RMII内部时钟方案

支持 MII 和 RMII 以及 10 和 100 Mbit/s 运行所需的时钟方案下图所示。

要节省引脚,需在同一个 GPIO 引脚上复用 RMII_REF_CK 和 MII_RX_CLK 这两个输入时钟信号。

4 RMII工作时序

4.1 发送序列

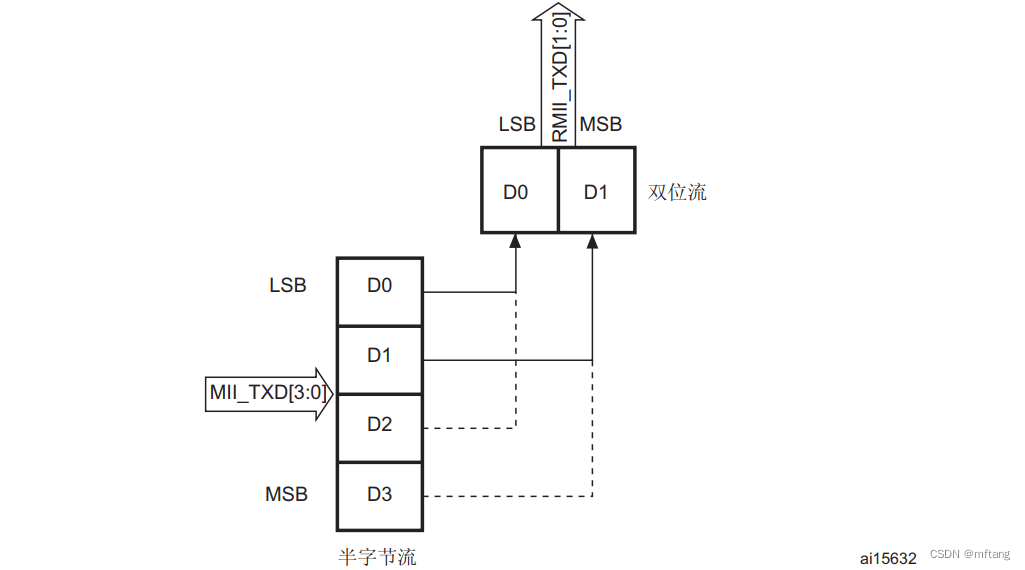

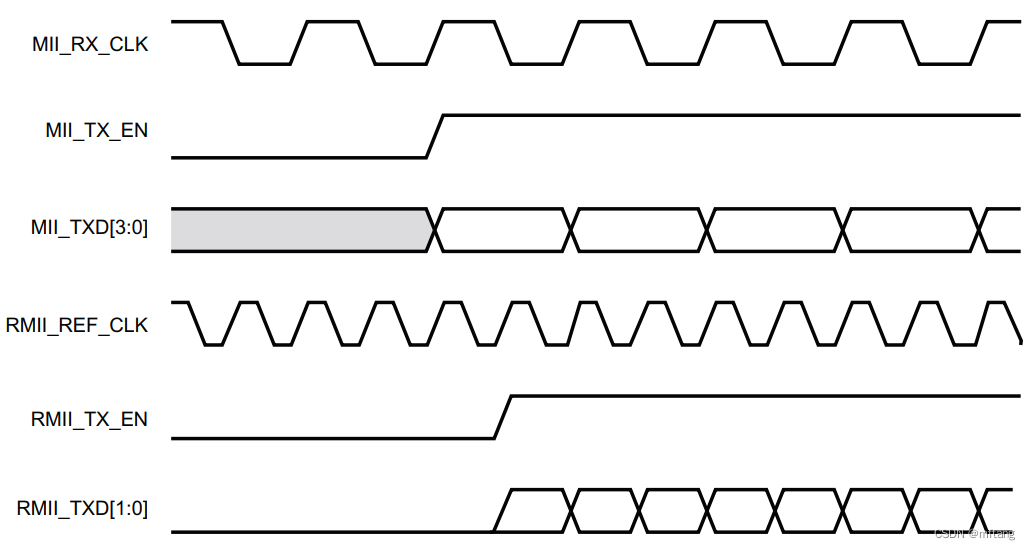

来自 MII 的每个半字节都在 RMII 上发送,一次发送双位,双位的发送顺序如图 所示。首先发送位序较低的位( D1 和 D0),再发送位序较高的位( D2 和 D3)。

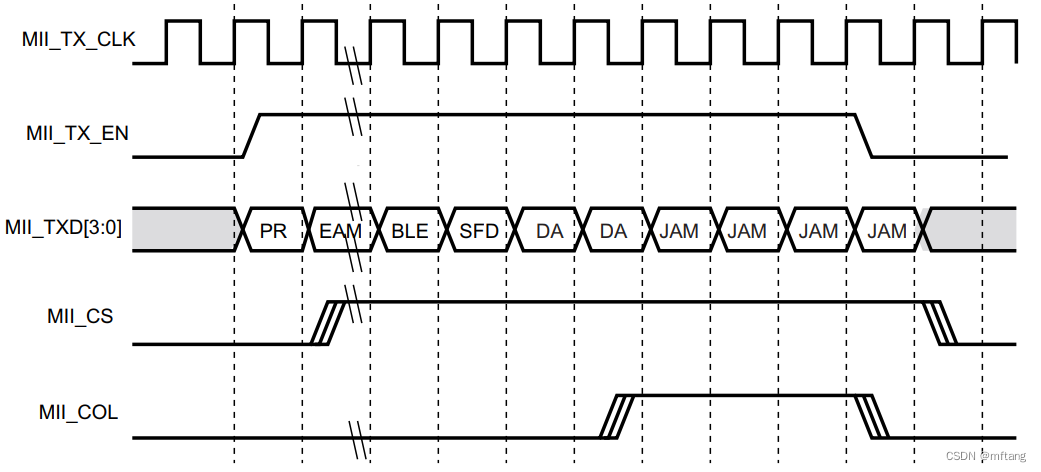

4.2 发送时序图

1)无冲突发送

2) 有冲突发送

3)RMII 模式下的帧发送

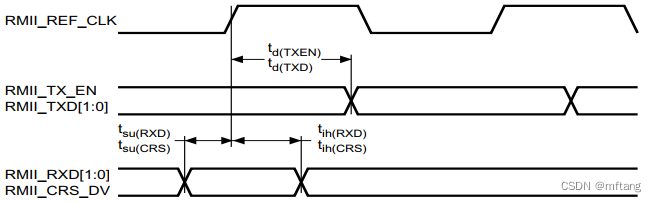

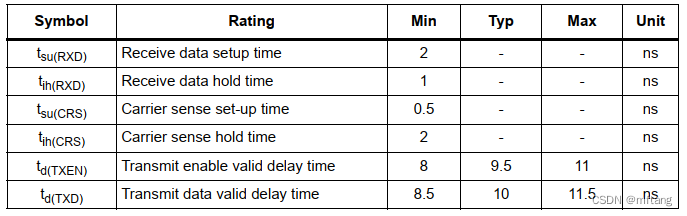

4.3 RMII时序参数

1)Ethernet RMII timing diagram

2) Dynamic characteristics: Ethernet MAC signals for RMII

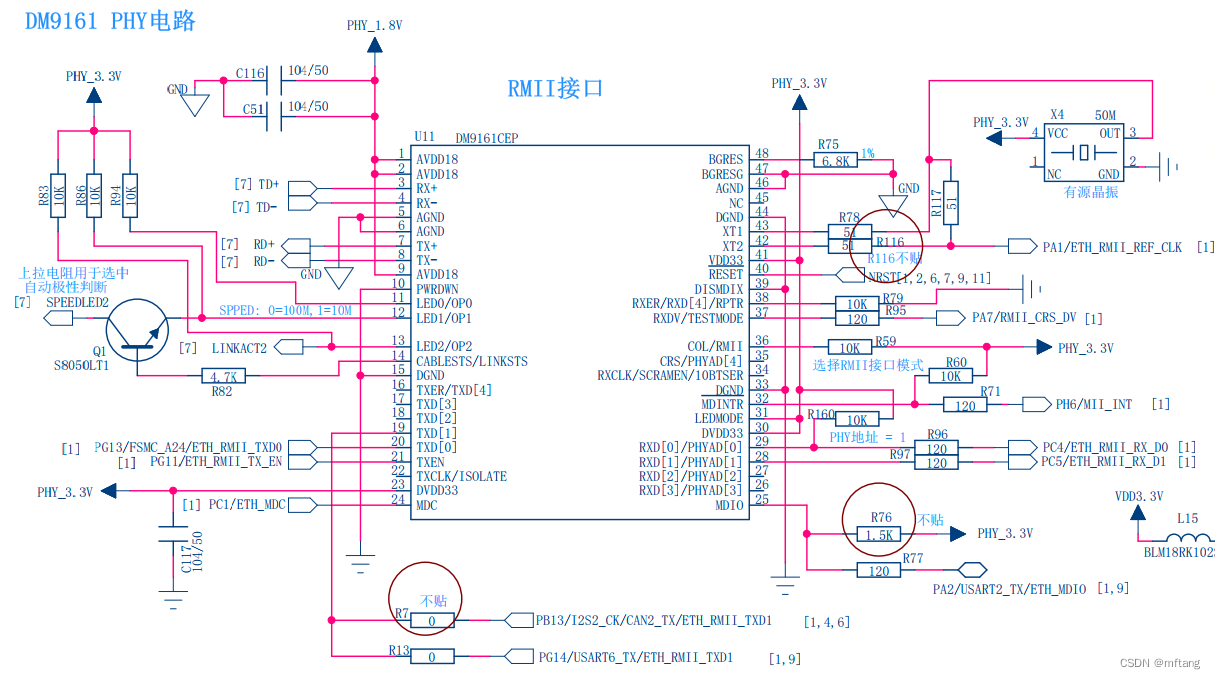

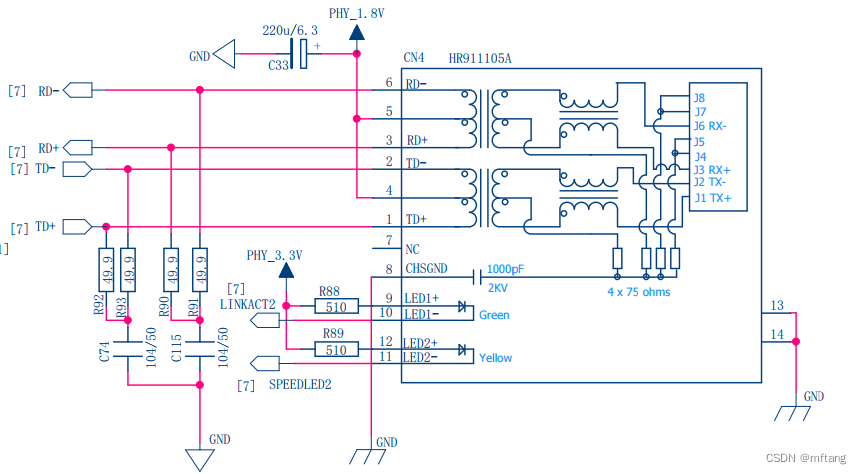

5 RMII的应用电路

5.1 电路图

5.2 STM32F4与RMII接口

| RMII( DM9161) | STM32F4(ETH) | 功能介绍 |

|---|---|---|

| TXD-1 | PG14 | ETH-RMII-TXD1 |

| TXD-0 | PG13 | ETH-RMII-TXD0 |

| TX-EN | PG11 | TH-RMII-TX-EN |

| MDC | PC1 | ETH-MDC |

| RXDV | PA7 | RMII_CRS_DV |

| MDINTR | PH6 | RMII_INT |

| RXD-0 | PC4 | ETH-RMII-RXD0 |

| RXD-1 | PC5 | ETH-RMII-RXD1 |

| MDIO | PA2 | ETH-MDIO |

| XT2 | PA1 | ETH-RMII-REF_CLK |