- 1MySQL多条语句同时执行_mysql支持多语句同时执行吗

- 2百度开源进行时

- 3com.mysql.jdbc.Driver 和 com.mysql.cj.jdbc.Driver的区别以及设定serverTimezone

- 4孙宇晨大举进驻NFT艺术的背后:区块链+艺术还能有怎样的玩法?_nft与实体

- 5微信自定义菜单的创建(微信账号绑定功能的实现 Java)_java 账号绑定微信

- 6解决recaptcha、cloudflare、incapsula验证问题_突然有了cloudflare验证

- 7二本4年测龄年仅25岁,五面阿里(定薪25K)....._阿里巴巴测试开发工程师工资

- 8微信小程序抢票脚本

- 9在mybatis中处理集合、循环、数组和in查询等语句的使用_mybatis 循环数组

- 10mysql同一机器安装8.3和5.73版本步骤_mysql安装5.7和8.3

SPI主机驱动功能仿真验证(AD9361和FLASH)_ad9361配置文件转verilog

赞

踩

上一次做了一个SPI主机驱动,代码:SPI主机驱动: SPI主机驱动,支持4从机,可配置4种传输模式。支持纯指令,读数据(指令+地址+读数据),写数据(指令+地址+数据) (gitee.com)![]() https://gitee.com/hywhj34343453/spi-host-driver

https://gitee.com/hywhj34343453/spi-host-driver

说明地址:四线标准SPI主机驱动Verilog-CSDN博客

一 .新增内容说明

1.这次首先对之前的主机驱动添加了一些新东西,以尽可能多地适应各种情况,比如:

① 支持对于每个读写数据字节的MSB和LSB传输。

② 添加新的指令,以适用于添加了“掩码”的读指令。

2.比起之前的读写回环测试,这次为了更好地测试正确性和实用性,试着应用于AD9361 SPI配置寄存器和FLASH指令。

二.SPI 配置 AD9361寄存器

1.参考资料【第5讲】Zedboard SPI配置AD9361寄存器初始化!!!Verilog SPI通信转换分析!!!AD9361 Init Done!!!_哔哩哔哩_bilibili

《AD9361 Reference Manual》

2.实现思路

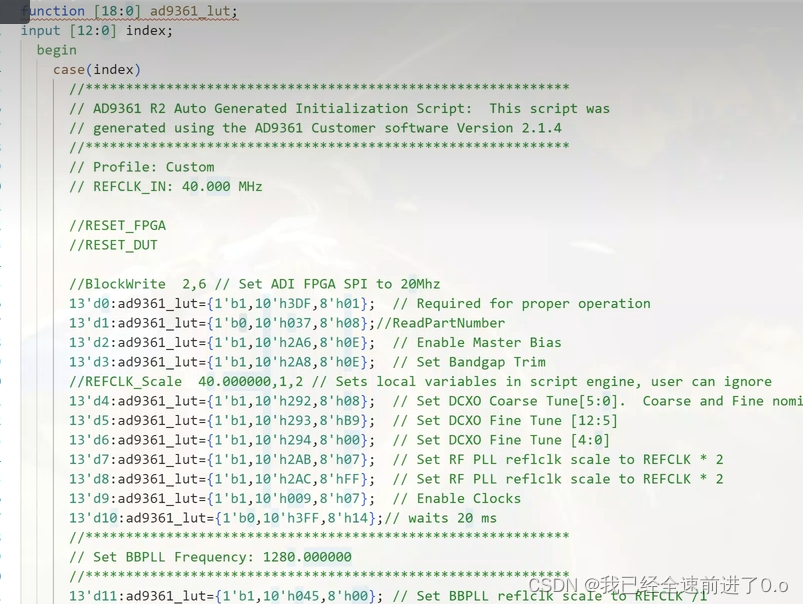

视频中,是将指令写在9361_lut中,在9361_init模块中,利用index索引指令,然后通过9361_spi传输指令和数据交互。图1是视频中,9361_lut的样子。

图1

于是我截取了其中一部分:

然后后面就是利用我自己的SPI主机驱动,编写对应的译码模块,来实现AD9361寄存器的配置。

3.实现过程

(1)与SPI主机驱动对接的主体模块

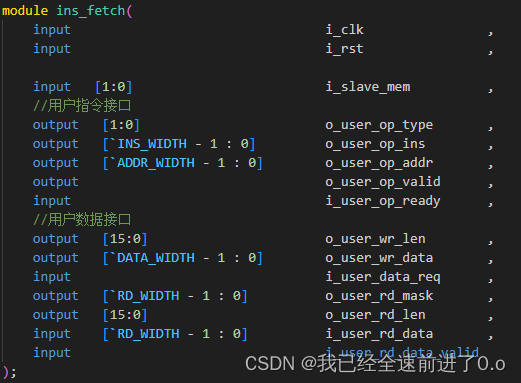

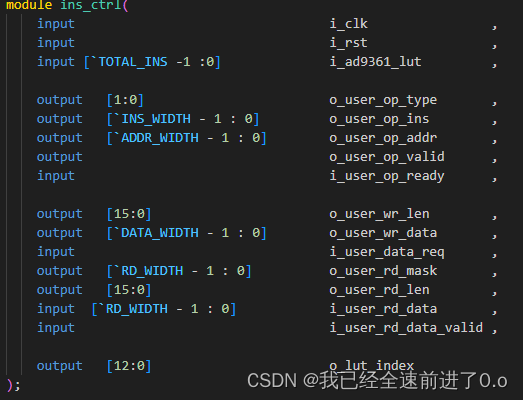

模块内部有两个子模块:

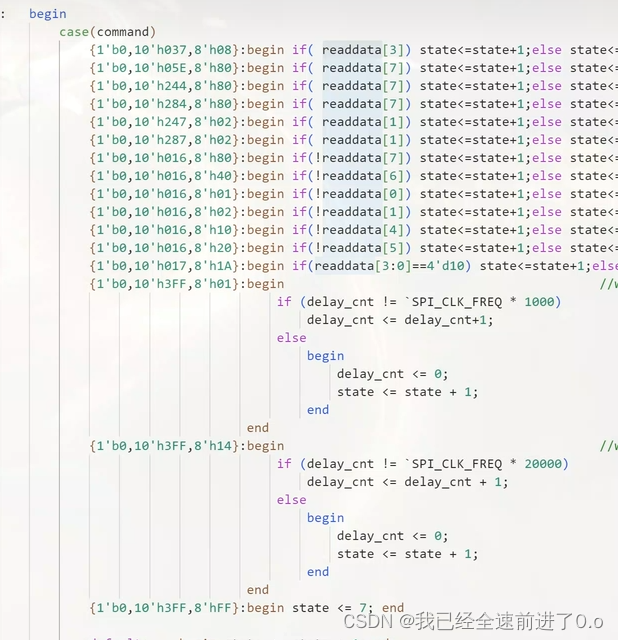

① :ins_lut,作为同视频中一样的指令lut模块。

② : ins_ctrl,作为针对AD9361的特殊指令控制模块,负责翻译指令,判断指令index是否该往下走等。

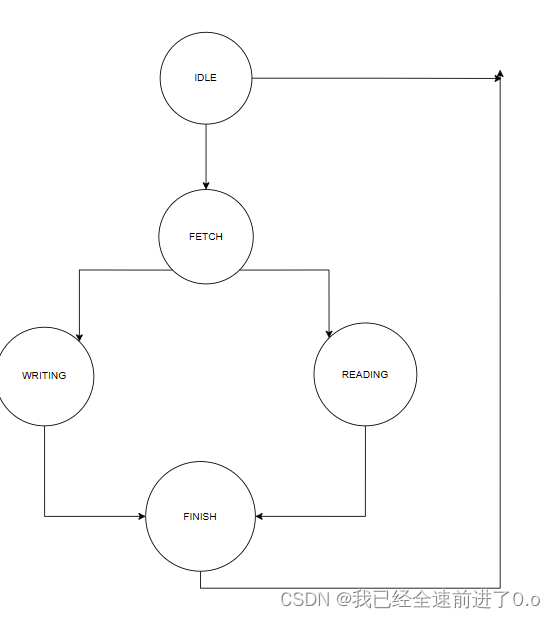

模块内部状态图:

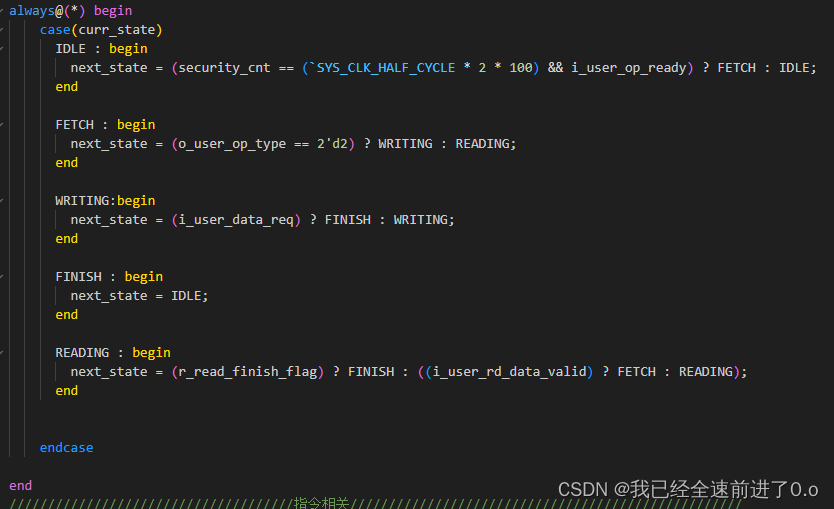

按照视频中的意思,为了稳定性,设置一个延迟计数器,不同指令间有一个设定的时间差。当这个计数器计数到一定值的时候,从IDLE跳转,判断当前指令是读还是写,分别进入WRITING和READING状态。进入WRITING状态后,取了个巧,就是ins_lut中的指令全是只有1个8bit数据部分,所以整个写过程,user_data_req只会拉高一次。所以,当输入的i_user_data_req拉高后,就会接收数据,也就意味着,指令已经都接收完了,可以进入FINISH状态了。而READING状态的跳转比较复杂,视频中是根据不同指令读取不同数据的情况来判断状态是否跳转,然后有些指令是延时指令,还须延时特定时间后,状态才会跳转,故而这里利用r_read_finish_flag来控制状态的跳转。FINISH状态下,将指令index加1,延迟计数器归零。自动跳转到IDLE.

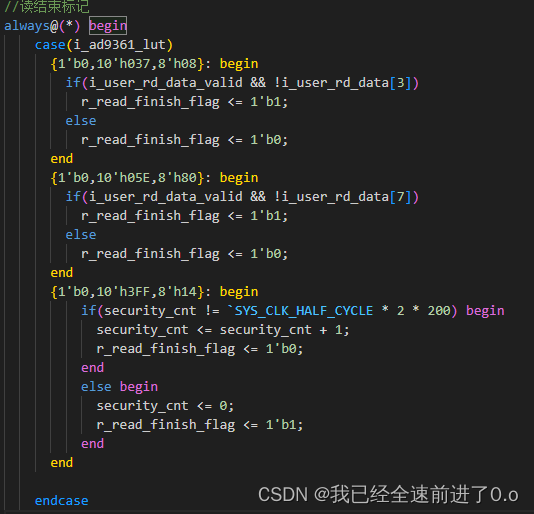

r_read_finish_flag按照视频的意思编写。

视频中表述是这样的:

我的表述是这样的:

4.仿真结果

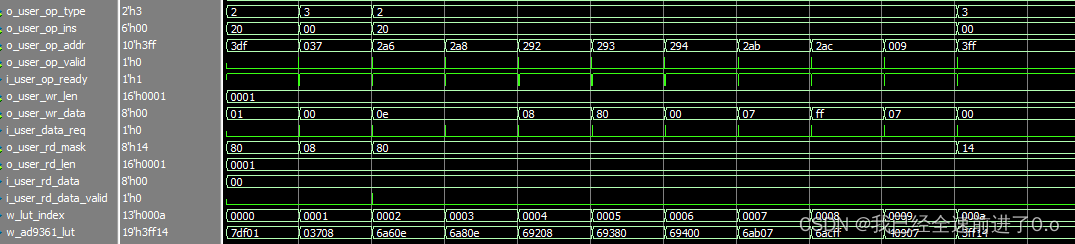

首先看整体:

可以看到两个指令之间存在特定延迟,第10个指令为特殊的延时指令,所以延时更长。

然后看细节:

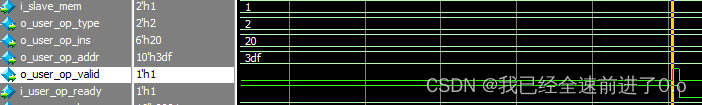

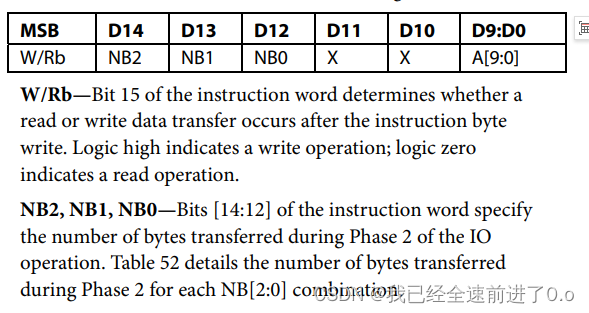

可以看到,第一个指令有效拉高时,接收到的指令类型是2,写指令。接收到的指令是6‘h20,也就是10_0000。这是对的,解释一下,从AD9361使用手册中可以看到:

有3位表示交互的数据个数,000表示1个数据交互,001表示2个,依次类推。然后跟着2位不关心位。由于ins_lut中,交互数据部分都是只有一个,所以这里是000,由由于是写指令,所以,最终的有效指令就是100000.我是根据指令后面接多少数据来判断的,我不确定实际是否是这样,希望有高人指点。我的逻辑是这样的:

![]()

然后,传输地址是3df。可以看到,这也是对的。因为第一个指令就是这么写的:

![]()

写数据要看user_data_req:

![]()

可以看到写数据是8'h01.这是对的。

此时的SPI_MOSI是:

![]()

对应的数据是:100000_1111011111_00000001(指令+地址+数据)是符合的。

后面检测就不一一说明了。

三.FLASH验证

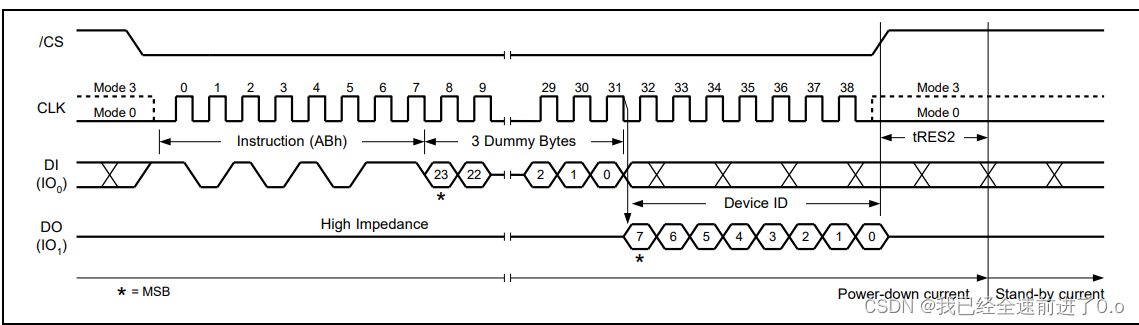

由于目前没有使用FLASH的需求,所以简单验证一下FLASH的读取设备ID指令就结束。利用W25Q128JV的仿真模型,指令时序图入下:

按照要求写入指令和虚地址即可。

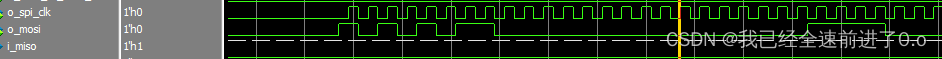

仿真结果如图:

这是写指令和地址,可以看到写入指令确实是1010_1011(ABh)

然后是读取数据(设备ID)

![]()

可以看到,仿真模型的设备ID是8'h17,我们来看看读取的是不是这个:

可以看到读取是对的。

四.总结

我是想尽量把这个主机驱动做得可以适用于绝大多数SPI设备,后面有时间且有钱的话,可以去看看上板的测试。当然啦,也是因为参加的比赛是9361相关的,要是我写的那个基带处理模块能够过初赛的话,就可以好好看看我这个SPI驱动的效果了。。。0.o。过不了的话,可能暂时就没后续啦,得考虑做点其他好玩的了。希望读到这里有缘人要是会9361的话,可以带带我0.o,谢谢啦。