热门标签

热门文章

- 1Linux Workqueue_linux中workqueue详细实现机制

- 2flink checkpoint 源码分析 (二)

- 3spark代码sc统一配置_spark sc

- 4关于org.apache.kafka.common.errors.TimeoutException: Failed to update metadata after 60000 ms.问题的解决

- 5算子的含义_算子 组合 csdn

- 6Redis单例、主从、哨兵、集群_redis只有一台哨兵实例可以吗

- 7微服务 - Eureka 服务注册与发现机制_注册中心eruka集群下如何进行消息同步

- 8Java后端面试高频问题:Redis_java面试问redis比较多

- 9Linux操作系统 第1关:Linux初体验_第1关:linux初体验

- 10tensorflow06——正则化缓解过拟合_dot.csv

当前位置: article > 正文

国产FPGA:替代ATLERAEP4CE10E22的AG10KL144

作者:我家自动化 | 2024-07-09 01:26:54

赞

踩

ag10kl144

背景

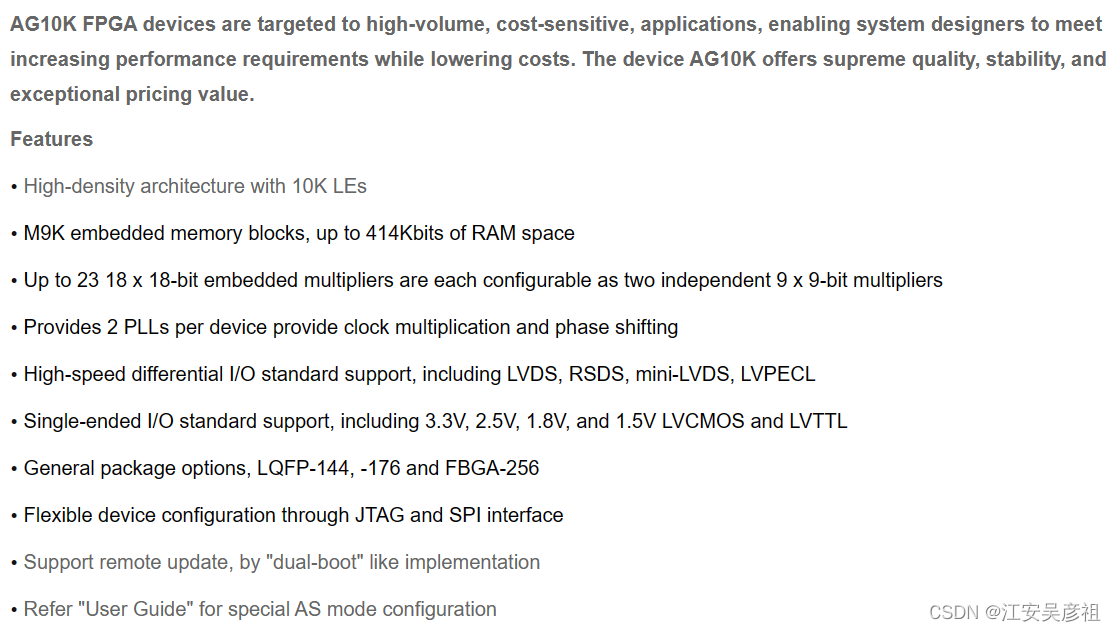

AG10K用于PIN TO PIN替代ATLERA EP4CE10E22、EP3C10E144的FPGA,其资源介绍如下:

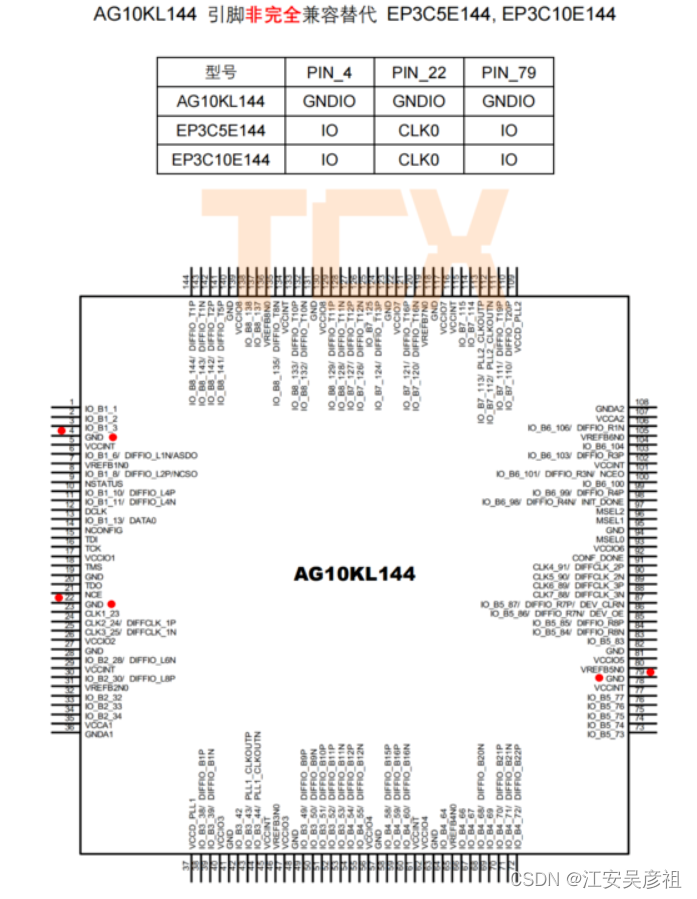

引脚对应如下:

一般Quartus II开发方式

新建工程

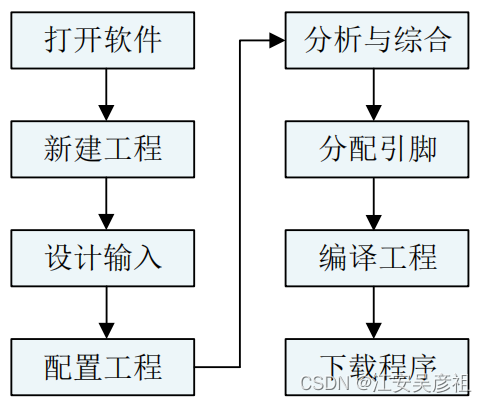

FPGA使用Quartus II开发,开发的整体流程如下:

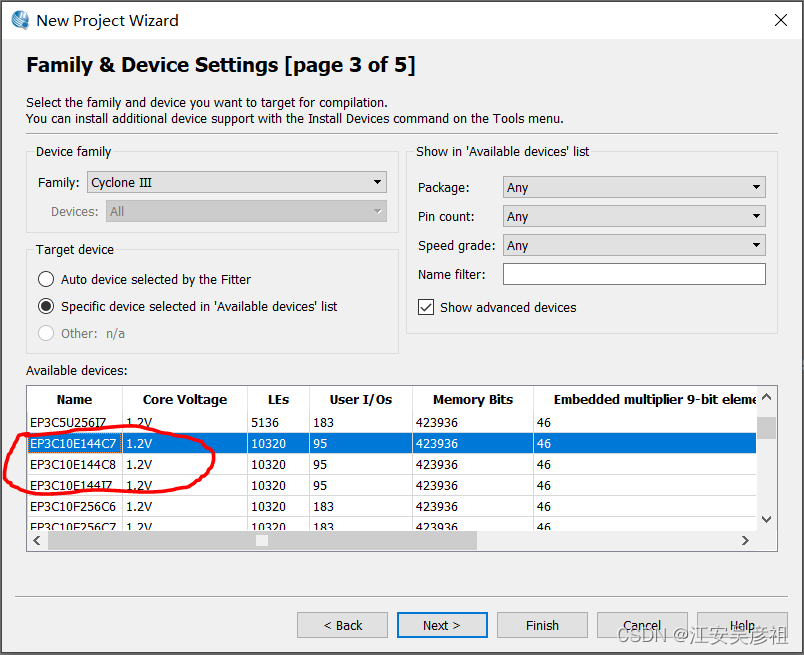

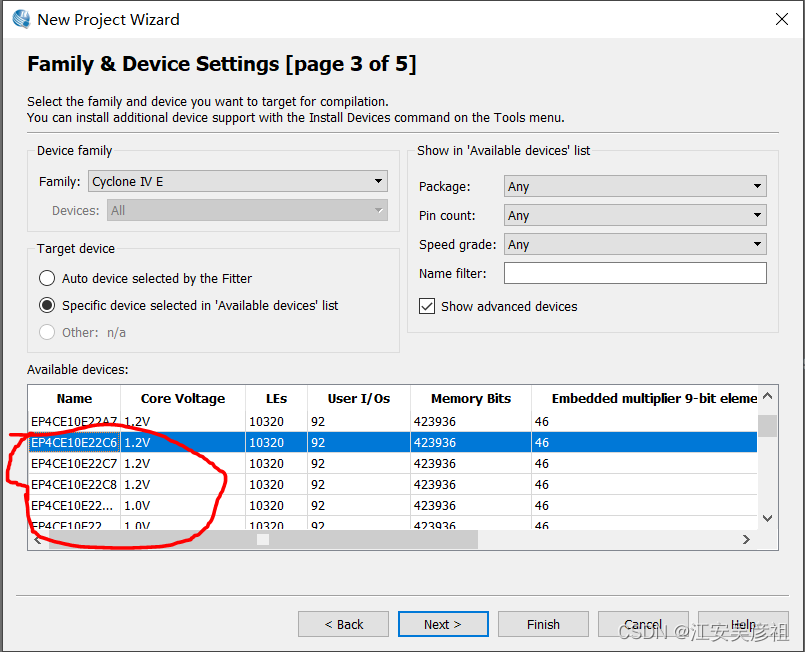

新建工程时选用Cyclone III或者Cyclone IV库,如下图:

- Cyclone III:

- Cyclone IV:

设计输入

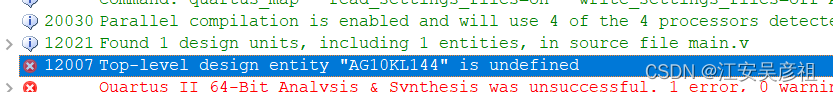

新建工程后添加verilog文件,一定要记得顶层verilog文件名称一定要和工程名称保持一致,否则会报下面的错误:

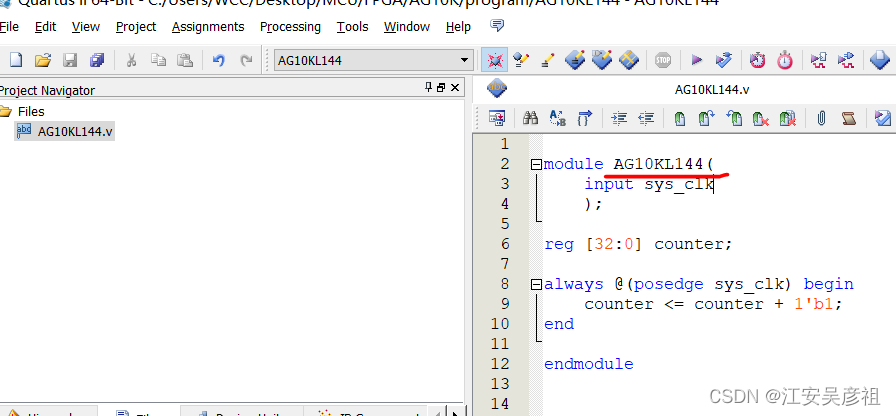

我们添加verilog文件并写测试代码如下:module名一定要和文件名保持一致

这里我们就完成了设计输出代码。下面就可以分析综合来检查代码语法错误。

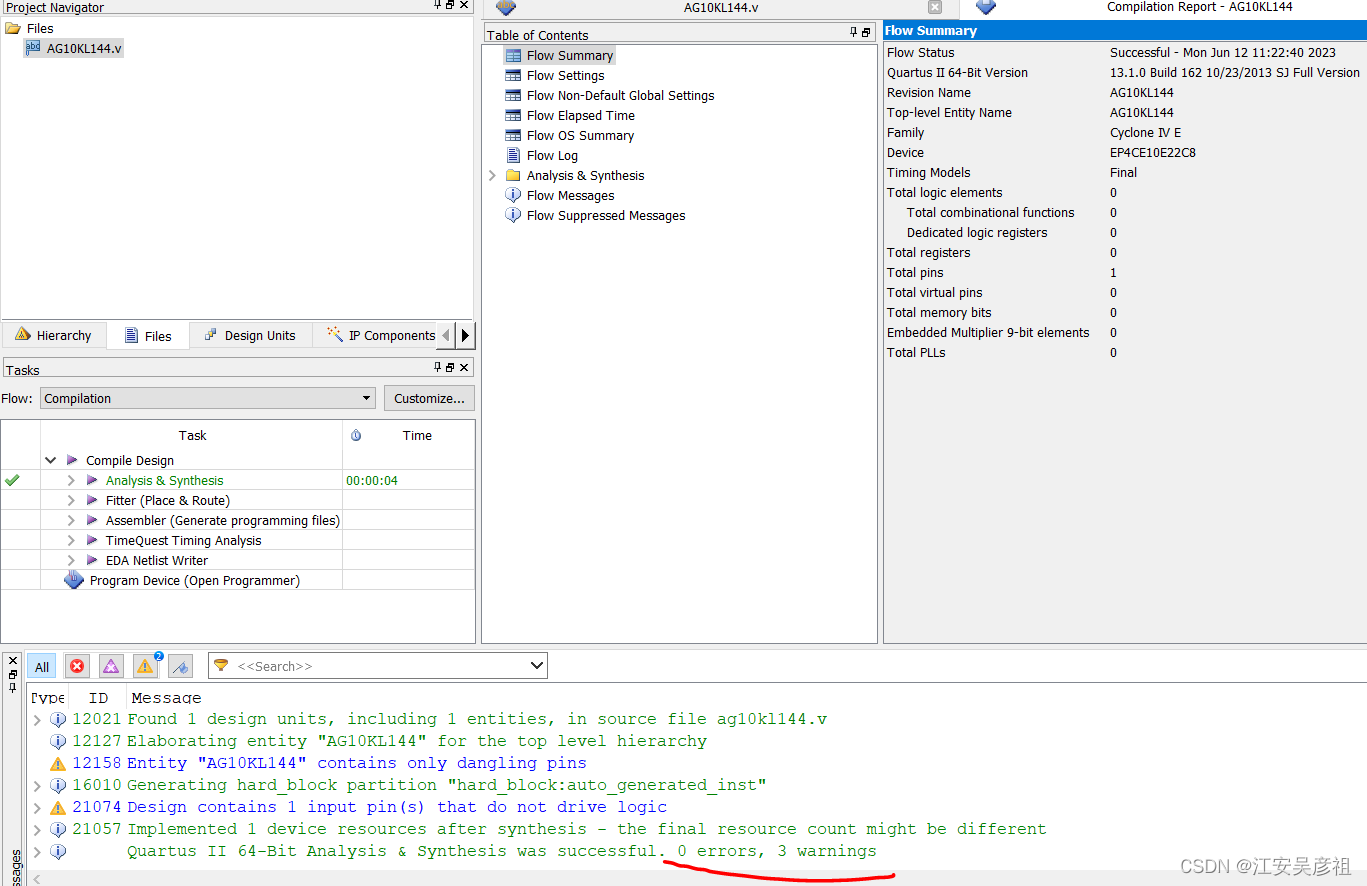

分析综合

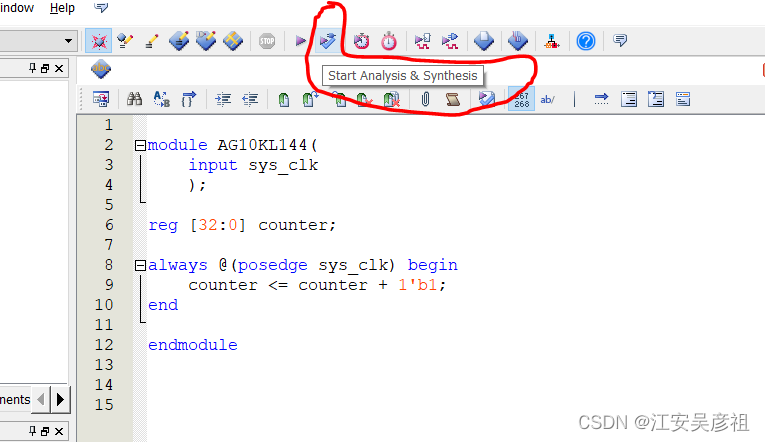

点击以下图标开始分析综合代码:

结果如下:

引脚分配

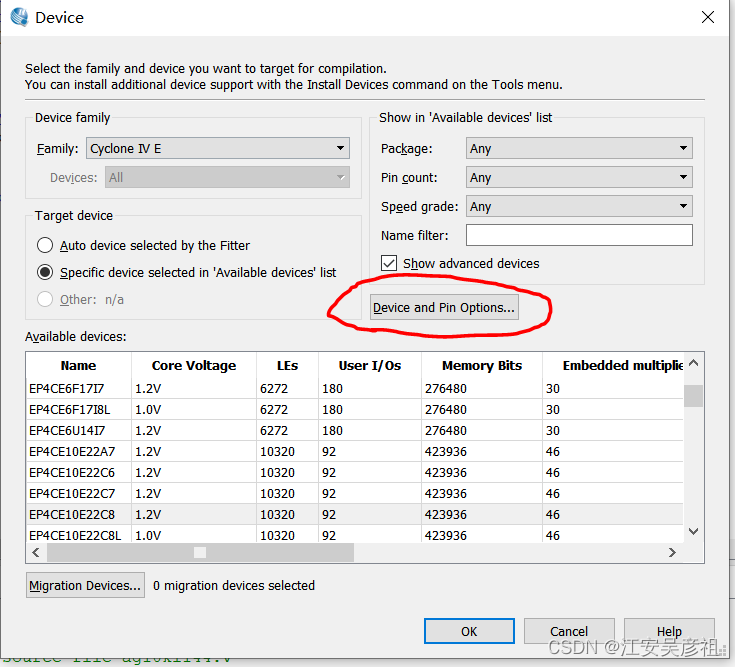

首先,我们点击 Assignments -> Device -> Device and Pin Options,如下:

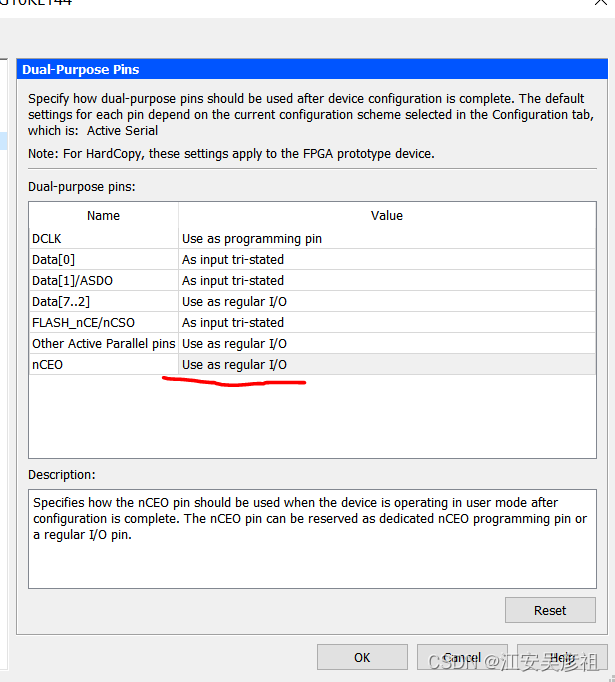

将下图中默认的编程引脚改为一般IO引脚,如下图:

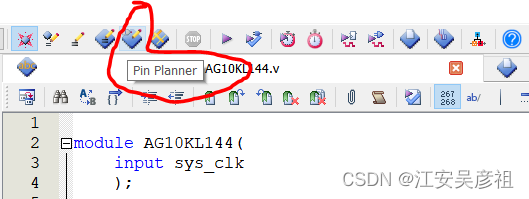

然后点击Pin Planner,进行引脚分配:

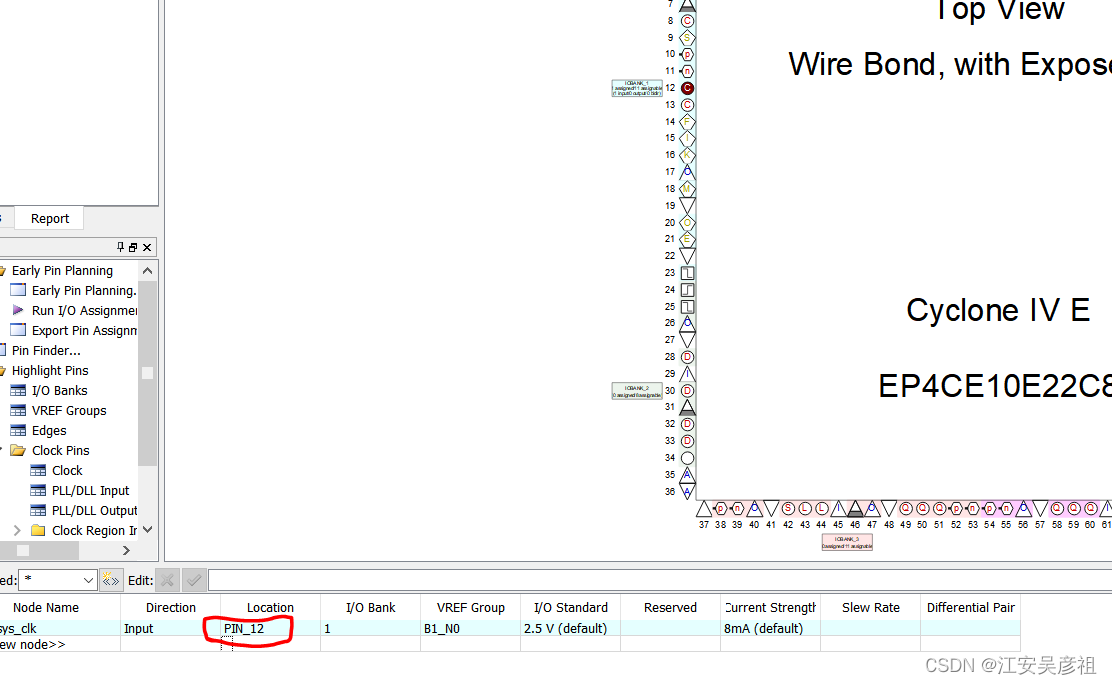

在下图中所示位置选择引脚即可:

编译工程

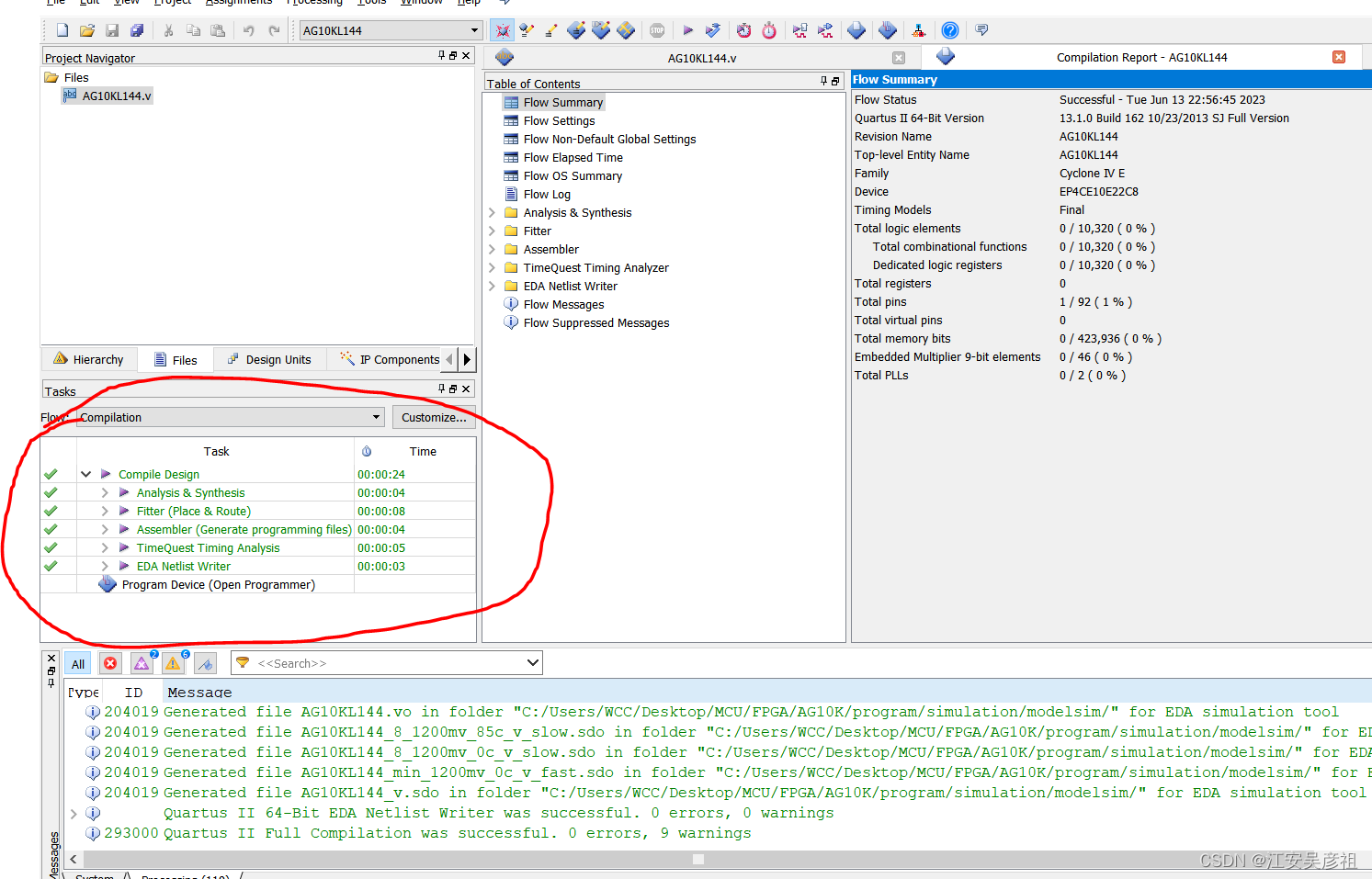

分配完引脚之后,我们就可以将代码生成电路,即布局布线。点击 Start Compilation,进行编译:

编译后结果如下:

下载

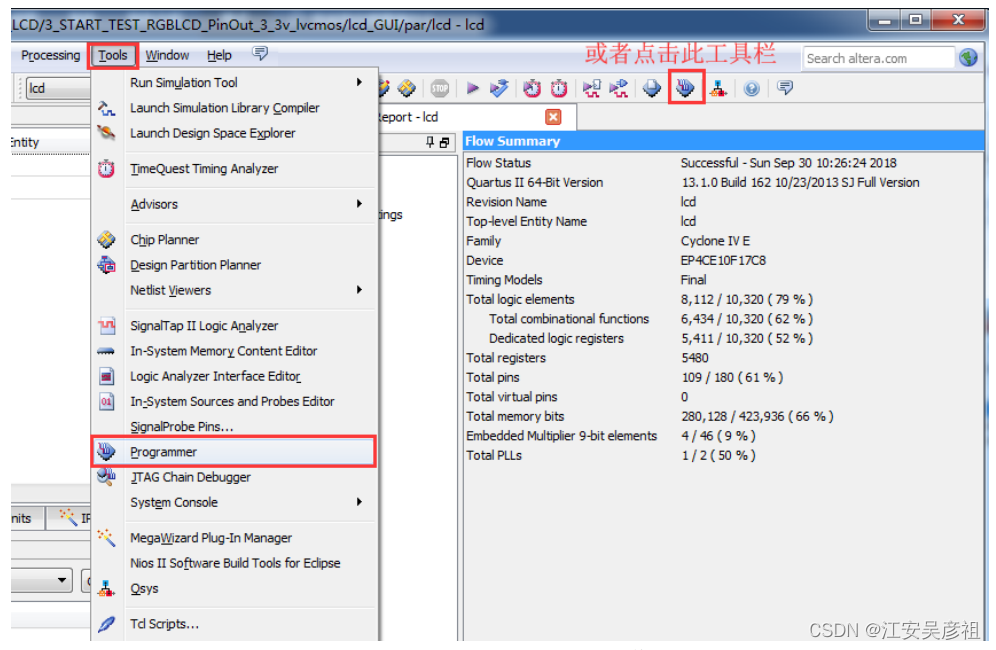

完成布局布线之后,我们就可以使用USB Blaster将程序烧录到FPGA的FLASH里面了。

使用AMG的综合工具Supra

由于Quartus II中我们使用的是Cyclone IV,因此我们需要使用AGM提供的Supra将工程进行转换,详细使用教程可以参考:Supra使用手册

参考:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/801008

推荐阅读

相关标签