- 1使用深度学习进行语音情感识别:案例演示与代码实现_语音情感识别技术案例

- 2MySQL之查询性能优化(九)

- 3X-AnyLabeling标注工具的使用_x anythinglabel

- 4微服务的构建环境比较--Spring Cloud和Kubernetes_kubernetes springcloud

- 5Ubuntu 16.04 安装 HBase2.2.2_hbase2.2.2下载

- 6Linux常用命令redis相关_linux rename-command config

- 7堆排序之Top-K问题

- 82024最新python毕设选题推荐,毕业设计题目大全(文末附源码)_基于python的毕业设计题目

- 9基于esp8266的手机远程控制开关装置_远程开关控制器设计

- 10【云原生】kubernetes中secret原理详解与应用实战

干货!ASIC芯片设计开发全流程讲解(内附ASIC设计流程讲解视频)_主控芯片设计开发调试

赞

踩

一颗芯片是如何造出来的,相信对行业稍有涉猎的同学,都能简单作答:即先通过fabless进行设计,再交由Foundry进行制造,最后由封测厂交出。

但这种程度仅仅是一个外行的基本认知,如果要在入行IC进行职业方向选择或是在面试中被问到时,则需要更加专业的回答。

这篇文章就是详细介绍数字IC设计的全流程内容,建议直接点赞收藏。(文末有视频福利哦)

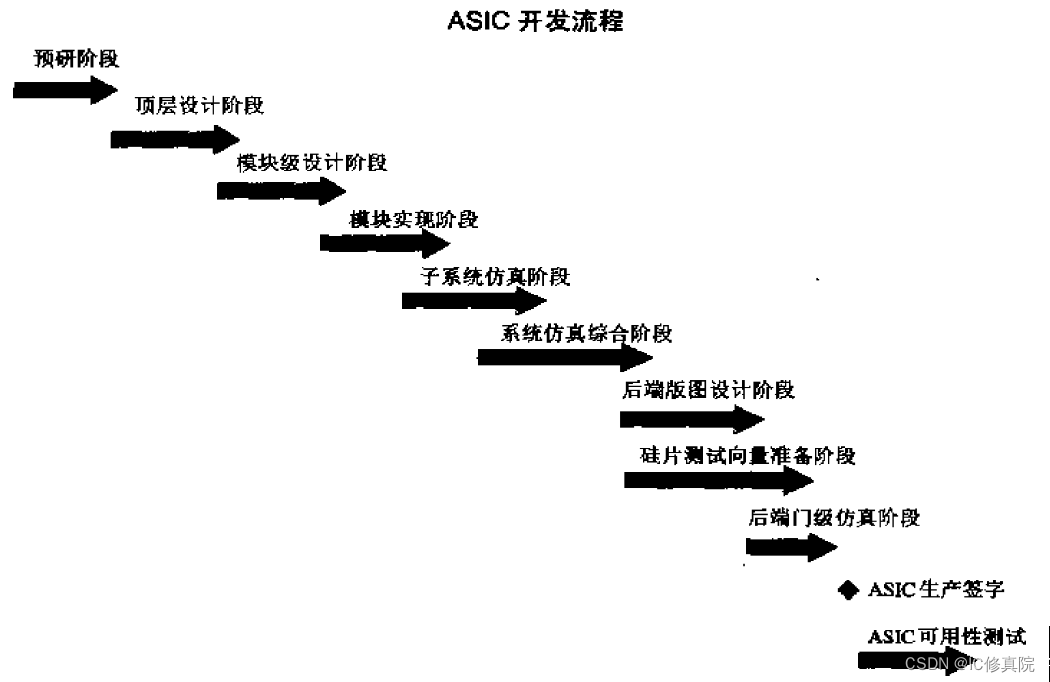

ASIC项目的主要步骤包括:

预研阶段;

顶层设计阶段;

模块级设计阶段;

模块实现阶段;

子系统仿真阶段;

系统仿真,综合和版图设计前门级仿真阶段;

后端版面设计阶段;

测试向量准备阶段;

后端仿真阶段;

生产签字;

硅片测试阶段。

ASIC开发流程中各步骤

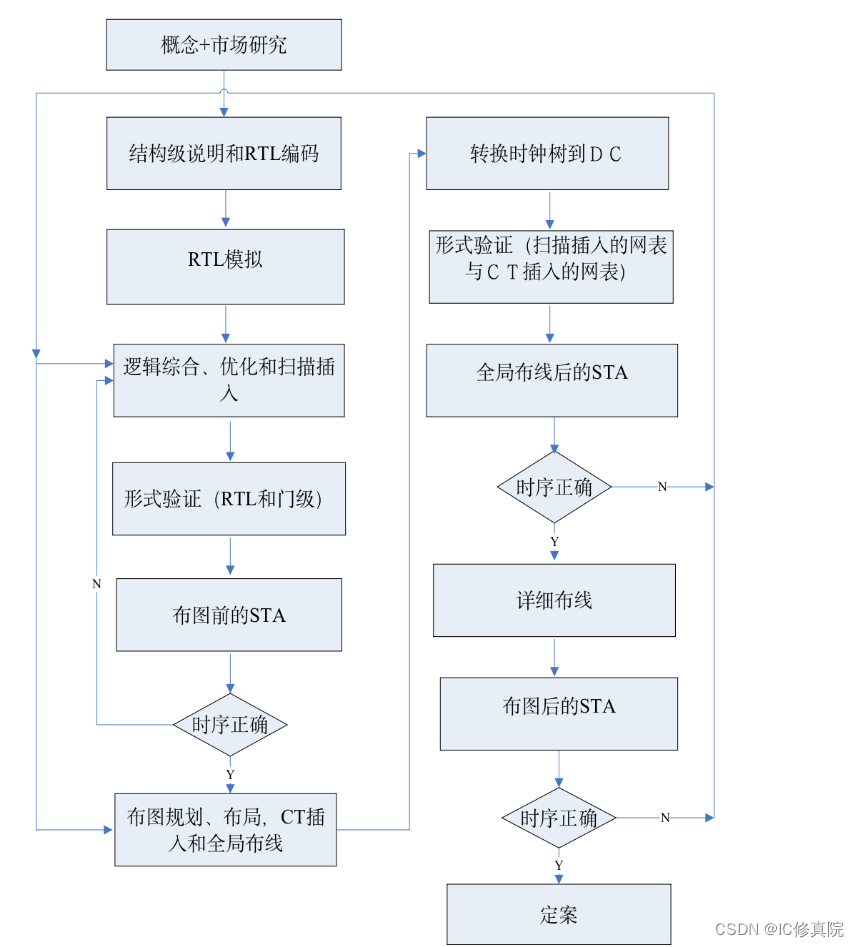

传统设计流程

设计的一般步骤

结构及电学特性编码

HDL中的RTL编码

为包含存储单元的设计插入DFT memory BIST

为了验证设计功能,进行详尽的动态仿真 实际环境设置,包括将使用的工艺库及其他环境属性

使用Design Compiler工具对具有扫描插入的设计进行 约束和综合设计

使用Design Compiler的内建静态时序分析机进行模块级静态时序分析

设计的形式验证,使用Formality将TRL和综合后的网表进行对比

使用PrimeTime进行整个设计布图前的静态时序分析

对布图工具进行时序约束的前标注

11)具有时序驱动单元布局,时钟树插入和全局布线的初始布局划分

将时钟树转换到驻留在Design Compiler中原始设计(网表)

在Design Compiler中进行设计的布局优化

使用Formality在综合网表和时钟树插入的网表之间进行形式验证

在全局布线后(11步)从版图提取估计的延时

从全局布线得到的估计时间数据反标注到PrimeTime

使用在全局布线后提取的估计延时数据在PrimeTime在中进行静态时序分析

设计的详细布局

提取来自详细布局设计的实际时间延迟

实际提取时间数据反标注到PrimeTime 使用PrimeTime进行布图后的静态时序分析

布图后的门级功能仿真(如果需要)

在LVS(版图对原理图)和DRC(设计规则检查)验证后定案

规范和RTL编码

结构规范定义了芯片的功能并划分为一些能够处理的模块,电学特性规范通过时序信息定义模块之间的关系

设计可用三个抽象层次来表示:行为级,寄存器传输级RTL和结构级。

动态仿真

通过仿真RTL代码以检查设计的功能,目前的仿真器都能够仿真行为级及RTL级编码

约束、综合和扫描插入

以前:手工将HDL转换为电路图并描述元件间的互连来产生一个门级网表。

综合:用工具完成RTL级到门级网表的转换,这个过程就称为综合

定义综合环境的文件,详细说明了工艺单元库和DC在综合过程中使用的其它相关信息。

形式验证

形式验证技术使用数学的方法来确认一个设计,不考虑工艺因素,如时序,通过与参考设计的对比了检查一个设计的逻辑功能。

形式验证和动态仿真,形式验证技术通过证明两个设计的结构和功能是逻辑等价的来验证设计;动态仿真只能检查敏感路经。

形式验证的目标是要验证RTL与RTL ,门级网表与RTL代码,两个门级网表之间的对应关系是否正确.

静态时序分析

在整个设计中,静态时序分析是最重要的步骤,一个迭代过程。

静态时序分析充许用户详细分析设计的所有关键路经并给出一个有条理的报告。 对布图前后的门级网表进行静态时序分析,在布图前,PrimeTime使用由库指定的线载模型估计线网延时。如果所有关键路径的时序是可以接受的,则由PrimeTime或DC得到一个约束文件,目的是为了预标注到布图工具。

在布图后,实际提取的延迟被反标注到PrimeTime以提供真实的延迟计算。

布局、布线和验证

布图工具完成布局和布线。布图规划包括单元的布局和时种树的综合,在步图工具中完成。布线一般有两步,全局布线和详细布线。

ASIC设计流程

更多免费视频可点击下方链接领取哦,或者想要了解行情,薪资,岗位的同学也可以通过下方链接进行了解~

这里给大家放个入口:芯片设计入门了解/更多视频课资料领取