- 1IO_总结

- 2mysql开启ssl_mysql ssl

- 3Elasticsearch7.6.x学习笔记(超详细)_es 7.6源码解析

- 4YOLOv7 | 注意力机制 | 添加ECA注意力机制_eca模块

- 5Python 机器学习 基础 之 监督学习 [ 神经网络(深度学习)] 算法 的简单说明_深度学习算法

- 6Flutter-Android签名打包,给小伙伴分享APP吧_flutter android签名打包

- 7C语言实现运动会分数统计_运动会分数统计系统c语言

- 8copy 修改时间_SCI论文审稿时间需要多久?

- 9n皇后问题(DFS)_比赛 题库 提交记录 hack! 博客 帮助 好评差评[-5] #58. n皇后问题百度翻译实时翻

- 10云原生存储:使用MinIO与Spring整合

RK3568平台(显示篇) LVDS协议与波形分析_rk3568 lvds

赞

踩

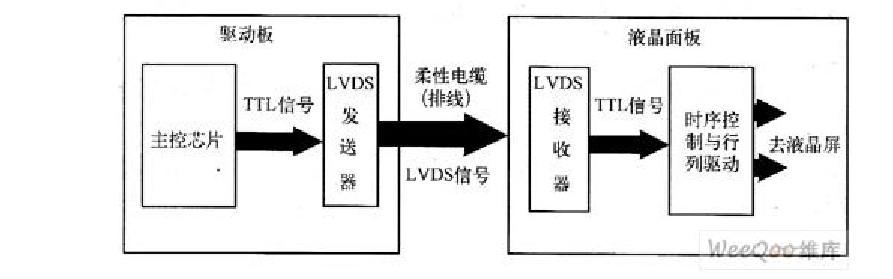

1.LVDS叙述

液晶显示器驱动板输出的数字信号中,除了包括RGB数字信号外,还包括行同步,场同步,

像素时钟等信号。lvds实现数据的高速率,低噪声,远距离,高准确度的传输。

2.LVDS接口电路的组成

3.典型LVDS发送芯片介绍

典型的LVDS发送芯片分为四通道、五通道。

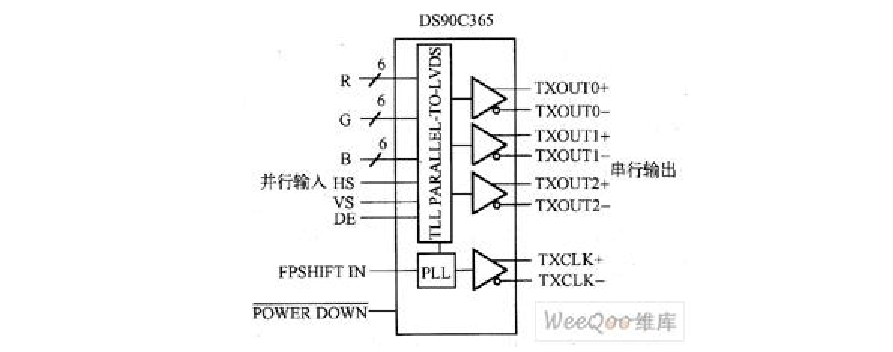

四通道LVDS发送芯片

如图所示为四通道LVDS发送芯片DS90C365内部框图。包含了三个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。

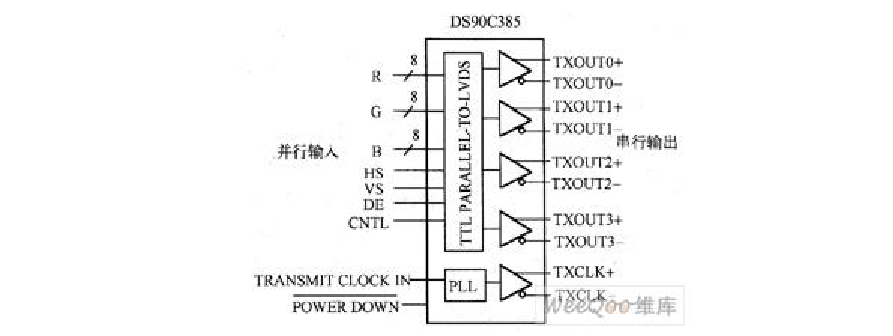

五通道LVDS发送芯片

如图所示为五通道LVDS发送芯片(DS90C385)内部框图。包含了四个数据信号(其中包括RGB、数据使能DE、行同步信号IIS、场同步信号vs)通道和一个时钟信号发送通道。

4.LVDS发送芯片的输入信号

在供6bit液晶面板使用的四通道LVDS发送芯片中,共有十八个RGB信号输入引脚,分别是

R0~R5红基色数据(6bit红基色数据,R0为最低有效位,R5为最高有效位)六个

G0~G5绿基色数据六个

B0~B5蓝基色数据六个

一个显示数据使能信号DE(数据有效信号)输入引

一个行同步信号HS输入引脚

一个场同步信号VS输入引脚

也就是说,在四通道LYDS发送芯片中,共有二十一个数据信号输入引脚。

输入时钟信号:

即像素时钟信号,也称为数据移位时钟(在LVDS发送芯片中,将输入的并行RGB数据转换成串行数据时要使用移位寄存器)。

像素时钟信号是传输数据和对数据信号进行读取的基准。

待机控制信号(POWER DOWN):

当此信号有效时(一般为低电平时),将关闭LVDS发送芯片中时钟PLL锁相环电路的供电,停止IC的输出。

数据取样点选择信号:

用来选择使用时钟脉冲的上升沿还是下降沿读取所输入的RGB数据。

有的LVDS发送芯片可能并不设置待机控制信号和数据取样点选择信号,但也有的除了上述两个控制信号还设置有其他一些控制信号。

5.LVDS发送芯片的输出信号

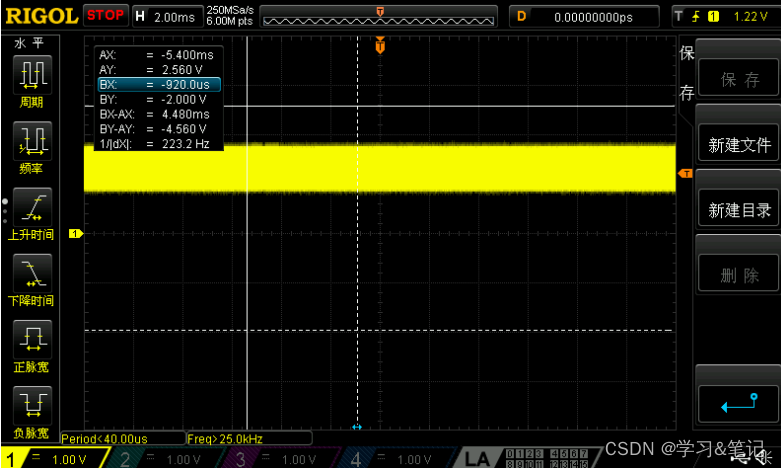

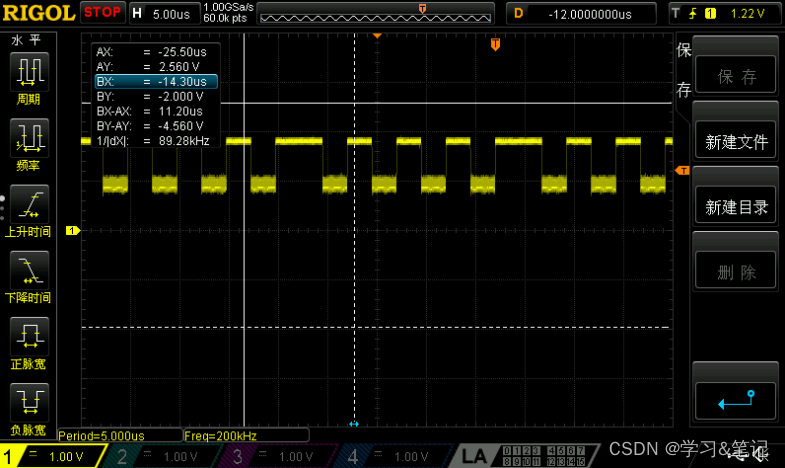

时钟信号输出:

LVDS发送芯片输出的时钟信号频率与输入时钟信号(像素时钟信号)频率相同。

时钟信号的输出常表示为:TXCLK+和TXCLK-,时钟信号占用LVDS发送芯片的一个通道。

CLK_N = RGB_B2

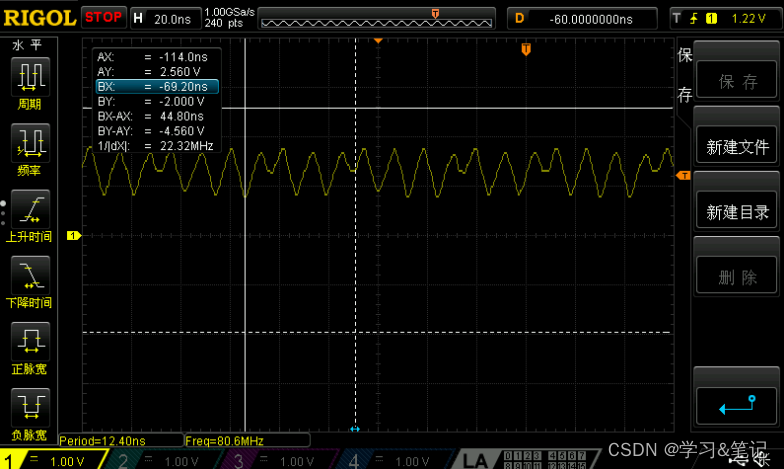

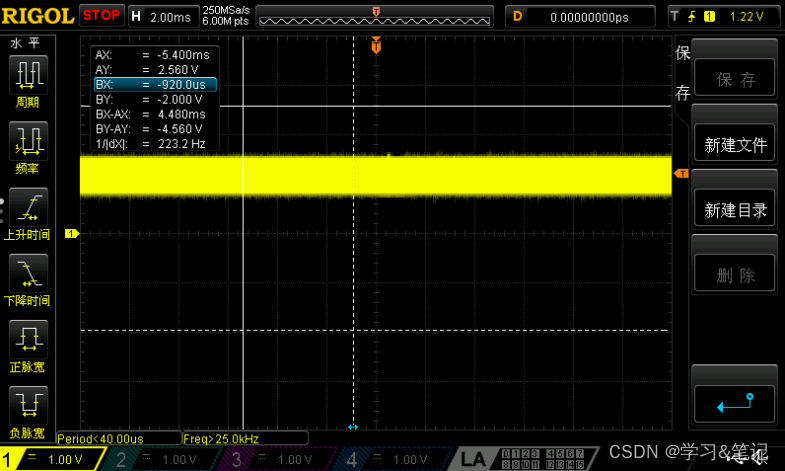

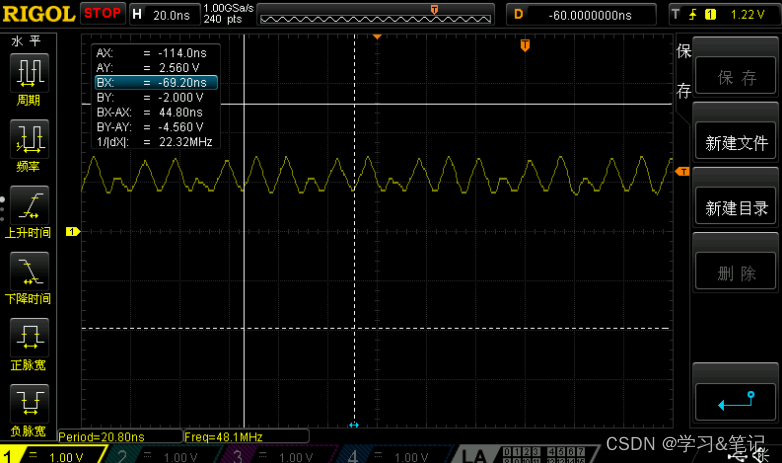

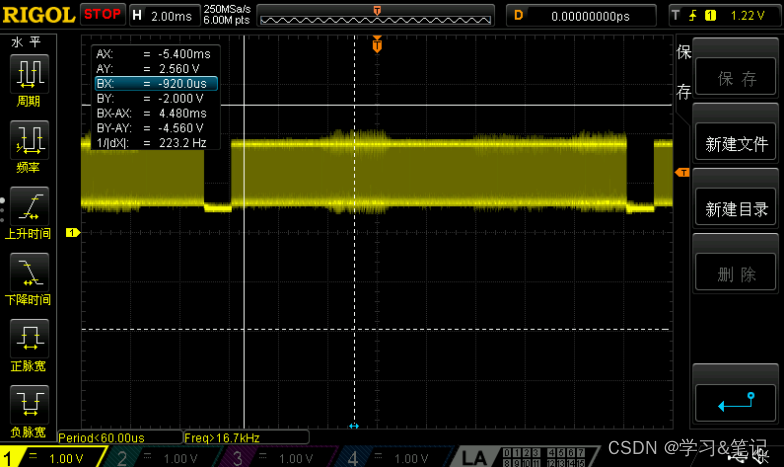

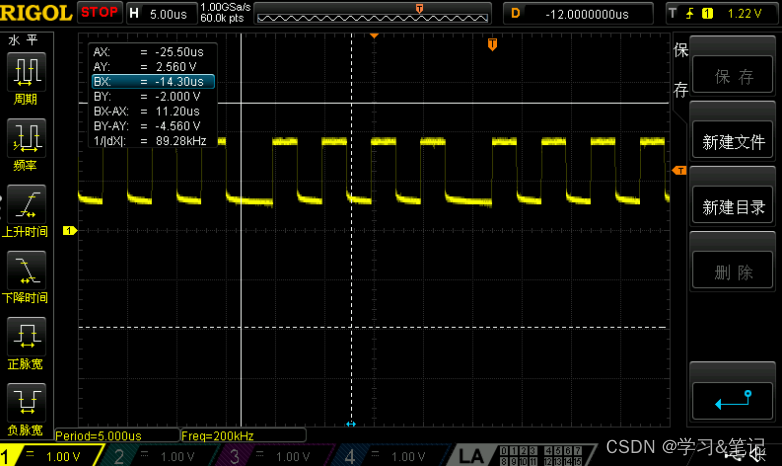

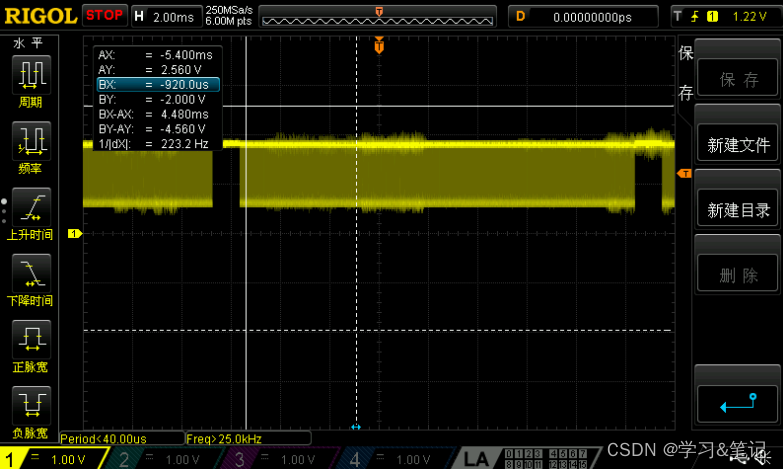

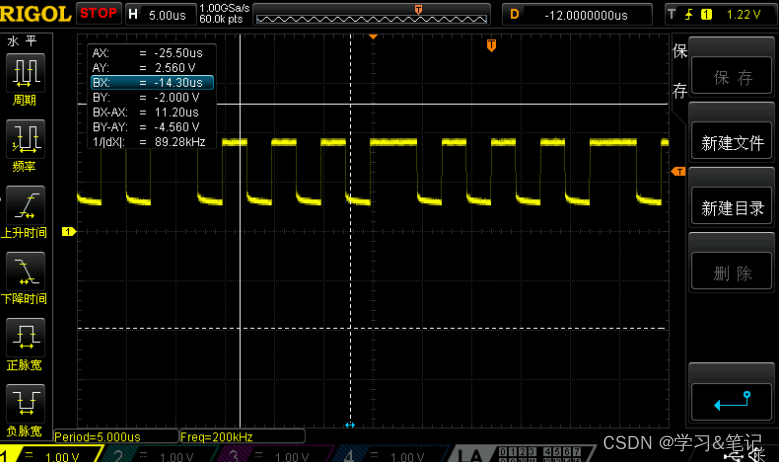

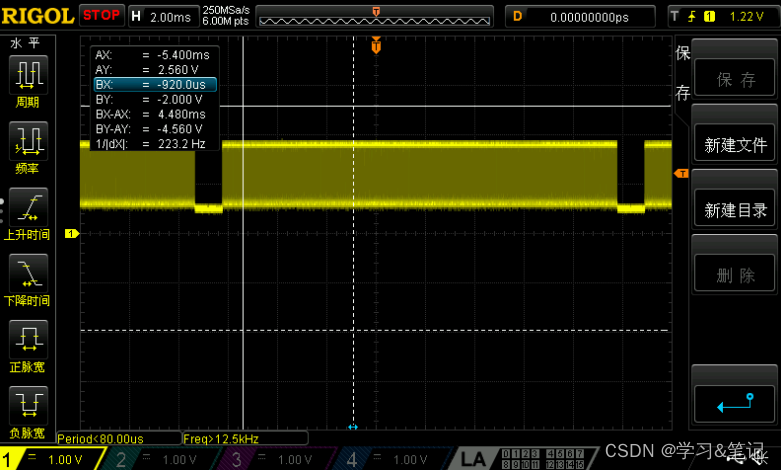

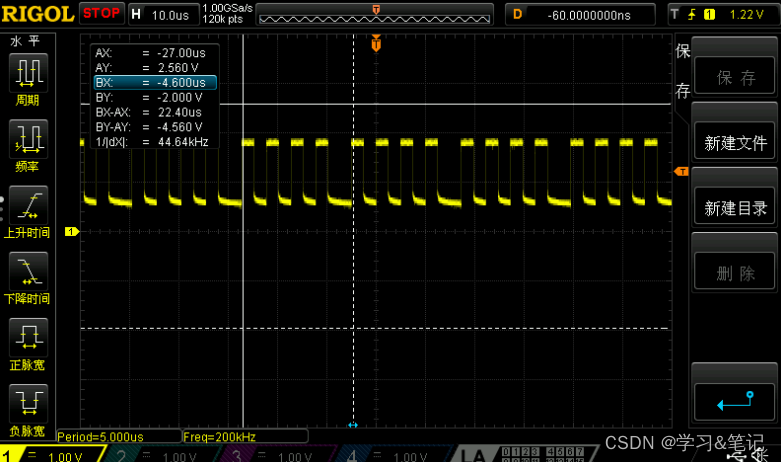

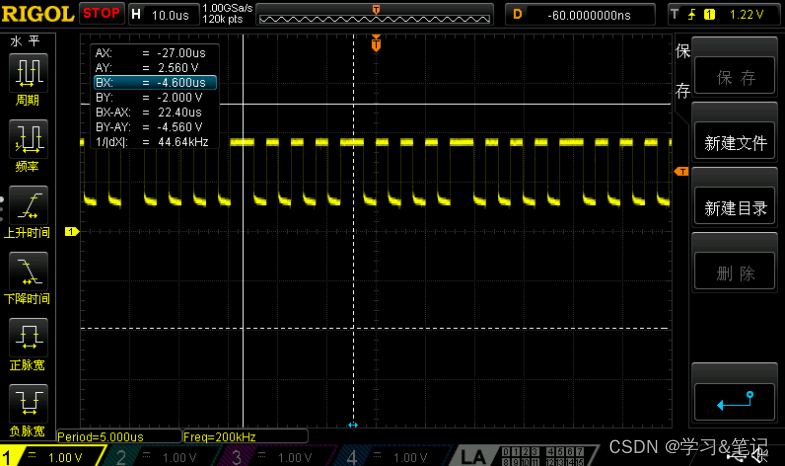

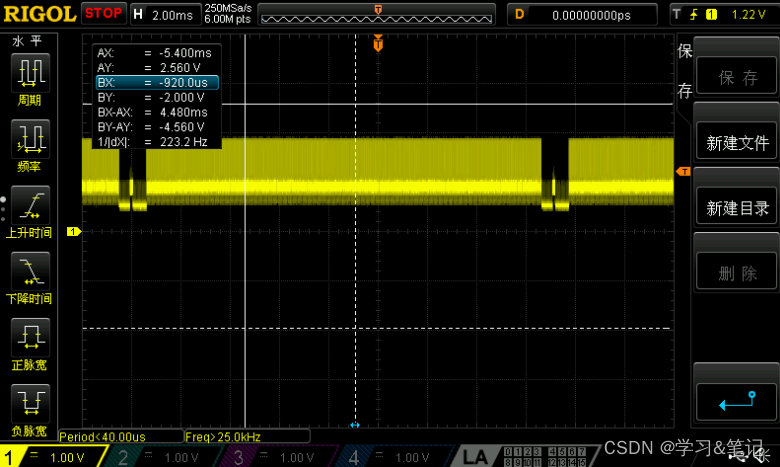

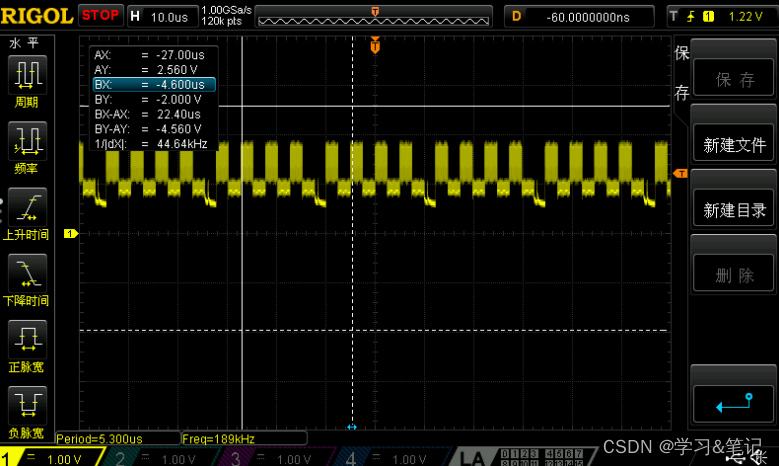

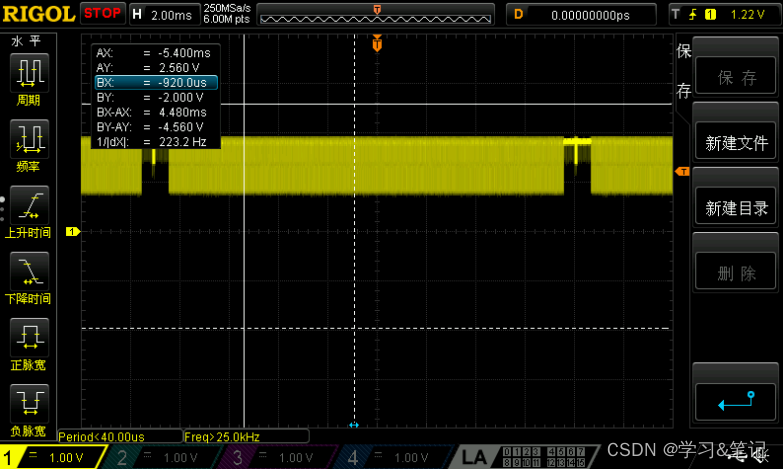

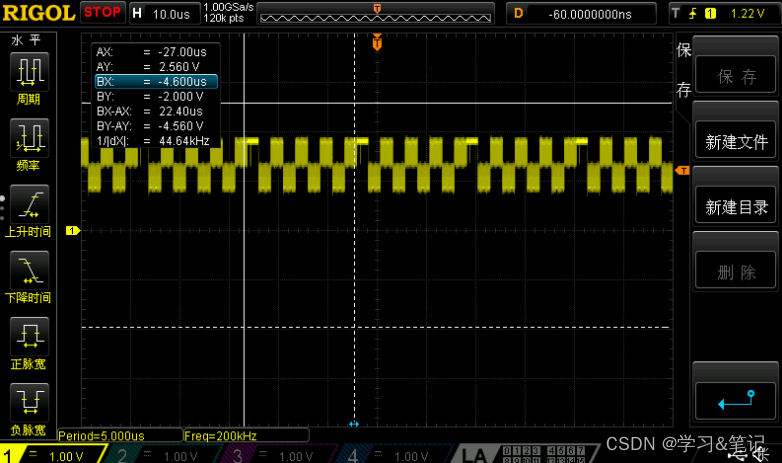

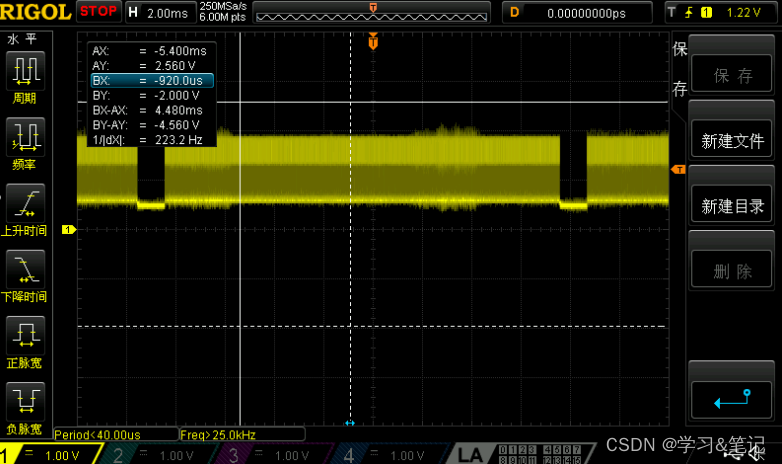

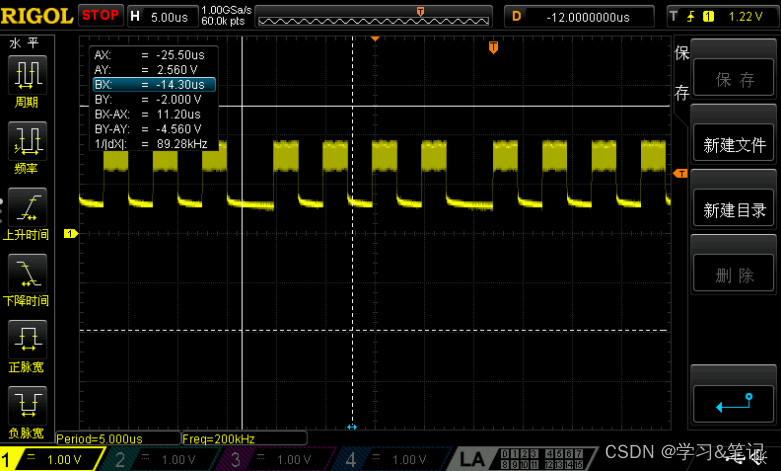

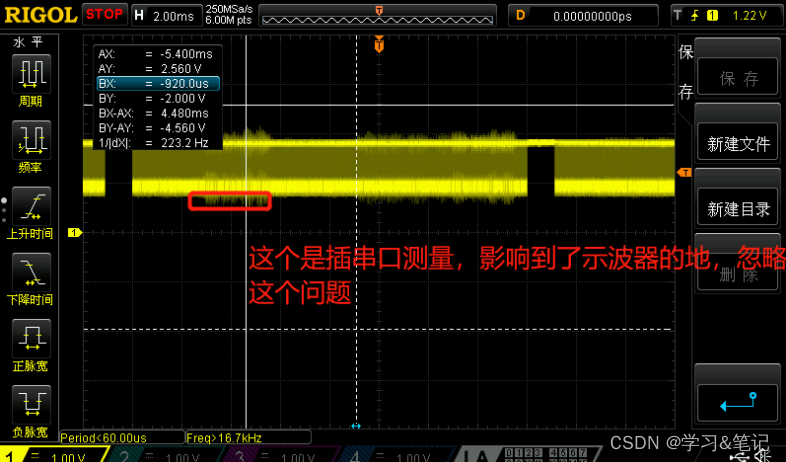

看lvds时钟信号的时候,看信号的波形是否正常,波形的振幅是否正常,不正常会出现图像传输不完整或者没接收到图像。

V3_P = RGB_B3

V4_N = RGB_B4

V4_N = RGB_B4

V5_P = RGB_B5

V5_P = RGB_B5

V6_N = RGB_B6

V6_N = RGB_B6

V7_P = RGB_B7

V7_P = RGB_B7

V8_N = RGB_B8

V9_P = RGB_G9

V9_P = RGB_G9

V10_N = RGB_G10

V10_N = RGB_G10

6.内核打印lvds输出日志

6.内核打印lvds输出日志

- [root@kunos ~]# dmesg | grep -iE "cfg_|lvds|disp"

- [ 2.309518] cfg_usrTiming outType:5 pclk:64000 h_a:1280 v_a:720 h_b:100 v_b:25 h_fp:40 v_

- [ 2.309666] cfg_usrTiming h_spw:4 v_spw:5 h_pol:1 v_pol:1 v_phase:0 rotate:

- [ 2.309782] cfg_usrTiming hv_pol:3 h_t:1424 v_t:770 h_blank:144 v_blank:50 lcd_hbp:104 lc

- [ 2.366863] [DISP]disp_module_init [ 2.432274] 64 [1280 x 720] 104 4 1424 30 5 770 [0 3] 0 lvds_colordepth=0 lvds_if=0 lv [ 2.453547] [DISP] Fb_copy_boot_fb,line:1787:

- [ 2.460034] in disp_al_lcd_get_clk_info():142 src_clk=448 tcon_div = 7

- [ 2.462466] [DISP]disp_module_init finish [ 2.467492] in disp_al_lcd_get_clk_info():152 src_clk=512 tcon_div = 8

- [ 2.475170] in disp_al_lcd_get_clk_info():152 src_clk=576 tcon_div = 9

- [ 2.486248] in disp_al_lcd_get_clk_info():142 src_clk=448 tcon_div = 7

- [ 2.493641] in disp_al_lcd_get_clk_info():152 src_clk=512 tcon_div = 8

- [ 2.501074] in disp_al_lcd_get_clk_info():152 src_clk=576 tcon_div = 9

- [ 2.511888] in disp_al_lcd_get_clk_info():142 src_clk=448 tcon_div = 7

- [ 2.519309] in disp_al_lcd_get_clk_info():152 src_clk=512 tcon_div = 8

- [ 2.526736] in disp_al_lcd_get_clk_info():152 src_clk=576 tcon_div = 9

- [ 2.537755] [DISP] disp_sys_power_enable,line:486:

- [ 2.537770] [DISP] disp_lcd_pin_cfg,line:1108:

- [ 2.537777] lcd 0 pin config, state lvds_on, 1 lvdsused=1

- [ 2.795774] [DISP] disp_device_attached_and_enable,line:223:

- [ 2.795795] [DISP] disp_device_attached_and_enable,line:236:

- [ 3.129922] [DISP] disp_device_attached_and_enable,line:223:

- [ 3.129938] [DISP] disp_device_attached_and_enable,line:236:

7.LVDS发送芯片输出信号的格式

LVDS发送芯片输出信号的格式,即LVDS发送芯片输入的RGB数据,以及行同步信号HS、场同步信号VS、有效显示数据使能信号DE在各个输出通道中数据位的排列顺序。

由于几个大的LYDS芯片生产厂家制定了不同的标准,因此,存在着几种不同的LVDS发送芯片数据输出格式,在更换液晶显示器驱动板或更换液晶面板时,必须弄清LVDS接口液晶面板所要求的LVDS信号格式,使液晶显示器驱动板侧LVDS发送芯片的输出数据格式与液晶面板LVDS接收芯片所要求的数据格式相同。

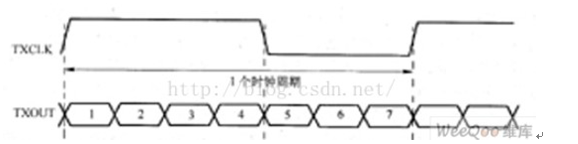

LVDS发送芯片在一个时钟脉冲周期内,每个数据通道都输出7bit的串行数据信号,而不是常见的8bit数据,如下图所示:

以8bit RGB显示屏接口为例,每个显示周期需要传输8bit的R信号,8bit的G 信号,8bit 的B信号,及VS,HS,DE信号,总共为27 BIT。而每对LVDS信号线在一个TX周期里只能传输7BIT数据,所以需要4 对数据线,外加一对时钟线。

LVDS并串转换如下图所示:

LVDS的格式会影响显示的效果,格式不对,图像可以显示出数据,但是显示的效果不好。