热门标签

热门文章

- 1git clone 443解决方案

- 2AIGC 助力电商虚拟试穿新体验

- 3内联函数、构造函数、静态成员函数不可以定义为虚函数_内联函数,静态成员函数,构造函数能是虚函数吗

- 4植物大战僵尸杂交版2.1最新版本详细下载安装步骤教程

- 5Python绘制矩形_用python绘制矩形信号

- 6鸿蒙应用开发之调用C++开发代码库2_纯血鸿蒙arkts开发调用c++ so

- 7burpsuite全套使用教程_burpsuite详细教程

- 808_ZYNQ7020_新建驱动文件、编译_正点原子zynq7020电机驱动器

- 9Docker环境搭建安卓打包环境_android sdk docker

- 10解密金融行业数据云平台建设密码_金融密码服务

当前位置: article > 正文

ZYNQ学习专栏(PS)_zynq ps端调试时怎么查看变量的值

作者:正经夜光杯 | 2024-07-06 03:36:23

赞

踩

zynq ps端调试时怎么查看变量的值

目录

(本文资料来源于网络以及自己的总结,学到哪更到哪,无商业用途,侵删)

PS与PL的数据交互

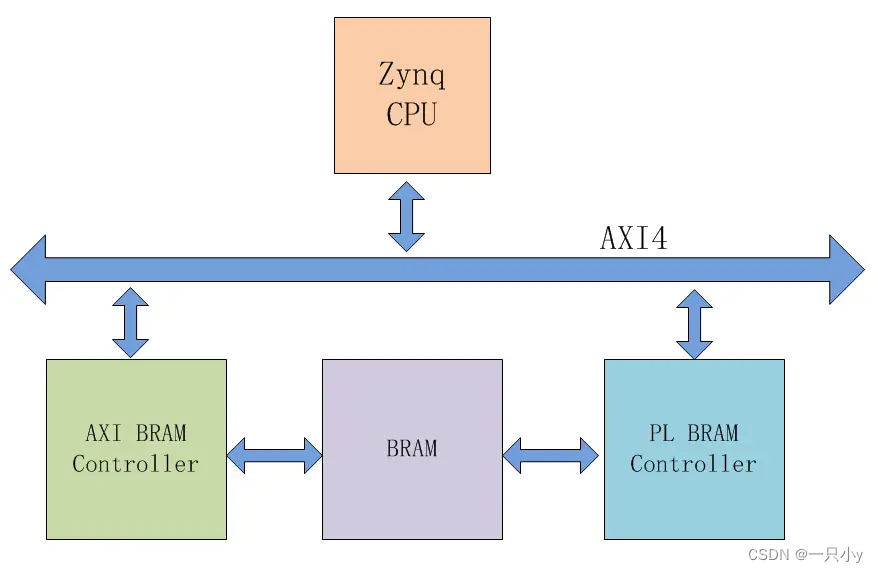

通过BRAM进行数据交互

主要是画个BD,里面加个axi_bram_controller(完成AXI接口至BRAM接口的转换)和双端口的block_Memorry_Gen模块,PS那边通过AXI接口使用controller来控制bram的读写,PL这边就用bram的另一个端口(一般是PORTB)来读写bram。因为bram_control那边会进行地址分配,所以SDK里面的代码对相应地址进行读或者写,也就和PL里面的那些input output差不多了我感觉。

![]()

这里bram_controller的AXI-full协议位宽设置的是32位,因为AXI协议规定一个地址存储8位数据,那么 位宽×深度/8=地址数,也就是说地址分配8k的话可以存储2048个32位的数据。

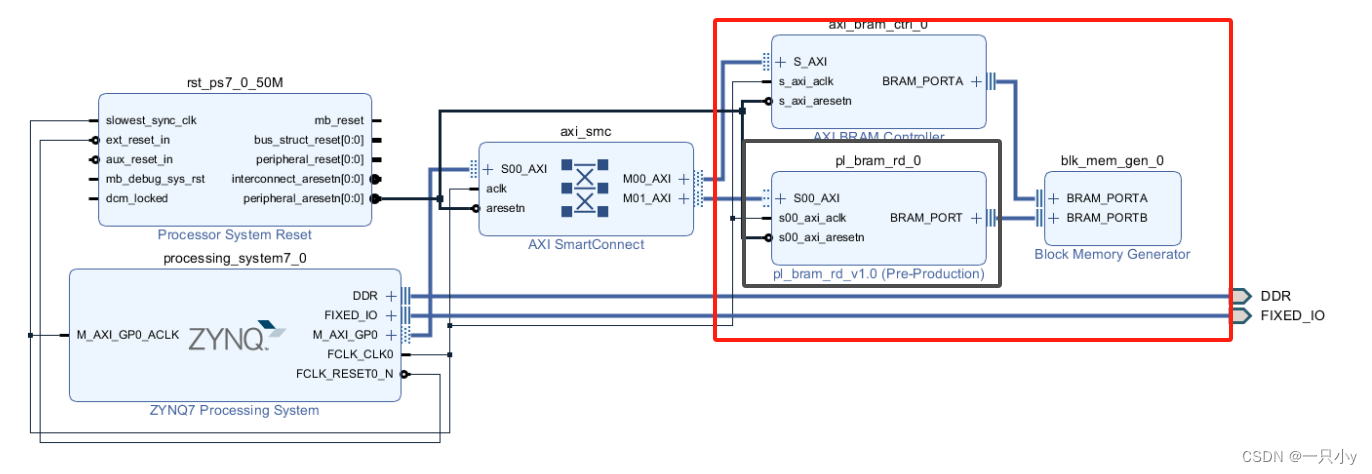

最后BD的图大概就是红色框框里这样,黑色框框的rd模块可以不要,也可以直接在pl代码里例化了system之后自己写bram的读写时序。

BRAM读写时序以及工作模式

关于bram的读写时序,分写优先、读优先和不变模式,看到一篇写的很好的csdn,先码在这:

XILINX BMG (Block Memory Generator)-CSDN博客

总结来说就是三个工作模式

- 写优先(写状态时先把数据同时写入地址和输出总线)

- 读优先(写状态下先把地址中以前的数据读出到输出总线上再把新的数据写入地址内)

- 不变模式(当在往 RAM 里面写的时候,DOUTA 读出的数据保持不变,一直为 aa 的内容,直到 WEA 被拉低,重新进入 READ 模式)

具体单双真的模型就不列出了,大概的读写流程是:

- CLKA 为输入的时钟信号,时钟上升沿对数据进行写入/读出

- DINA 为写入的数据总线

- DOUTA 为读出的数据总线

- ADDRA 为地址总线

- ENA 为使能端,当 ENA 为 1 的时候,可进行读写操作,ENA 为 0 的时候,无法进行读写

- WEA 为写使能,当 ENA 为 1 同时 WEA 为 0 的时候,为读操作;当 ENA 和 WEA 同时为 1 的时候,为写操作;

————————————————

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/zhoutaopower/article/details/105257499

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/正经夜光杯/article/detail/791702

推荐阅读

相关标签