热门标签

热门文章

- 1NVIDIA 安装 CUDA_nvidia cuda

- 2Java入门(一)——Java循环语句之 while (4-6)_用while循环求6代码java

- 3特斯拉擎天柱机器人:工厂自动化的未来

- 4docker 搭建服务中心etcd、nacos_etcd何nacos

- 5基于Java+SpringBoot+Vue+Uniapp奶茶在线下单小程序设计与实现(源码+lw+部署文档+讲解等)_基于springboot的奶茶点单系统的设计与实现

- 6玩转Mysql系列 - 第23篇:mysql索引管理详解

- 7华为手机刷linux系统,华为Harmony OS 2.0手机Beta版刷机包流出:电脑助手一键刷入/手动...

- 8A*算法原理与实现(python)_python a*

- 9手把手教你使用docker-compose搭建RabbitMQ集群_docker-compose 安装rabbitmq集群

- 10数据分析中常用的数据模型

当前位置: article > 正文

用译码器来设计组合逻辑电路_译码器设计全加器

作者:盐析白兔 | 2024-05-13 12:05:06

赞

踩

译码器设计全加器

三线到八线:输入端只有三个所以只能是三变量

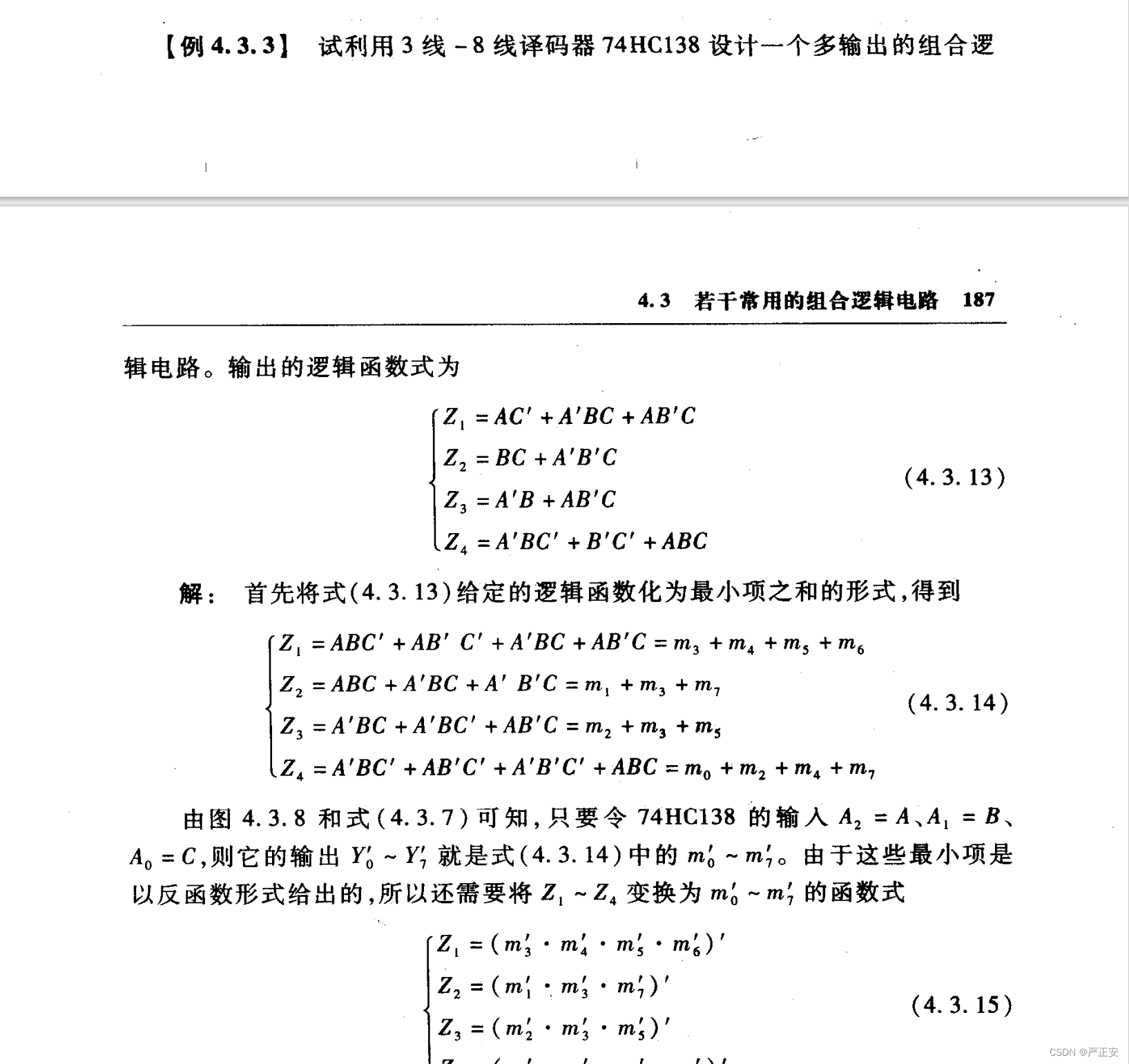

我们先来看书上的一个例子

设计的过程第一步

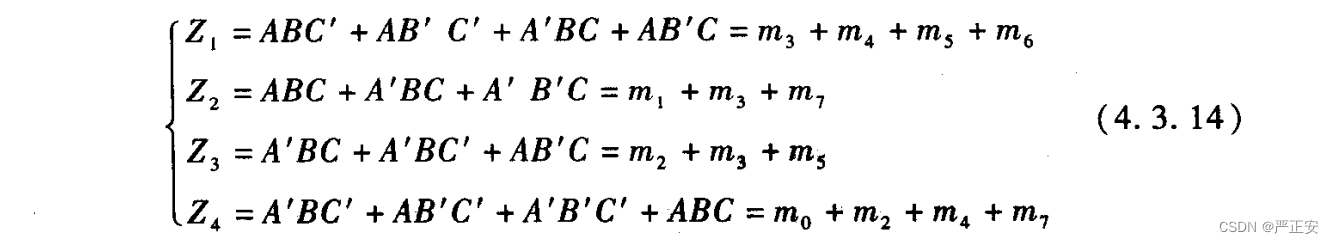

将函数表达式整理成最小项和的形式

我们用来举例,不是最小项的形式

三变量函数可以用三变量的最小项来表示

为了看的更清楚,我们写成最小项的编号,这样子更好看

这个时候,我们还需要做变化,两次取反

译码器的输出作为与非门的输入

我们在译码器输出之后,拿起来做一个与非门的组合

我们要根据选择的器件来变

所以在这里才会去做这样子的一个变换

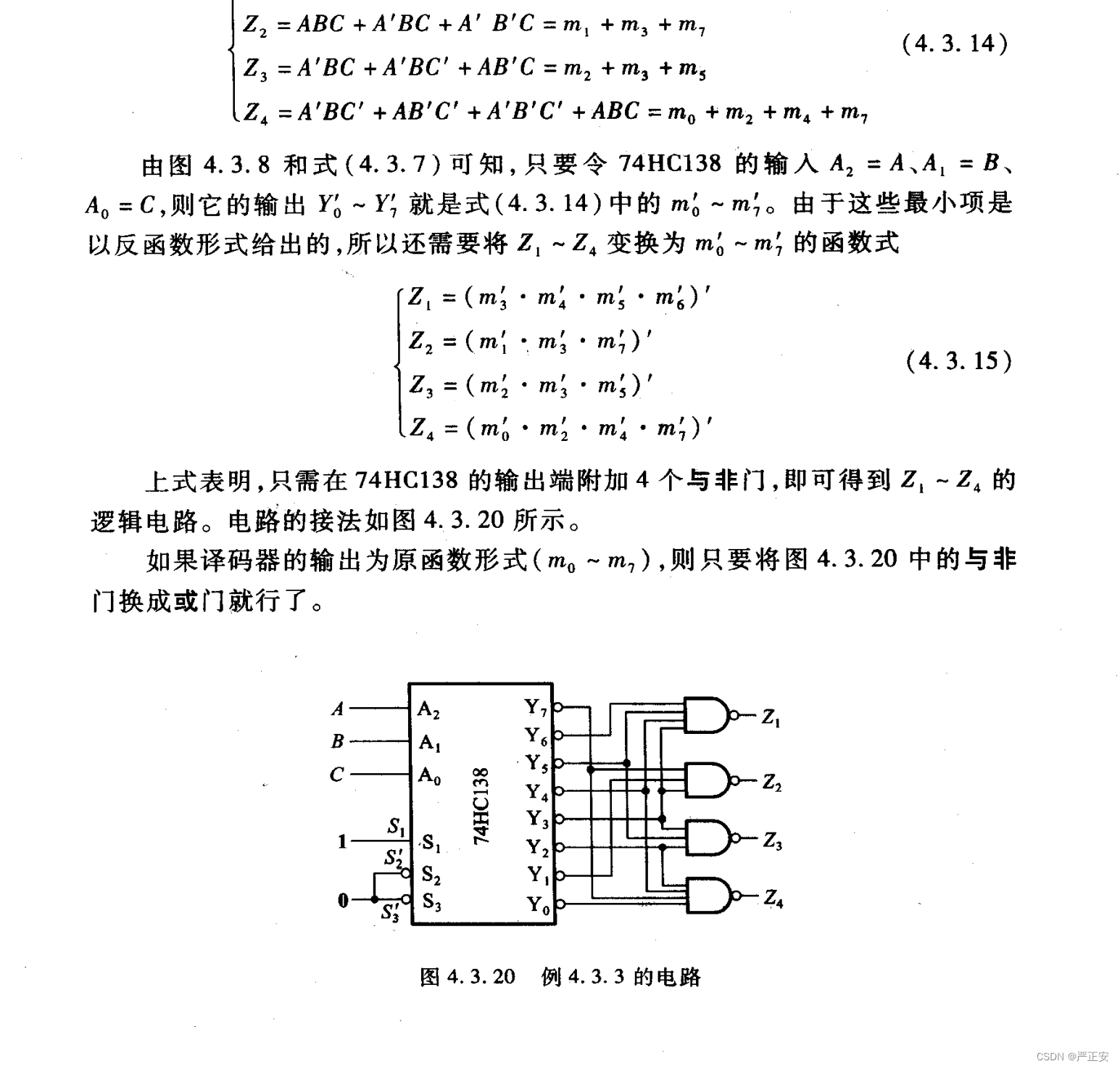

当这个表达式出来以后,剩下就是画电路图

外部需要标识符

这样子才是规范的连接方式

我们接下来看一个

完整的例子

例子:用74HC138 设计一个移位全加器电路

全加器:除了考虑加法,还要考虑进位

输入信号有三个:两个加数,来自于低位的进位

输出有两个信号:一个是和,还有一个是产生的进位

因为是一个算数运算,零进来时零,一进来是一,接下来我们就需要列真值表

首先判断可行性,三变量所以138没有问题

首先列出真值表,三个输入,两个输出

所以可以用译码器来设计全加器

利用最小项译码的特点非常方便,可以完成组合译码器的设计,一定要针对译码器这样的一个电路特点来进行变换

一定要记住译码器输出和最小项之间的关系

Y-》m 相当于完成了从输出端到输入端的一个转换

推荐阅读