- 1C/C++中extern的作用_c++ extern有什么用

- 2Android科大讯飞TTS语音合成实例详细步骤_科大讯飞 tts文档

- 3OSG中几何体的绘制(二)_结果限定为构造几何结构对象,该对象可能将点与多个几何体共享。请检查结果。

- 4第二个鸿蒙入门应用页面跳转_鸿蒙3.0 应用跳转设置

- 5音视频--DTMF信号发送及检测_dtmf拨号判读 csdn

- 6vscode + vite + vue3 + typescript + eslint 项目配置_vscode 配置vue3和typescript环境

- 7Qt on Android:图文详解QT开发Andriod入门,Hello World全过程

- 8BigDecimal 的加减乘除运算以及除法保留两位小数_bigdecimal乘法

- 9Linux初级知识大全(一)

- 10SharedPreference使用的正确姿势_sharedpreference使用场景

FPGA采集CameraLink相机Full模式解码输出的实现设计方案_fpga实现cameralink

赞

踩

FPGA采集CameraLink相机Full模式

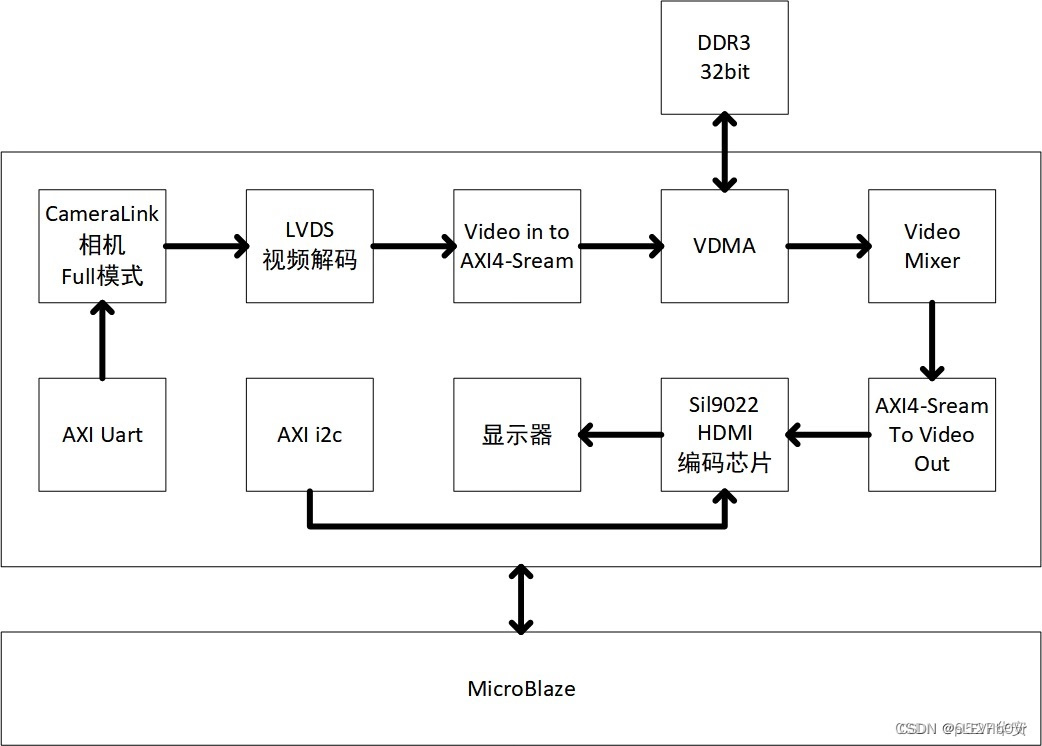

本文详细描述了FPGA采集CameraLink相机Full模式解码输出的实现设计方案,思路是这样的,CameraLink相机输入到FPGA板子,FPGA使用内部逻辑资源实现LVDS视频解码,解析出像素时钟、行同步信号、场同步信号、数据有效信号、以及像素数据,然后将视频转为Xilinx的AXI4-Sream的视频流,经VDMA送入DDR3缓存,然后读取出视频再经过AXI4-Sream to Video Out通过HDMI接口输出视频,这是Xilinx图像处理常用的套路,可谓相当精巧的方案

FPGA采集CameraLink相机Full模式下的解码输出实现设计方案

摘要:

本文详细描述了FPGA采集CameraLink相机Full模式解码输出的实现设计方案。该设计方案通过将CameraLink相机的输入连接至FPGA板子,并利用FPGA内部逻辑资源实现LVDS视频解码,解析出像素时钟、行同步信号、场同步信号、数据有效信号以及像素数据。随后,视频流会被转换为Xilinx的AXI4-Stream视频流,并通过VDMA传输到DDR3缓存中。最后,通过AXI4-Stream to Video Out接口,通过HDMI输出视频。该方案是Xilinx图像处理中常用的套路,具备高度精巧性。

介绍:

相机作为图像采集设备的重要组成部分,广泛应用于各行各业。在FPGA领域,利用FPGA来采集CameraLink相机Full模式的视频信号,并经过解码输出,是一项具有挑战性的任务。本文将从硬件设计的角度,详细描述这一过程中的关键步骤和设计方案。

1. FPGA实现LVDS视频解码

首先,将CameraLink相机的输出信号连接至FPGA板子。通过FPGA内部逻辑资源,实现对LVDS视频信号的解码。解码后,获得像素时钟、行同步信号、场同步信号、数据有效信号以及像素数据。这些信号对于后续的视频处理非常关键。

2. 视频流转换为AXI4-Stream格式

获得相机输出的视频信号后,需要将其转换为Xilinx的AXI4-Stream格式。这一步骤可以通过FPGA内部逻辑资源实现。AXI4-Stream是一种具有固定数据帧和信号标准的视频流协议。将视频信号转换为AXI4-Stream格式后,可以方便地进行后续的处理和传输。

3. 视频流传输到DDR3缓存

为了高效地处理视频流,需要将其传输到DDR3缓存中。这一步骤可以通过使用VDMA(Video Direct Memory Access)模块实现。VDMA模块能够将视频流直接传输到DDR3缓存中,从而减轻FPGA的负担,提高整体性能。

4. 通过HDMI输出视频

最后,通过使用AXI4-Stream to Video Out接口,将DDR3缓存中的视频数据传输至HDMI输出接口。这一步骤可以实现将处理后的视频信号展示到外部显示器上。HDMI接口是常见的视频输出接口,具有广泛的兼容性和易用性。

总结:

通过本文所描述的FPGA采集CameraLink相机Full模式解码输出的实现设计方案,可以实现高效且精准地从CameraLink相机中采集视频信号,并通过FPGA进行解码处理和输出。该方案利用了FPGA的内部逻辑资源,实现了LVDS视频解码、AXI4-Stream视频流转换、VDMA视频流传输以及HDMI视频输出等关键步骤。通过以上步骤的有机组合,可以实现对CameraLink相机Full模式下的视频信号进行高质量的采集和处理。

参考链接:

详细设计文档参考链接:[链接已删除]

注意:本文所提供的链接可能不再有效,请读者自行搜索相关资料获取更多信息。本文仅对FPGA采集CameraLink相机Full模式下的解码输出实现设计方案进行了描述,并未涉及具体代码实现和参考文献。

相关代码,程序地址:http://imgcs.cn/lanzoun/721343787341.html