热门标签

热门文章

- 1聊聊 Kafka: 在 Linux 环境上搭建 Kafka_kafka的持久化存储在linux上是哪一个路径

- 2Python 第三方库大全_python第三方库列表

- 3让机器学习助力医疗领域

- 4计算机组成原理:输入、输出系统(一)_crt的分辨率为1024*512像素,像素的颜色数为256,则刷新存储器的容量为

- 5《网络是怎样连接的》——第二章笔记_协议栈到网卡都是单线程在处理吗

- 6XSS注入——反射性XSS_反射型xss攻击方式的攻击过程

- 7基于matlab的图像去噪算法设计与实现_图像降噪研究现状

- 8java后端部署一般需要选择什么服务器?_后端常用服务器

- 92022/6/15 docker安装与项目部署(入门教程)_docker部署项目

- 10基于Java+Vue+uniapp微信小程序宿舍报修系统设计和实现

当前位置: article > 正文

vivado VIO IP的用法_vio的时钟最小多少

作者:知新_RL | 2024-06-11 18:28:49

赞

踩

vio的时钟最小多少

vivado VIO IP的用法

0 程序功能

通过VIO模拟按键来控制DDS的频率控制字,从而得到不同频率的正弦波。

程序结构

必须要通过ILA才能模拟VIO,testbench不能模拟VIO。

1 IP核的例化

1.1 VIO IP的例化

vio_0 your_instance_name (

.clk(clk), // input wire clk

.probe_out0(probe_out0) // output wire [1 : 0] probe_out0

);

- 1

- 2

- 3

- 4

1.2 DDS IP

dds_sin your_instance_name (

.aclk(aclk), // input wire aclk

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(s_axis_config_tdata), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata), // output wire [47 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata) // output wire [23 : 0] m_axis_phase_tdata

);

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

2 程序

2.1 程序结构

2.2 顶层模块

`timescale 1ns / 1ps module top( input sys_clk ,//系统时钟 50MHz T=20ns input rst_n //系统复位 ); // -----------0、VIO按键控制频率控制字(key_PINC) wire [1:0] key_PINC; vio_0 vio_0_inst ( .clk(sys_clk), // input wire clk .probe_out0(key_PINC) // output wire [1 : 0] probe_out0 ); //---------------1、信号频率控制模块--------------// wire [23:0] Fword ; //频率字 Fword_set Fword_set_inst( //input .clk (sys_clk ), .rst_n (rst_n ), .key_PINC (key_PINC ), //output .Fword (Fword ) ); //---------------2、DDS模块--------------// //input wire [0:0] fre_ctrl_word_en ; //output wire [0:0] m_axis_data_tvalid ; wire [47:0] m_axis_data_tdata ; wire [0:0] m_axis_phase_tvalid ; wire [23:0] m_axis_phase_tdata ; assign fre_ctrl_word_en=1'b1; //例化DDS IP dds_sin dds_sin_inst ( .aclk (sys_clk ), // input wire aclk .s_axis_config_tvalid (fre_ctrl_word_en ), // input wire s_axis_config_tvalid .s_axis_config_tdata (Fword ), // input wire [23: 0] s_axis_config_tdata .m_axis_data_tvalid (m_axis_data_tvalid ), // output wire m_axis_data_tvalid .m_axis_data_tdata (m_axis_data_tdata ), // output wire [47 : 0] m_axis_data_tdata .m_axis_phase_tvalid (m_axis_phase_tvalid ), // output wire m_axis_phase_tvalid .m_axis_phase_tdata (m_axis_phase_tdata ) // output wire [23 : 0] m_axis_phase_tdata ); ila_1 ila_1_inst ( .clk(sys_clk), // input wire clk .probe0(key_PINC), // input wire [1:0] probe0 .probe1(Fword), // input wire [23:0] probe1 .probe2(m_axis_data_tdata) // input wire [47:0] probe2 ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

2.3 Fword_set模块

`timescale 1ns / 1ps // // 通过按键来选择对应的频率控制字,进而选择对应的信号频率 // module Fword_set( input clk , input rst_n , input [1:0] key_PINC , output reg [23:0] Fword ); //always@(posedge clk or negedge rst_n) //begin // if(!rst_n) // key_sel <= 4'd0; // else // key_sel <= key_sel; //end // The output frequency(f_out ) , of the DDS waveform is a function of the system clock frequency(f_clk ) . // the phase width, that is, number of bits (B ) in the phase accumulator // and the phase increment value (deta_theta) . // The output frequency in Hertz is defined by:f_out=f_clk*deta_theta/(2^B) // fre_ctrl_word是如何确定的? // 根据IP核的summery, phase width=20bits Frequency per channel=100MHz // 输出频率的计算公式f_out=f_clk*deta_theta/(2^B)=100M* 104857/(2^20 )= 10M always@(*) begin case(key_PINC) 0: Fword <= 'h28f5; //1Mhz 10485 每次相位增加的值 deta_theta 1: Fword <= 'h51eb; //2Mhz 20971 2: Fword <= 'ha3d7; //4Mhz 41943 3: Fword <= 'h19999; //10Mhz 104857 endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

2.4 约束文件

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN J16 [get_ports rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

#时序约束

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

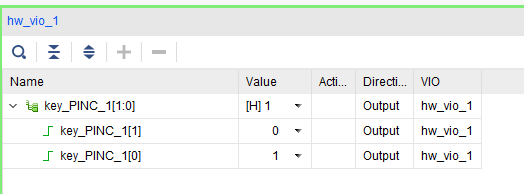

3 结果

key_PINC=0(2’b01)

key_PINC=2(2’b10)

声明:本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:【wpsshop博客】

推荐阅读

相关标签