热门标签

热门文章

- 1RocketMq集群安装&整合Springboot_rocketmq springboot多个namesrv 怎么订阅

- 2Python:关于创建字典的4种方式_python创建字典

- 32024-5-15

- 4金融与大模型:引领行业未来的创新融合

- 5AMEYA360代理品牌:ROHM开发出世界超小CMOS运算放大器,适用于智能手机和小型物联网设备等应用

- 6HDFS Disk Balancer_hdfs diskbalancer

- 7Centos7配置Hadoop出现Permission denied (publickey,gssapi-keyex,gssapi-with-mic,password)的解决

- 8RocketMQ 第一章 核心功能 4 消息发送样例 4.5 批量消息_rocketmq批量发送 指定队列

- 9linux下使用libusb获取系统usb设备具体信息_libusb 对应

- 10java hutool工具类处理json的常用方法_hutool json字符串转map

当前位置: article > 正文

3-8译码器和8-3编码器VHDL_38译码器vhdl

作者:知新_RL | 2024-06-12 11:21:09

赞

踩

38译码器vhdl

- 实验内容

1) 熟悉quartusll开发环境

2) 3-8译码器和8-3编码器

3) 用VHDL实现

二、实验目的

1) 熟悉quartusll开发环境

2) 3-8译码器和8-3编码器

3) 用VHDL实现

三、软件流程(硬件连接)

①新建工程

②将设计项目设置成可调用的元件

③编写代码,检查错误并改正

④尝试运行代码

⑤连接对应芯片的引脚

⑥将电脑与硬件连接

⑦在硬件上运行检验

四、代码

1)3-8译码器

2)8-3编码器

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL; --实体说明

-

- ENTITY basan IS

- PORT( IN1: IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入端

- OUT1: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); --输出端

- END;

-

- ARCHITECTURE ONE OF basan IS --结构体

- BEGIN

- PROCESS(IN1) --顺序执行

- BEGIN

-

- if IN1(7)='1' THEN OUT1<="111";

- ELSIF IN1(6)='1' THEN OUT1<="110";

- ELSIF IN1(5)='1' THEN OUT1<="101";

- ELSIF IN1(4)='1' THEN OUT1<="100";

- ELSIF IN1(3)='1' THEN OUT1<="011";

- ELSIF IN1(2)='1' THEN OUT1<="010";

- ELSIF IN1(1)='1' THEN OUT1<="001";

- ELSIF IN1(0)='1' THEN OUT1<="000";

- ELSE OUT1<="XXX";

- END IF;

- END PROCESS;

- end;

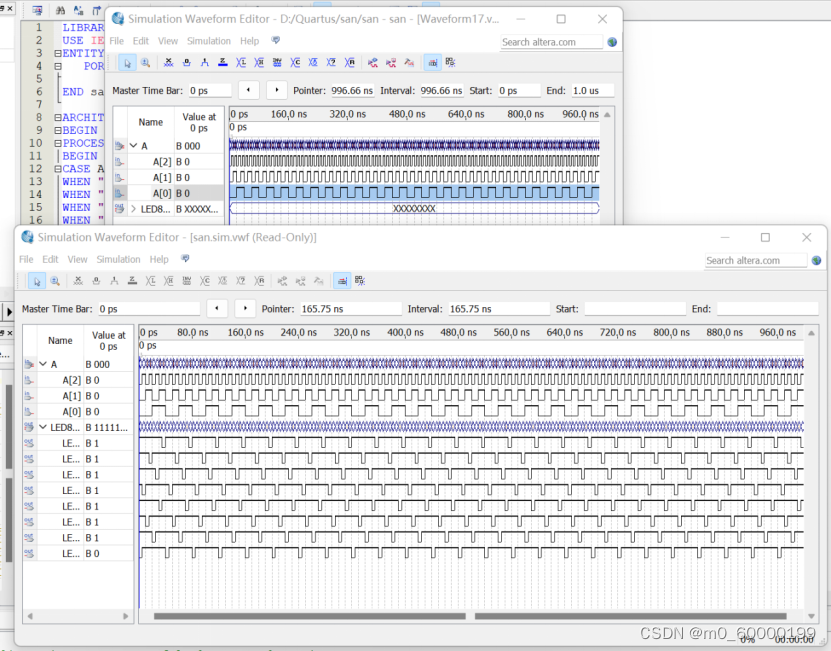

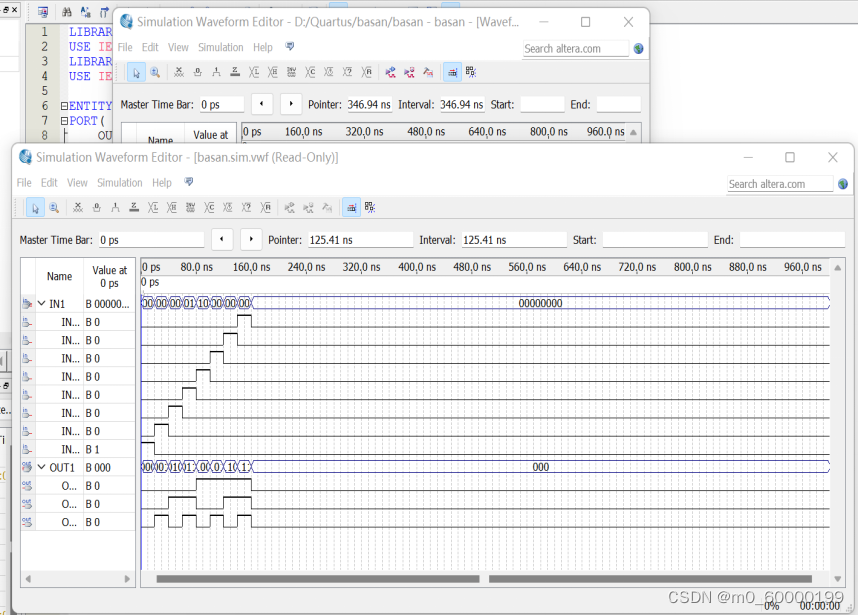

五、实验结果及分析

1)3-8译码器

2)8-3编码器

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/知新_RL/article/detail/707866

推荐阅读

相关标签