- 1基于一体化有序信息和事件关系的脚本事件预测_事件关系脚本学习

- 2idea git 合并多个commit_idea git合并多个commit

- 3关于def __init__(self)_def --init--

- 4字节跳动的真实工作体验_字节跳动稳定吗

- 5华为HCIP-Datacom认证题库(H12-821)_mqc与pbr一样,只能在设备的三层接口下调用

- 60.1## 梯度下降的优化算法,SGD中的momentum冲量的理解_sgd momentum如何取值

- 7将本地项目上传到GitHub_添加本地git代码到sourcetree

- 8基于Python+Django+Vue+Mysql前后端分离的图书管理系统_djangovue前后端分离图书馆

- 9基于JSP的图书销售管理系统_jsp 图书信息管理 博客

- 10Linux系统Docker部署DbGate并结合内网穿透实现公网管理本地数据库_docker安装基于web的数据库管理工具_dbgate docker

DDR官方例程读写仿真记录_ddr读写仿真

赞

踩

一、配置MIG控制器,理解MIG核的输入输出信号

1、配置MIG控制器

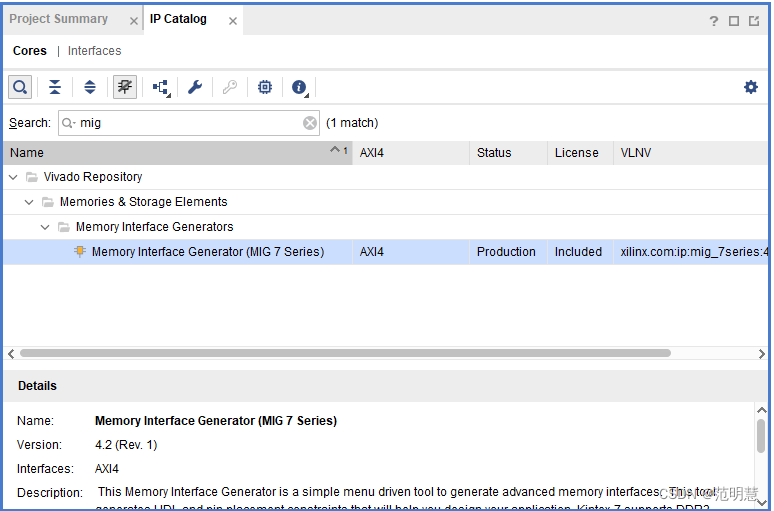

a、在 IP Catalog里搜索MIG,点击下方的Memory Interface Generator核

b、接下来是查看FPGA的器件,速度等级,语言等等,全部和工程一致

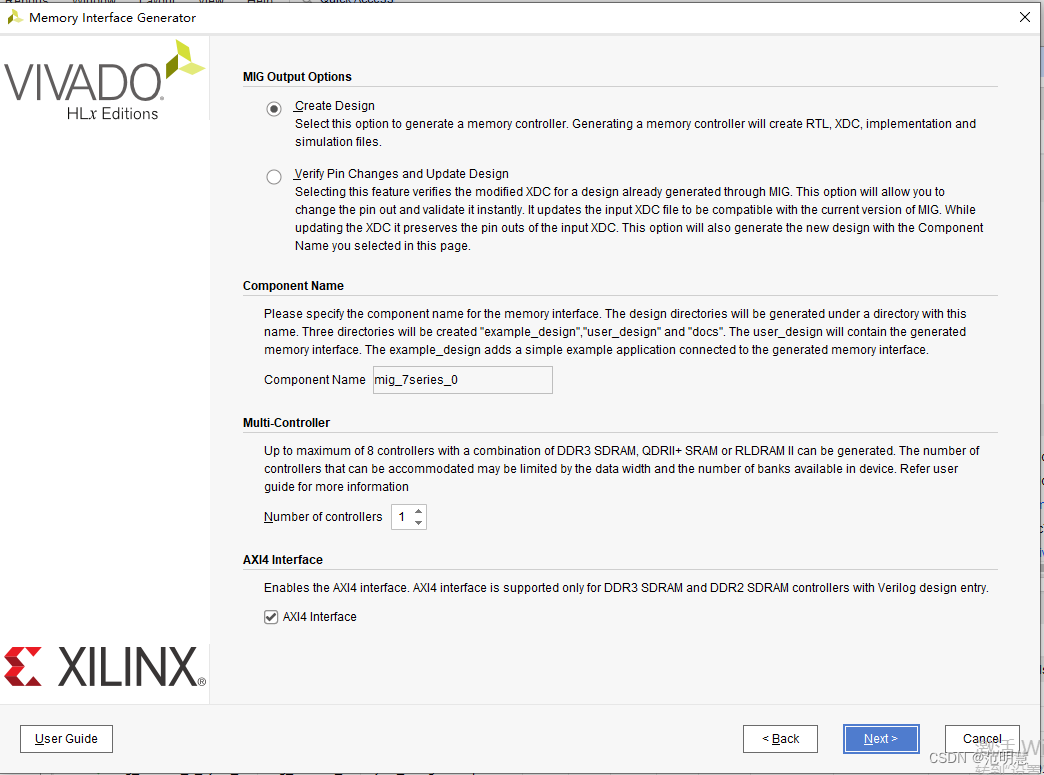

c、接下来勾选 Creat Design ,设计名称保持默认 mig_7series_0 ,底部勾选使用AXI4接口

d、之后是 兼容的FPGA型号选择(默认不选) 和 存储器类型选择DDR3

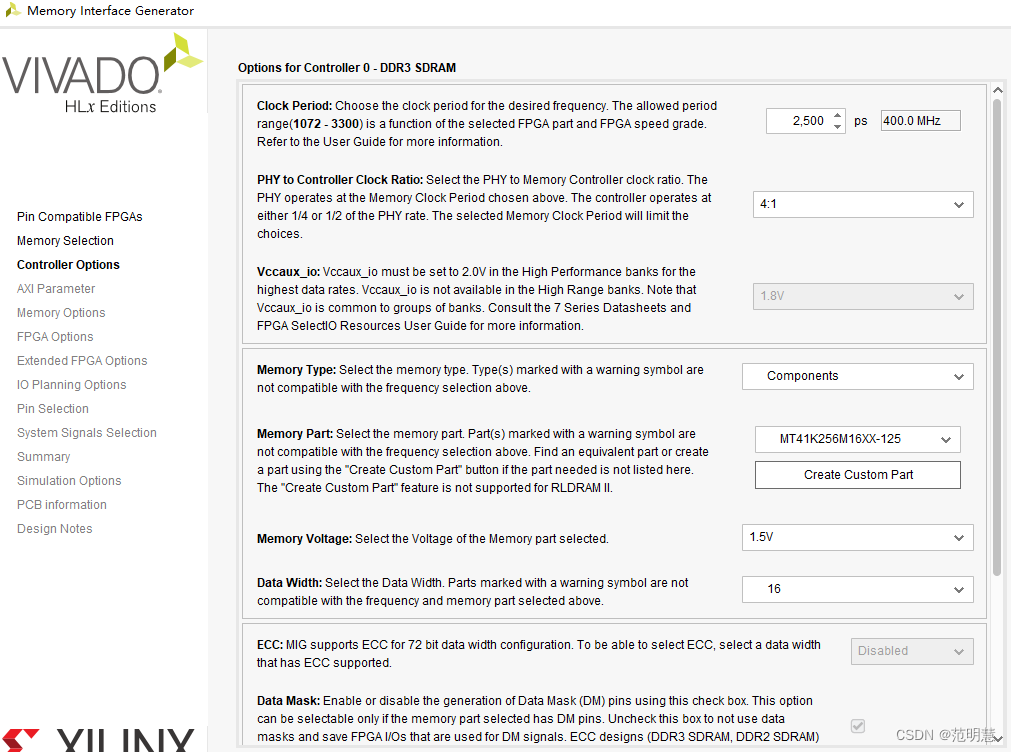

e、Controller Option

DDR时钟:(外部时钟)

选择400M----2500ps,这个时钟是输出给DDR储存器的驱动时钟,DDR芯片的IO时钟频率

表现是MIG的输出信号 ddr_ck_p和ddr_ck_n

由于是双沿采样,800M是实际的工作频率

用户时钟:(内部时钟)

400 / 4 =100M

表现是MIG的输出信号 ui_clk = DDR的IO时钟 / (PHY to Controller Clock Ratio)

DDR3 是8倍预读取,所以 ui_clk = 工作频率 / 8

此外MIG核还有 参考时钟ref_clk 和 系统时钟sys_clk_i

系统时钟一般为sys_clk_i=200M(工作频率大于666M时),即给MIG使用的

参考时钟一般选择使用系统时钟(use system clock),给MIG中的IEDELAY使用

存储器类型(Memory Type)选择 :Components

然后选择相应的DDR型号,Create Custom Part,电压为1.5V

DDR的数据位宽:16--128bit

ECC和数据掩码保持默认

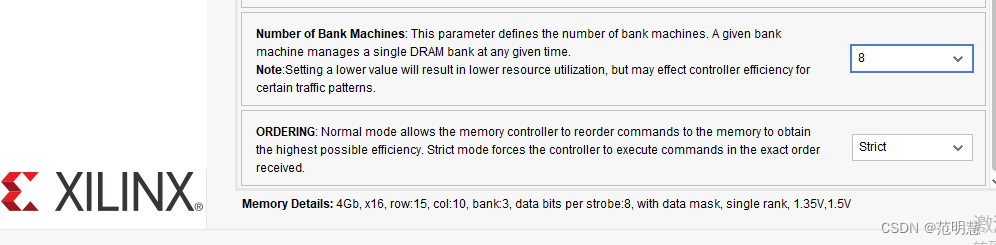

Bank Machine 数量,这里默认 4 个

命令排序方式选择 strict,即不对命令重新排序

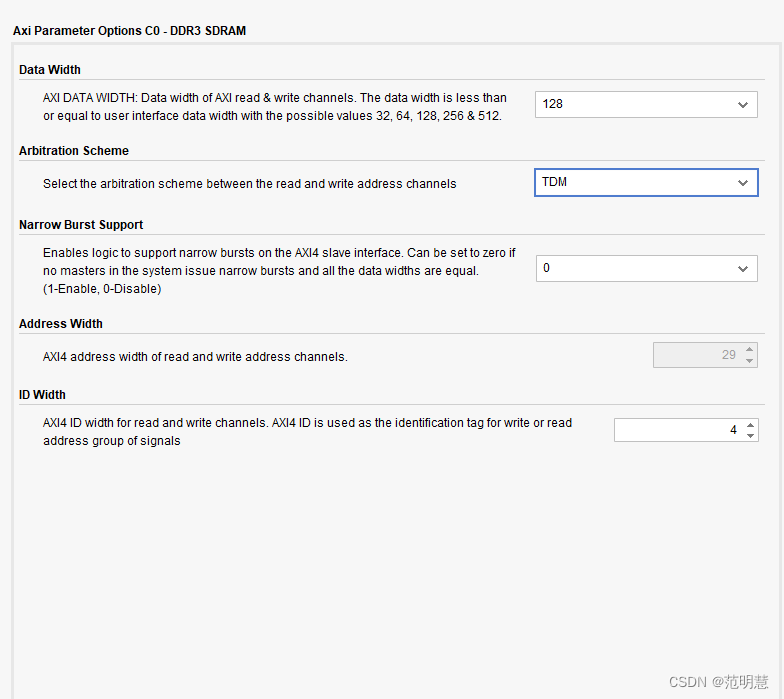

f、AXI4接口配置

AXI4数据位宽 128 = 16 * 8

TMD表示读写优先级相同,因为MIG只有一组地址线,DDR的读写两组地址线不能发挥作用

地址位宽 2Gb = 256MB = 2^28B 所以地址位为29位宽

AXI ID的位宽 4 ,AXI读写的通道号

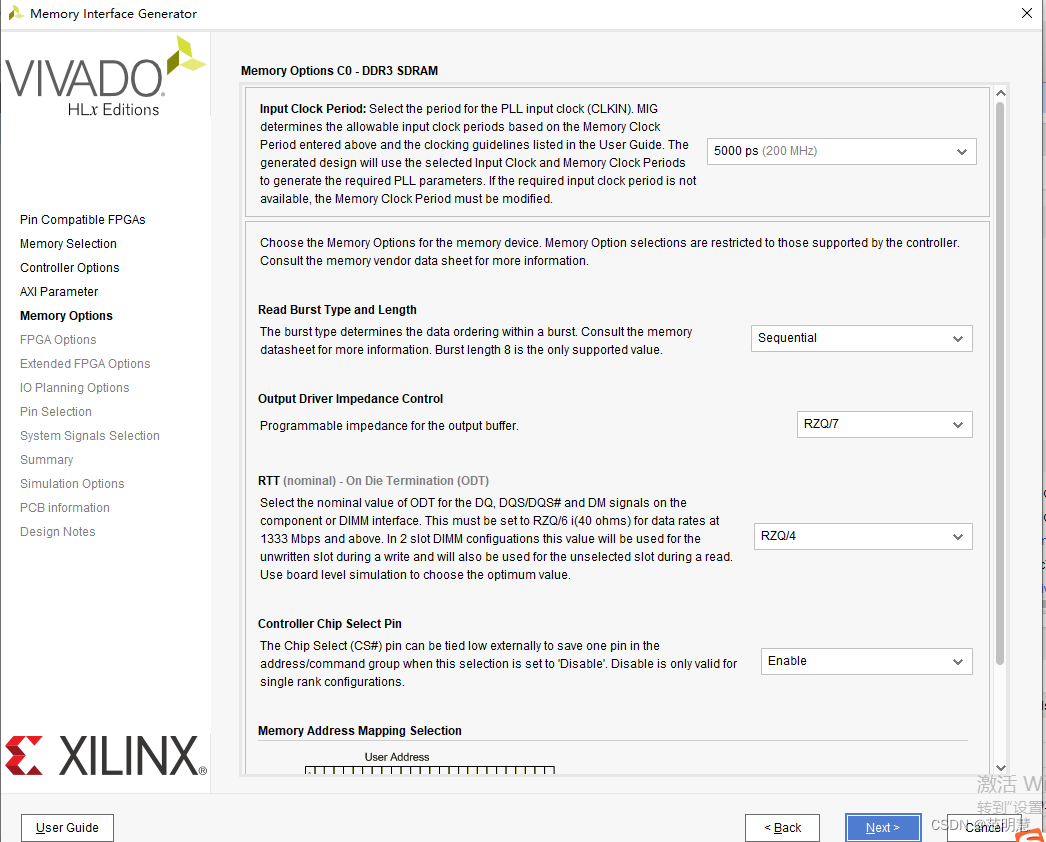

g、MEMORY OPTION

200M的系统时钟 sys_clk_i,FPGA晶振上只有125M,使用PLL生成

后续参考时钟也使用这个时钟

顺序读写Sequential

输出驱动阻抗 R ZQ/7

片上终端 R ZQ/4

片选信号:要注意硬件原理图,连接即使能,否则不使能

AXI和DDR的地址映射关系选择后者

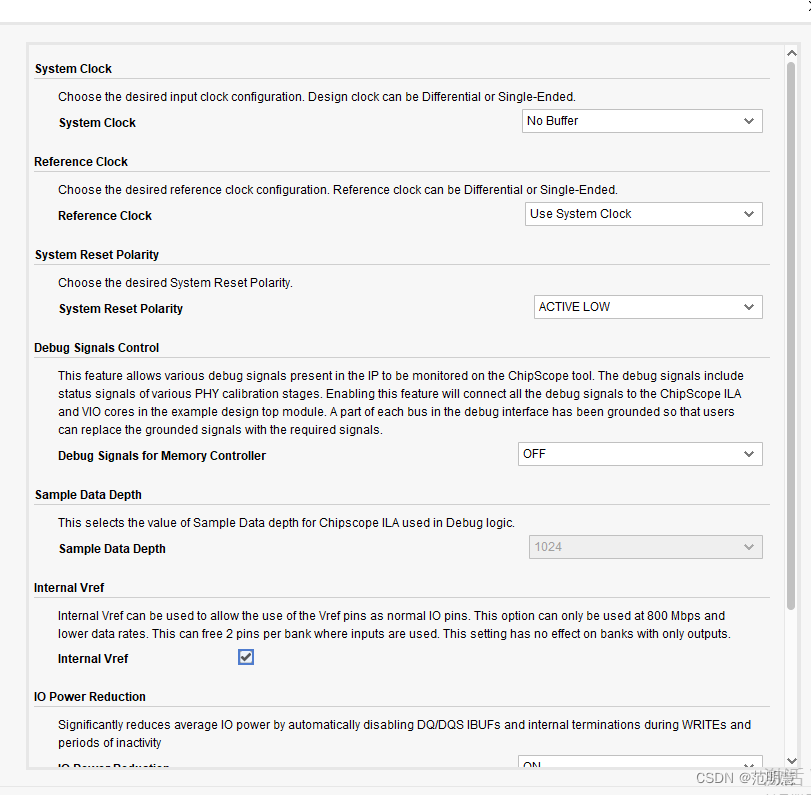

h、FPGA Option

系统时钟 no buffer

参考时钟使用系统时钟

低电平复位

勾选 Internal Vref

i、IO Selecting

设置内部阻抗:50hom

下面只要仿真的话,选择第一个选项;因为我们要上板,所以选第二个,配置引脚

配置引脚时,可以根据原理图选择 pin number 和 IO standard;也可以读取.ucf约束文件

验证后进入下一步

后面就不需要更改选项了,全部默认,最后选择 accept 即可

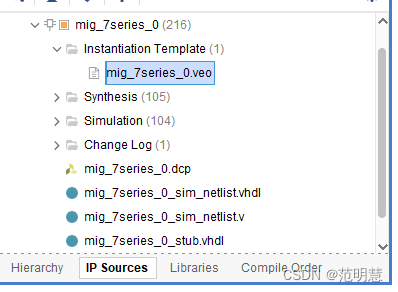

2、MIG信号说明

打开MIG的例化文件(.veo)

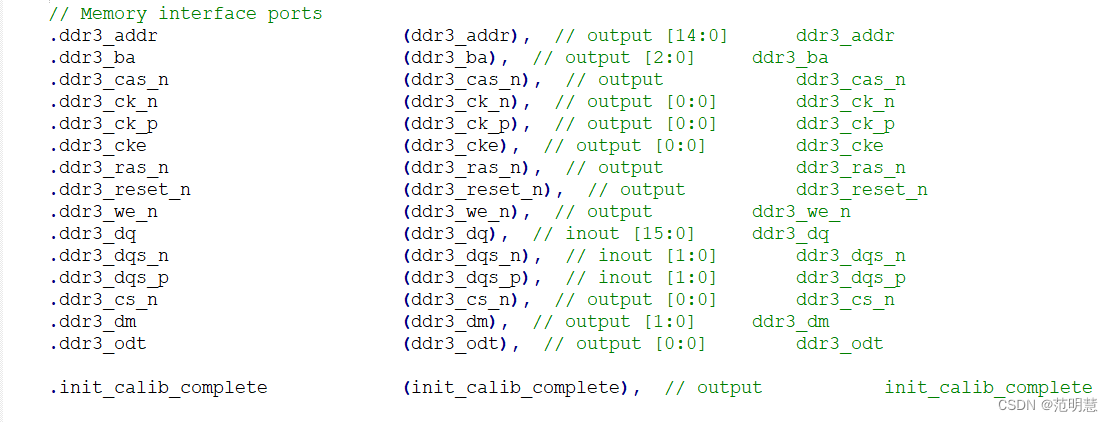

a、DDR接口

其中,init_calib_complete 信号表示MIG对DDR存储器初始化完成信号

init_calib_complete :(仿真时要先等该信号拉高,然后才能进行读写测试);

带有 ddr3 的信号:通引脚(.ucf文件)连到外部,与DDR存储器相连的,满足DDR传输的协议

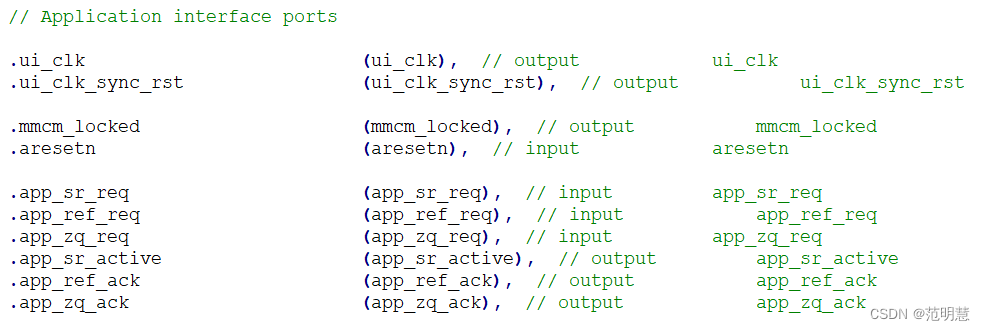

b、用户接口

其中

ui_clk 和 ui_clk_sync_rst :输出给用户的时钟复位,具体频率多少与前面Controller Option设置的 相关;ui_clk = Clock period / (PHY to Controller Clock Ratio)

即 DDR的 IO 时钟频率 除以 设置的速率比

mmcm_locked 和 aresetn:是MIG内部 PLL,MMCM的锁定(高有效)和复位信号(低有效)

带有 app 的信号是 用户接口维护命令信号:不使用,输入给0,输出不用

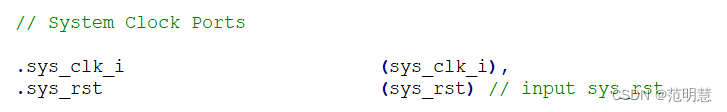

c、系统信号

即 输入给MIG控制器IP的信号,时钟是前面配置的200M,低电平复位;控制MIG的

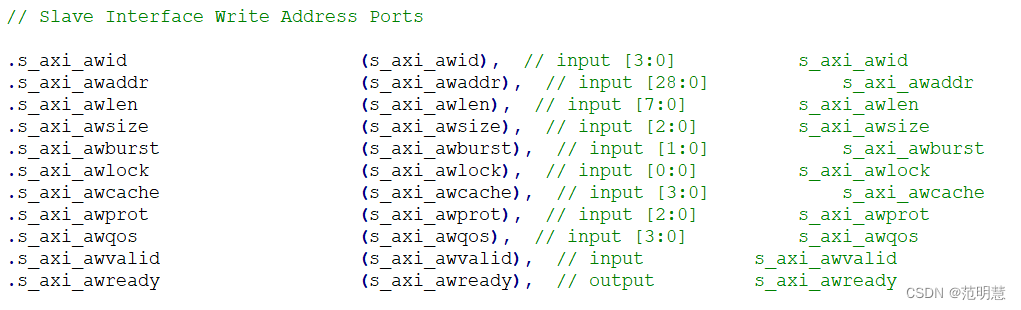

d、AXI接口信号

写地址信号

s_axi_awid : 写入的通道 ID tag;

可以不按照通道ID tag读写,但是必须完成一个ID tag才能进入下一个ID tag

s_axi_awaddr :写入数据的地址

s_axi_awlen :突发写的长度,数据写入长度 = s_axi_len + 1;

s_axi_awsize :写入数据的位宽大小,以字节为单位;s_axi_awsize = 4,即 2^4 = 16Byte

s_axi_awburst :突发类型,一般是01;

s_axi_awlock ,s_axi_awcache ,s_axi_awprot ,s_axi_awqos :一般全输入为 0

s_axi_awvalid :由信息源端发送给目的端,代表信息源端的写入地址有效(主机发送)

s_axi_awready :由目的端发送给信息源端,代表目的端准备接受(从机发送)

当 s_axi_awvalid 和 s_axi_awready 同时为高时,才将地址信息和控制信息传给设备

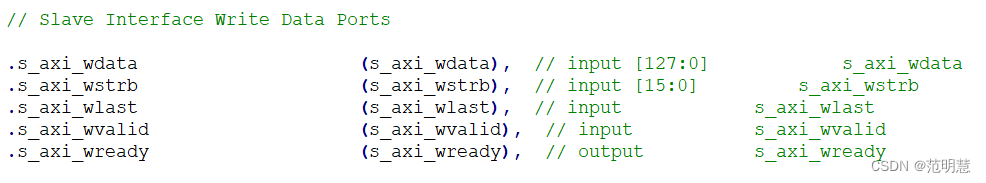

写数据信号

s_axi_wdata : 要写入的数据

s_axi_wstrb : 数据有效码;每一位拉高代表一个字节的数据有效

s_axi_wlast :最后一位传输时拉高

s_axi_wvalid :由信息源端发送给目的端,代表信息源端的写入数据有效(主机发送)

s_axi_wready :由目的端发送给信息源端,代表目的端准备接受(从机发送)

当 s_axi_wvalid 和 s_axi_wready 同时为高时,才将数据信息传给设备

写响应信号

s_axi_bid :写响应通道,与awid相同

s_axi_bid :写响应通道,与awid相同

s_axi_bresp :写响应状态;2'b00表示OK,写入正常

(valid 和 ready 方向相反)

s_axi_bvalid :由目的端发送给信息源端,代表目的端的写入响应有效(从机发送)

s_axi_bready :由信息源端发送给目的端,代表信息源端准备接受(主机发送)

当 s_axi_bvalid 和 s_axi_bready 同时为高时,才将写入响应信息传给主机

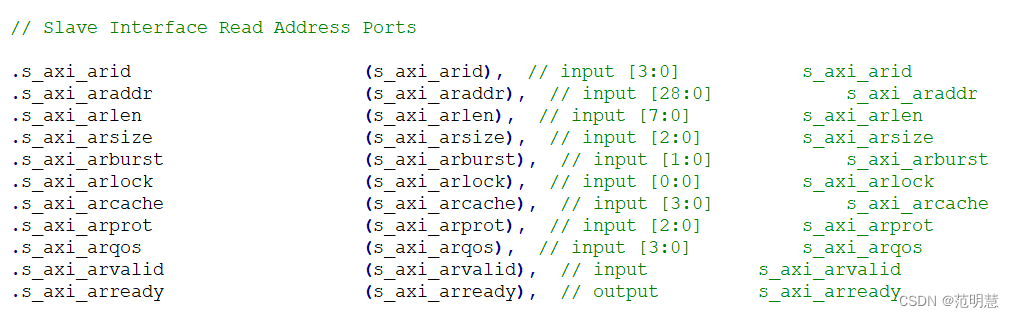

读地址信号

s_axi_arid :读取地址的 ID tag

s_axi_araddr :读取数据的地址

s_axi_arlen : 读取数据的突发长度;数据读取长度 = s_axi_arlen + 1;

s_axi_arsize :读取数据的位宽,以字节为单位;s_axi_arsize = 4,2^4 = 16Byte

s_axi_arburst :读突发的类型,一般为 2'b01

s_axi_arlock,s_axi_arcache,s_axi_arprot,s_axi_arqos :一般全为0;

s_axi_arvalid :由信息源端发送给目的端,代表信息源端的读取地址有效(主机发送)

s_axi_arready :由目的端发送给信息源端,代表目的端准备接受(从机发送)

当 s_axi_arvalid 和 s_axi_arready 同时为高时,才将地址信息和控制信息传给设备

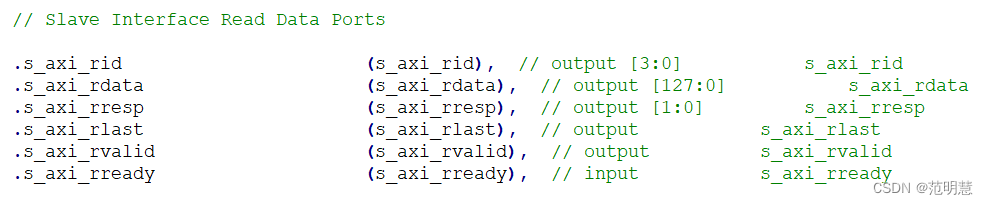

读数据信号

s_axi_rid :读取数据的 ID tag,与s_axi_arid相同

s_axi_rdata :读取的数据

s_axi_rresp :读响应状态;2'b00表示OK,读取正常

s_axi_rlast :最后一次读取时拉高

s_axi_rvalid :由目的端发送给信息源端,代表目的端的读取数据和响应有效(从机发送)

s_axi_rready :由信息源端发送给目的端,代表信息源端准备接受(主机发送)

当 s_axi_rvalid 和 s_axi_rready 同时为高时,才将读取数据和响应信息传给主机

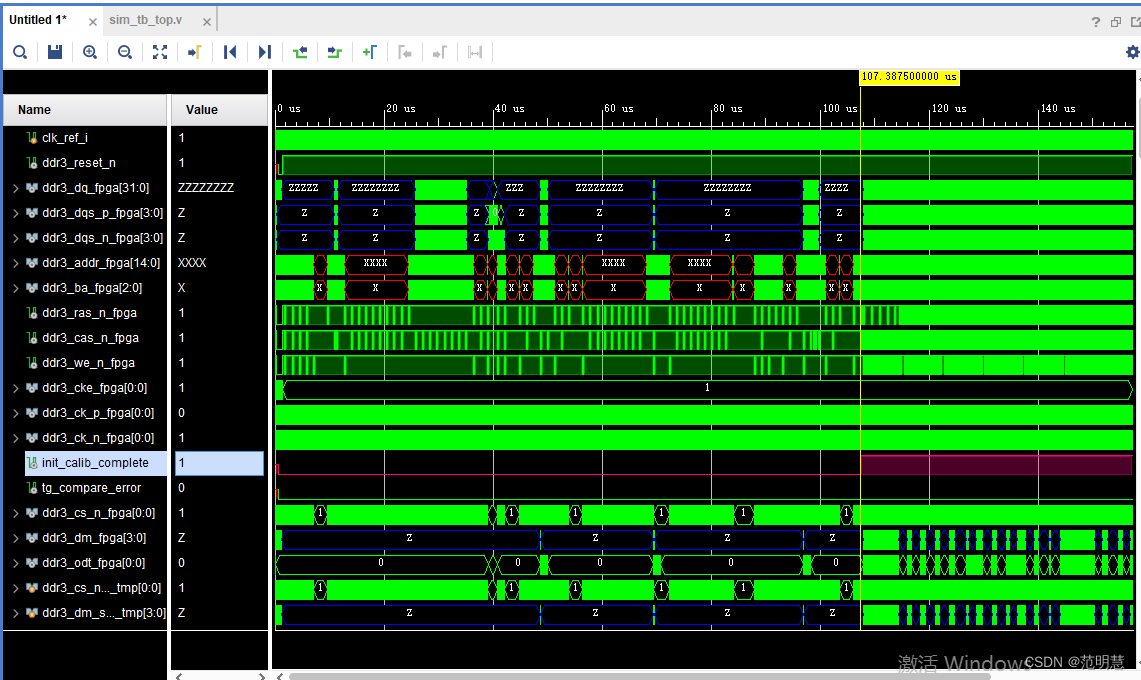

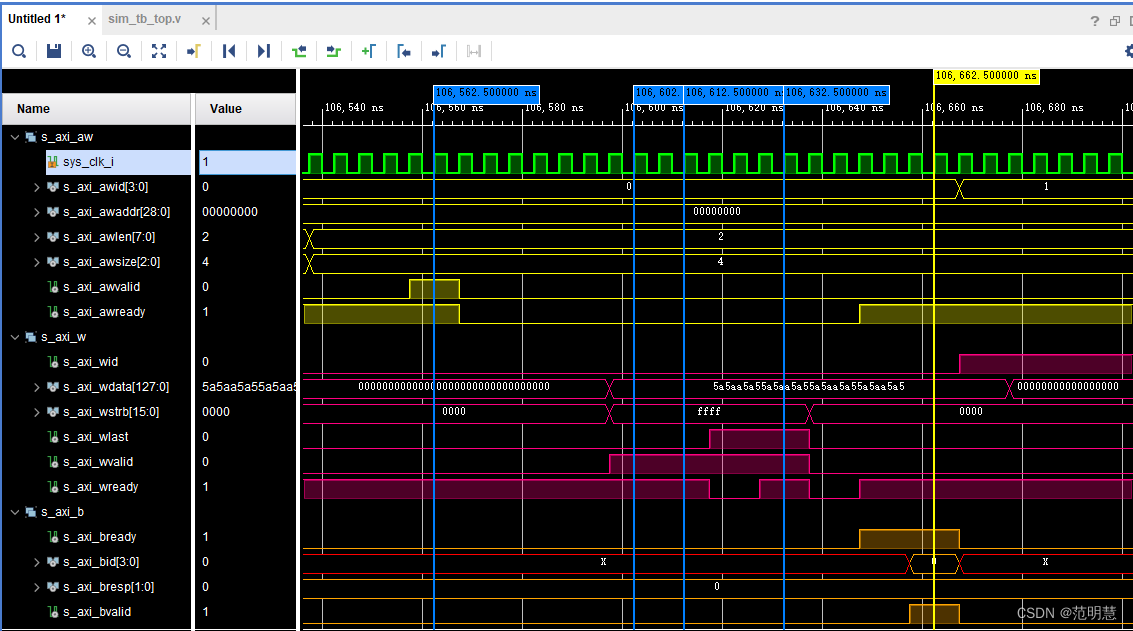

二、仿真DDR,对照AXI4协议查看波形

前面配置完成之后,直接右击MIG核,打开官方例程进行仿真( open ip example design )

直接simulation

等待一段时间,init_calib_complete信号拉高后,DDR初始化完成

添加 AXI4 信号,重新仿真

这里要注意的是显示的系统时钟 sys_clk 是输入给MIG核的(200M)

而AXI4的时序时钟是MIG输出的用户时钟 ui_clk (100M),查看时要留意

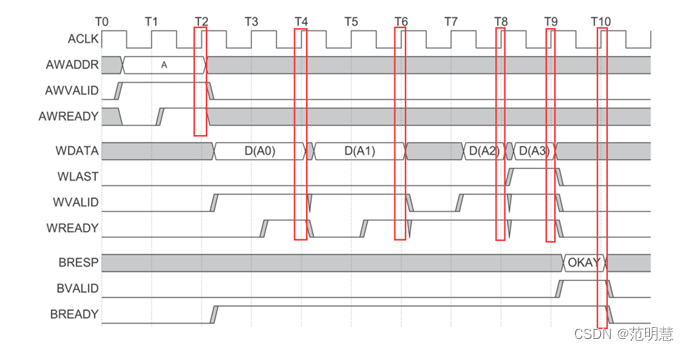

写

黄色线 awvalid 和 awready 同时拉高时

写入的 ID tag 是 4'b0

写入的地址是 29'd0

写入的数据长度是 2+1 = 3

写入的数据位宽是 2^4 = 16Byte

粉色的线在 wvalid 和 wready 拉高时,确实保持3个 ui_clk(100M)

wlast 最后一个周期拉高

wstrb 为 16'hffff,数据全部有效

128'h5a_5a_a5_a5_5a_5a_a5_a5_5a_5a_a5_a5_5a_5a_a5_a5确实是16Byte

橙色线在 bvalid 和 bready 同时拉高时,bresp 为 2'd0 写入状态正常

符合AXI4写时序

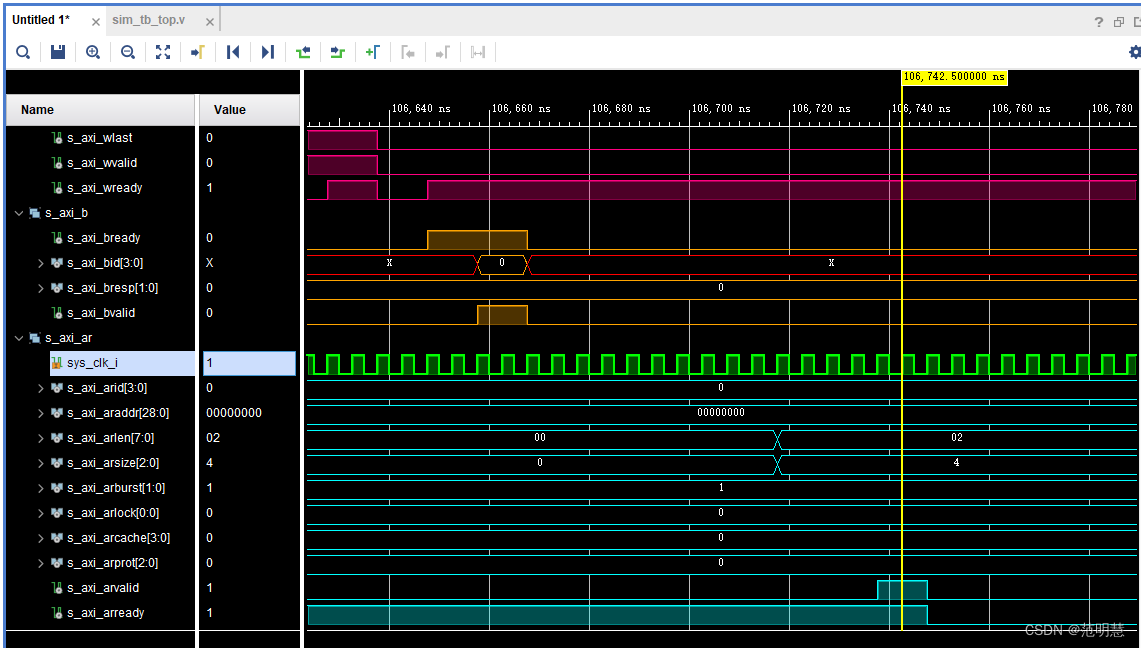

读

写入状态响应正常之后,过一段时间开始读

蓝色线 rrvalid 和 rrready 同时拉高时

读取的 ID tag 是 4'b0

读取的地址是 29'd0

读取的数据长度是 2+1 = 3

读取的数据位宽是 2^4 = 16Byte

与之前写入的相同(aw),读写地址正确

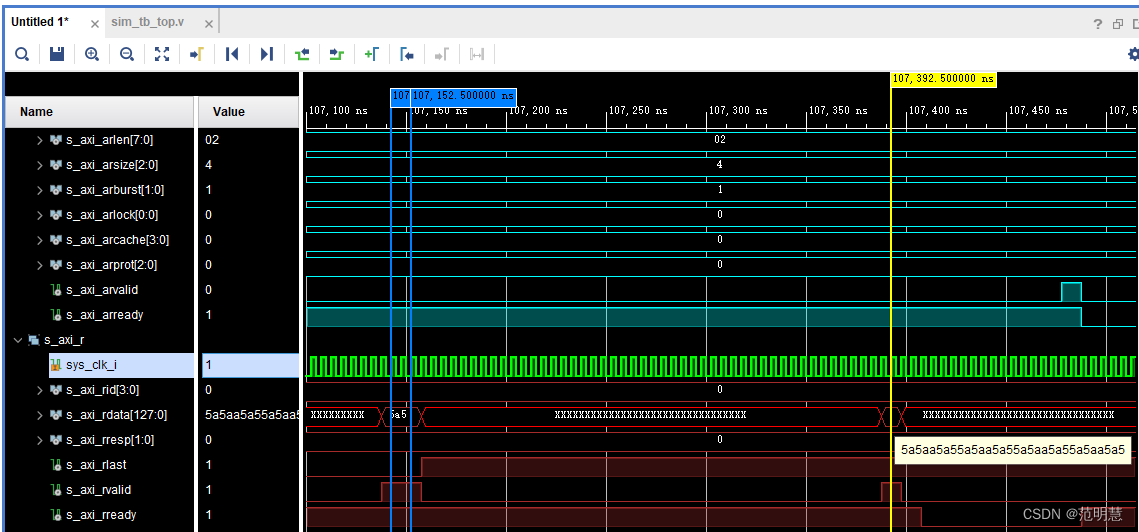

褐色线在rvalid 和 rready同时拉高时,持续3个 ui_clk ;在最后一次读取时,rlast 拉高;

读取响应为2'd0,状态正常;读取的数剧也与之前写入的相同。

AXI4读时序正确

至此带有AXI4接口的MIG核仿真验证成功