- 1代码随想录算法训练营第四十七天|198.打家劫舍、213.打家劫舍II、337.打家劫舍III

- 2基于的X86+FPGA轨道交通模块化计算机,标准3U无风扇,支持国产化定制

- 3【开发工具】VS编译后生成的文件类型_vs是二进制文件而非文本文件

- 4android 上网 (二)-- apn切换拨号_android移动网络apn自动拨号代码

- 5全网最全Python操作Excel教程,建议收藏!

- 6SpringBoot框架介绍及使用_spring boot默认配置了哪些框架的使用方式

- 7FPGA—DDS信号发生器笔记_dds信号发生器fpfga

- 8探索OpenSSH版本升级_openssh升级

- 9Swagger2 入门及使用

- 10Kingbase(人大金仓数据库)(总结全网精华,虚拟机:从安装到操作数据库一条龙)_kingbase数据库

7 Series FPGAs Integrated Block for PCI Express IP核简介_xilinx pcie ip核

赞

踩

7 Series FPGAs Integrated Block for PCI Express IP核是Xilinx公司7系列FPGA中集成的PCI Express(PCIe)IP核模块,是一个可扩展的、高带宽的、可靠的串行互联构建块,用于与Xilinx的Zynq®-7000 SoC和7系列FPGA配合使用。它支持1-lane、2-lane、4-lane和8-lane的端点(Endpoint)和根端口(Root Port)配置,速度可达5 Gb/s(Gen2),所有配置都符合PCI Express Base Specification,rev. 2.1。

Xilinx的7系列FPGA中集成的PCI Express IP核模块为那些需要高速、可靠的数据传输的应用提供了强大的支持,同时保持了低开销和低延迟。它为用户提供了一个灵活的、可扩展的接口,并支持最新的PCI Express标准。

特征

(1)是高性能、高度灵活、可扩展和可靠的通用I/O核

高性能:能够提供快速的数据传输和处理能力。

高度灵活:可以适应不同的应用场景和配置需求。

可扩展:系统可以根据需要增加更多的I/O通道或功能。

可靠:在数据传输和处理过程中具有高度的稳定性和可靠性。

(2)采用Xilinx Smart-IP技术以保证关键时序

Xilinx的Smart-IP技术是一种智能知识产权(IP)解决方案,它集成了经过验证的硬件设计和 软件工具,以确保设计的正确性和性能。在这里,它被用来保证PCIe I/O核心的关键时序要求 得到满足。

(3)使用GTXE2或GTPE2收发器(针对7系列FPGA)

GTXE2和GTPE2是Xilinx为其7系列FPGA提供的高速串行收发器。

2.5 GT/s和5.0 GT/s线速度:这些收发器支持高达2.5 GT/s和5.0 GT/s的线速度,提供了高速 数据传输的能力。

支持1通道、2通道、4通道和8通道操作:可以根据需要配置为不同的通道数,以满足不同的 带宽和性能需求。

弹性缓冲和时钟补偿:有助于在数据传输过程中处理时钟偏差和抖动,确保数据的完整性和 准确性。

自动时钟数据恢复(CDR):用于从接收到的数据中恢复时钟信号,从而提高数据传输的稳 定性。

(4)支持Endpoint和Root Port配置

PCIe系统中有两种主要类型的设备:Endpoint(端点)和Root Port(根端口)。该IP核可以 配置为这两种类型中的任何一种,以适应不同的系统架构和需求。

(5)8B/10B编码和解码

8B/10B是一种线路编码方案,用于在高速串行通信中确保数据的直流平衡和同步。它通过将8 位数据转换为10位编码来减少由于连续0或1造成的位流偏差。

(6)支持PCIe规范要求的Lane Reversal和Lane Polarity Inversion

Lane Reversal(通道反转):在某些情况下,可能需要反转通道的数据传输方向。

Lane Polarity Inversion(通道极性反转):改变通道上数据的逻辑极性(例如,将1转换为 0,将0转换为1)。

(7)标准化的用户界面

提供了统一的、标准化的用户界面,使得开发人员可以更容易地集成和使用该IP核。

(8)符合PCI/PCI Express电源管理功能

PCIe接口遵循PCI和PCI Express标准中的电源管理功能。这意味着它支持各种电源管理特 性,如节能状态(如L0s、L1等)、电源状态转换以及电源管理消息等。这些功能有助于优化 系统的能耗和性能。

(9)符合事务处理顺序规则

PCIe接口遵循PCI Express标准中的事务处理顺序规则。这些规则确保了事务(如内存读写、 I/O请求等)按照正确的顺序执行,从而避免了数据冲突和不一致性。

(10)支持最大事务负载高达1024字节

(11)支持多向量MSI(Message-Signaled Interrupts)高达32个向量和MSI-X

MSI是一种中断机制,它使用PCIe消息而不是传统的硬件中断线来通知CPU设备需要服务。 多 向量MSI允许设备为每个中断源分配一个独特的消息ID,从而允许CPU同时处理多个中断。

MSI-X是MSI的扩展版本,它提供了更多的中断向量和更好的中断管理能力。MSI-X允许设备 为每个中断源分配一个独特的内存写入地址,从而减少了中断处理时的CPU开销。

(11)上配置(Up-configure)能力使应用驱动带宽可扩展性

上配置(Up-configure)是一种PCIe功能,它允许在运行时动态地增加PCIe链路的带宽。这 意味着,如果系统需要更高的数据传输速率,可以通过重新配置PCIe链路来实现。这种能力 使得PCIe接口能够根据应用的需求动态地调整带宽,从而实现了应用驱动的带宽可扩展性。

概述

在Xilinx 7系列FPGA中,7 Series FPGAs Integrated Block是一个重要的组成部分,它允许FPGA设备与其他PCIe设备(如处理器、内存和其他扩展卡)进行高效的数据交换。通过支持不同的PCIe速度(包括2.5 Gb/s、5.0 Gb/s和8.0 Gb/s Gen3),这些FPGA可以满足广泛的应用需求,包括高性能计算、网络通信和数据中心等。

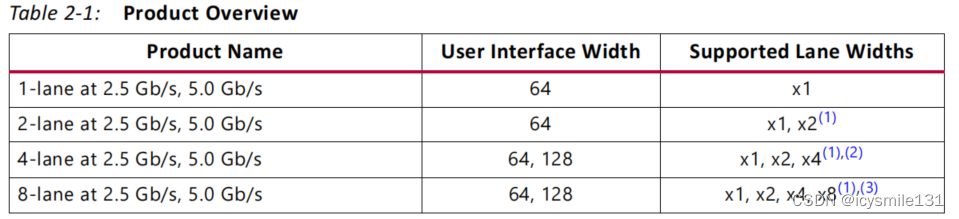

下表定义了PCIe®决方案的集成块。

7 Series FPGAs Integrated Block IP核内部实例化了7系列FPGA的PCI Express集成块(PCIE_2_1),通过实例化PCIE_2_1集成块来支持PCIe协议。这个集成块遵循PCI Express基础规范的分层模型,该模型包括物理层、数据链路层和事务层。按照PCIe基础规范的分层模型进行设计和实现,确保了与PCIe标准的兼容性和可靠性。

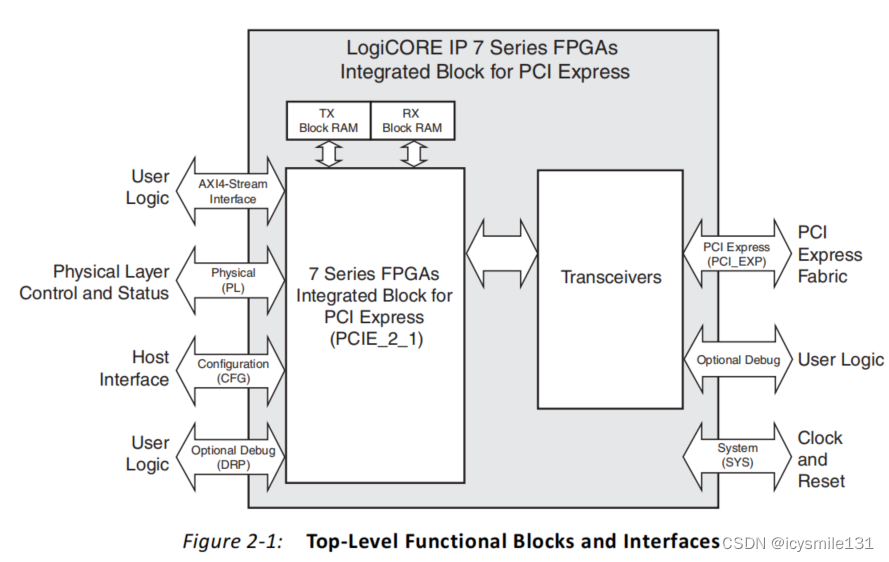

在Figure 2-1中描述的这些接口,与7系列FPGA的PCI Express(PCIe)硬核相关,包括系统(SYS)接口、PCI Express(PCI_EXP)接口、配置(CFG)接口、事务接口(AXI4-Stream)以及物理层控制和状态(PL)接口。下面是对这些接口的简要说明:

- 系统(SYS)接口:允许FPGA与外部系统或处理器进行通信的接口。通过此接口,FPGA可以接收来自系统或处理器的命令和数据,也可以向系统或处理器发送数据。

- PCI Express(PCI_EXP)接口:这是PCIe硬核的主要接口,用于实现PCIe的物理层、链路层和事务层。它允许FPGA与其他PCIe设备(如显卡、存储设备等)进行高速数据传输。

- 配置(CFG)接口:此接口用于配置PCIe硬核的参数和设置。通过CFG接口,用户可以对PCIe硬核进行初始化、设置其工作模式和参数等。

- 事务接口(AXI4-Stream):AXI4-Stream是Xilinx FPGA中使用的一种高速数据流接口。在PCIe硬核中,它用于在FPGA的逻辑部分和PCIe硬核之间传输事务层数据包(TLP)。用户如果需要向PC发送数据,就需要在逻辑端组好MEM_WR事务包并发送到AXI4-Stream接口;同样,如果要从PC获取数据,就需要发送MEM_RD事务包,并从返回的COMPLETE事务包中提取数据。

- 物理层控制和状态(PL)接口:此接口用于控制和监控PCIe硬核的物理层。通过PL接口,用户可以读取物理层的状态信息(如链路状态、错误计数等),也可以对物理层进行某些控制操作(如重置链路、配置参考时钟等)。

7 Series FPGAs Integrated Block IP核使用数据包(packets)在上述各个模块之间交换信息。这些数据包在事务层(Transaction Layer)和数据链路层(Data Link Layer)中形成,用于将信息从发送组件传输到接收组件。在传输数据包时,会添加必要的信息,以便在这些层中处理数据包。

在接收端,接收元素的每一层都会处理传入的数据包,剥离相关的信息,并将数据包转发到下一层。这个过程涉及到从物理层表示(Physical Layer representation)到数据链路层表示(Data Link Layer representation),再到事务层表示(Transaction Layer representation)的转换。

在接收端,数据包首先会到达物理层,然后逐层向上传输,每个层都会剥离掉自己添加的头信息,并将数据包转发给上一层。最终,数据包会到达事务层,这时数据包中的信息就可以被应用程序或设备驱动程序使用了。

通过这种分层处理的方式,PCIe协议能够高效地处理大量的数据传输请求,同时保持较低的错误率和较高的可靠性。

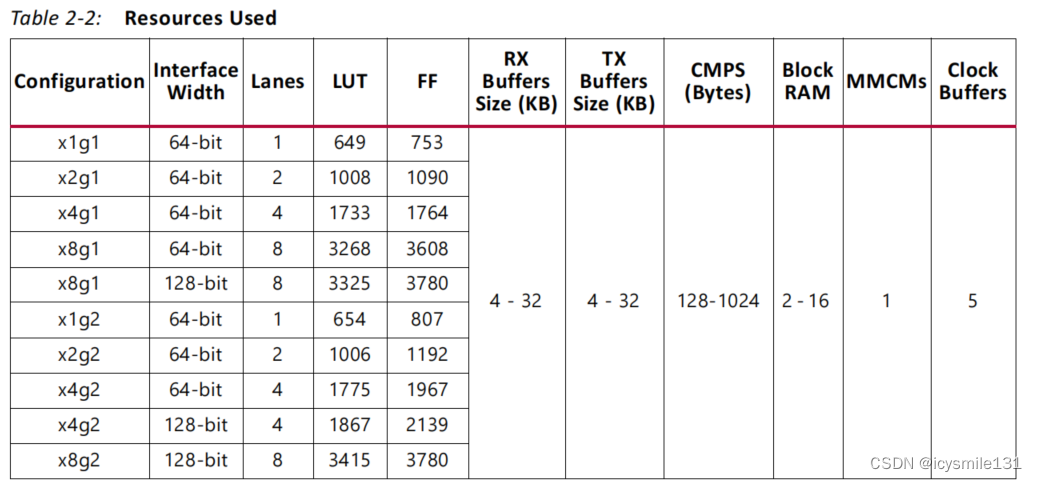

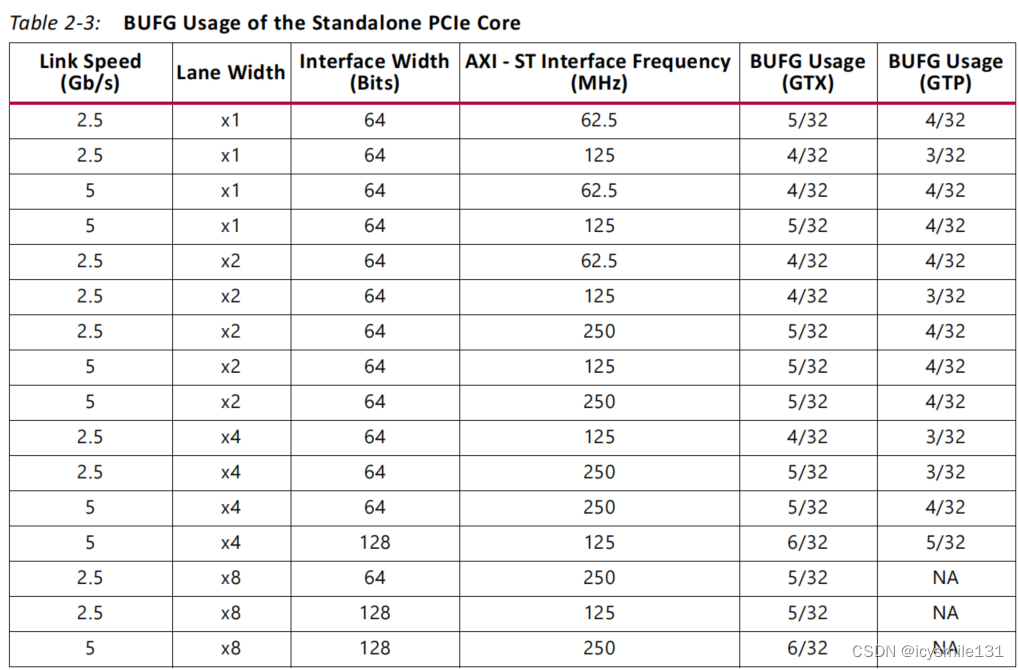

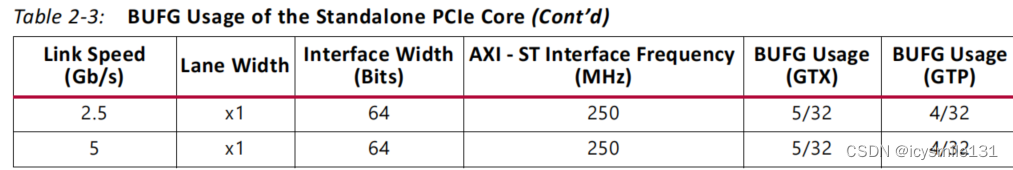

下面两张表显示在Vivado® Design Suite中实现PCI Express(PCIe)硬核时的资源信息。

IP核接口

7 Series FPGAs Integrated Block IP核包含顶层信号接口和发送接口。

顶层信号接口

(1)系统(SYS)接口

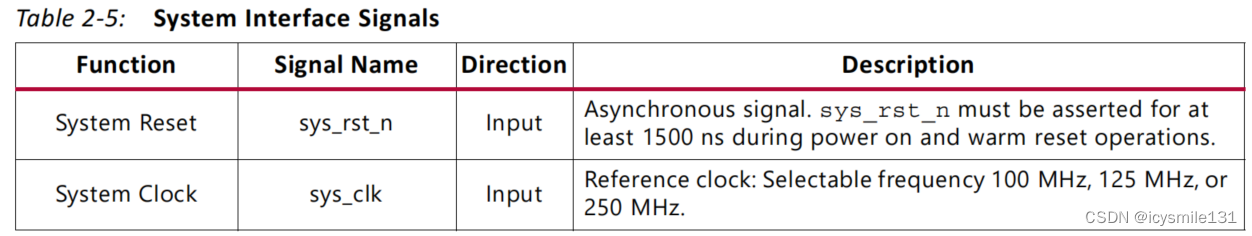

包括系统复位信号(sys_rst_n)和系统时钟信号(sys_clk),这些在Table 2-5中有描述。

系统复位信号(sys_rst_n)是一个低电平有效的信号,用于初始化或重置PCIe IP核。当这个信号被激活(即被拉低)时,PCIe IP核将回到其初始状态或重置状态。

在一些7系列设备中,可能并没有提供3.3V的I/O端口,因此当这些设备只包含1.8V的bank时,就需要进行适当的电平转换来操作。

系统复位信号(sys_rst_n),它是一个异步输入,低电平有效。用于初始化或重置PCIe IP核。当sys_rst_n被激活(即被拉低)时,它将导致整个PCIe IP核的硬复位,即PCIe IP核将回到其初始状态或重置状态。这个系统复位信号是一个3.3V的信号。

系统时钟信号(sys_clk)是用于PCIe IP核操作的时钟信号。这个时钟信号定义了PCIe IP核内部操作的时序和速率。PCIe IP核的所有功能,包括数据传输、控制和状态更新等,都将基于这个时钟信号进行操作。

系统输入时钟(sys_clk)的频率必须是100MHz、125MHz或250MHz中的一个,具体选择取决于在Vivado® IP目录中的时钟和参考信号设置。这些频率值是根据PCIe协议规范和PCIe核心的要求来确定的,以确保正确的数据传输和同步。

(2)PCI Express 接口

PCI Express(PCI_EXP)接口是一个高速串行计算机扩展总线标准,用于连接计算机的主板和其他设备,如显卡、网络接口卡、固态硬盘等。它使用差分信号传输技术,以提高数据传输的可靠性和速度。

PCI Express 接口由多个“通道”(lane)组成,每个通道包含一对差分发送信号(pci_exp_txp, pci_exp_txn)和一对差分接收信号(pci_exp_rxp, pci_exp_rxn)。

其中PCI Express 通道数为:

- 1-lane 核心:只支持 Lane 0。

- 2-lane 核心:支持 Lane 0 和 Lane 1。

- 4-lane 核心:支持 Lane 0 到 Lane 3。

- 8-lane 核心:支持 Lane 0 到 Lane 7。

通道数的增加可以提高数据传输的带宽,但也会增加硬件的复杂性和成本。

事务接口

(1)通用接口

(2)发送接口

s_axis_tx_tuser 总线包含了多个不相关的信号,这些信号用于在AXI-Stream接口的发送(Tx)路径上传递额外的用户定义信息。

例如:在(tsrc_dsc)s_axis_tx_tuser[3] 中,tsrc_dsc 是一个助记符,用于标识s_axis_tx_tuser总线的第4个信号(因为数组索引通常从0开始)是“Transmit Source Discontinue”信号。这里的括号可能是为了在文档中清晰地表明助记符与信号名的关联。

(3)接收接口

其中,m_axis_rx_tuser 总线包含了一组不相关的信号,这些信号在AXI-Stream接口的接收(Rx)路径上传递额外的用户定义信息。

(4)物理链路层接口

允许用户设计来检查链路(Link)和链路伙伴(Link Partner)的状态,并控制链路的状态。

(5)配置接口

允许用户设计检查PCIe配置空间的状态。具体来说,用户设计提供一个10位的配置地址,这个地址用于选择1024个配置空间双字(DWORD)寄存器中的一个。然后,PCIe端点通过32位数据输出端口返回所选寄存器的状态。

PCIe配置空间是一个重要的组成部分,它包含了PCIe设备的信息和配置选项。这个空间由一系列的寄存器组成,每个寄存器都存储了关于设备的一个特定方面的信息或设置。通过CFG接口,用户可以读取和修改这些寄存器,从而获取PCIe设备的状态信息或配置设备的行为。

(6)终端接口

(7)错误汇报接口

(8)动态配置接口

允许用户对对7 Series FPGAs Integrated Block IP核的FPGA配置存储器位进行动态更改。这些配置位以PCIE_2_1库原语的属性形式表示,这些原语是该IP核的一部分的实例化。

具体来说,DRP(Dynamic Reconfiguration Port)是一种用于外设配置和通信的接口技术,它可以通过FPGA内部的可编程逻辑实现,提供了一种快速、灵活地配置和通信外设的方式。DRP接口具有灵活性,可以在设计过程中根据需要动态地配置和重新配置外设,无需重新实现整个设计,这可以大幅度降低开发成本和时间,并提供更快的产品上市时间。

在7系列FPGA中,配置存储器不仅用于实现用户逻辑、连接和I/O,还用于其他目的,如指定功能块中的各种静态条件。有时,应用程序需要在功能块运行时更改这些条件,这可以通过使用DRP等接口进行部分重配置来实现。DRP接口还支持动态重配置功能,可以在无需停机或重启系统的情况下对外设进行热插拔或重新配置。

总的来说,DRP接口为FPGA的动态配置提供了强大的支持,使得FPGA的设计更加灵活和高效。

(9)内部端点接口

(10)内部配置访问端点接口