热门标签

热门文章

- 1RuoYi-Vue-Plus (Echarts 图表)_若依图表

- 2Python+moviepy使用manual_tracking和headblur函数10行代码实现视频人脸追踪打马赛克_视频流 人物跟踪打码 python

- 3MySQL8.4 安装配置与卸载_mysql8.4安装

- 4【Kafka】Kafka 实现 Exactly-once (ack机制、高水位)_kafka exactly once

- 5web安全--点击劫持攻击与防御技术简介

- 6iMazing2023官网中文版下载及许可证附使用教程_imazing官网

- 7Android Studio实现简单的记事本_android studio记事本

- 8基于Python爬虫山东济南天气预报数据可视化系统设计与实现(Django框架) 研究背景与意义、国内外研究现状_python国外研究现状文献综述

- 9自然语言处理NLP概述_nlp是什么意思

- 10解决postman打开一直转圈圈的问题_postman一直转圈圈打不开

当前位置: article > 正文

基于FPGA的数字秒表设计_设计要求 设计一个数字秒表,用lcd1602反应秒表状态。 、设计目的 学习fpga设

作者:神奇cpp | 2024-07-07 19:10:59

赞

踩

设计要求 设计一个数字秒表,用lcd1602反应秒表状态。 、设计目的 学习fpga设

VHDL实现数字秒表

1设计要求

(1) 能对0秒~59分59.99秒范围进行计时,显示最长时间是59分59秒;

(2) 计时精度达到10ms;

(3) 设计复位开关和启停开关,复位开关可以在任何情况下使用,使用以后计时器清零,并做好下一次计时的准备。

2数字秒表设计的目的

本次设计的目的就是在掌握EDA实验开发系统的初步使用基础上,了解EDA技术,对计算机系统中时钟控制系统进一步了解,掌握状态机工作原理,同时了解计算机时钟脉冲是怎么产生和工作的。在掌握所学的计算机组成与结构课程理论知识时。通过对数字秒表的设计,进行理论与实际的结合,提高与计算机有关设计能力,提高分析、解决计算机技术实际问题的能力。通过课程设计深入理解计算机结构与控制实现的技术,达到课程设计的目标。

2.1 设计规划

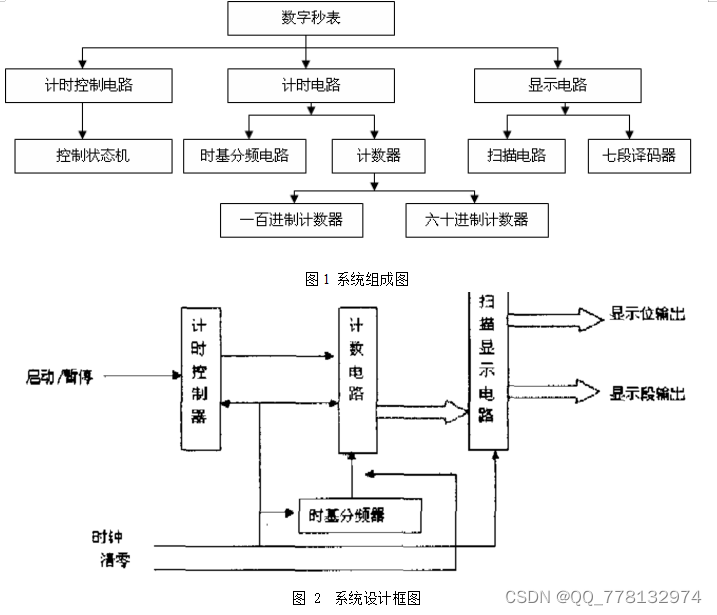

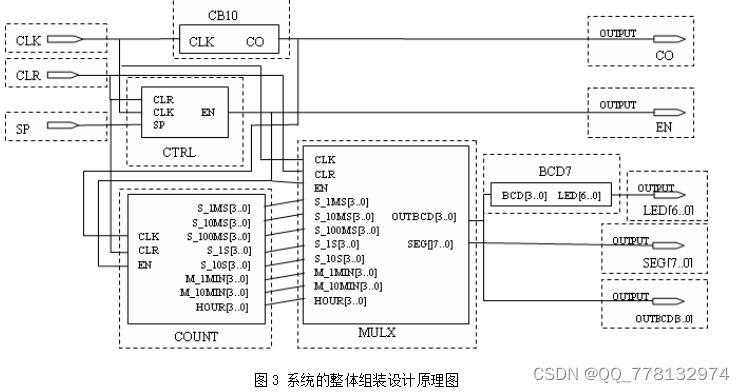

本系统设计采用自顶向下的设计方案,系统的整体组装设计原理图如图1所示,它主要由控制模块、时基分频模块,计时模块和显示模块四部分组成。各模块分别完成计时过程的控制功能、计时功能与显示功能。

2.2.1控制模块

计时模块的作用是针对计时过程进行控制。计时控制模块可用俩个按钮来完成秒表的启动、停止和复位。部分源程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.a

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/神奇cpp/article/detail/796588

推荐阅读

相关标签