- 1用verilog设计一数字钟系统_verilog数字钟手动调整时间

- 2【华为OD】C卷200分真题 100%通过:路口最短时间问题 JS语言代码实现[思路+代码]_> 假定街道是棋盘型的,每格距离相等,车辆通过每格街道需要时间均为 timeperroad;

- 3Github/gitee 上传文件最大100MB限制this exceeds file size limit of 100.0 MB_this exceeds github's file size limit of 100.00 mb

- 4gitee上传本地文件

- 5利用transmac在windows上做启动U盘_transmac是不是不能用超过16g的优盘

- 6【Java】智慧校园家校互通小程序源码_校园小程序源码

- 7JDBC连接MySQL的五种方式_jdbc你如何连接mysql properties

- 8【CRASH】freelist异常导致的异常地址访问

- 9【数据结构】-树及森林 菜单实现 深度优先 广度优先 递归遍历_广度优先 带路径递归

- 102018年春招总结(暑假实习生C++岗)_c++实习简历

期末大作业 电子钟_数字电子时钟设计顶层模块各个模块连接

赞

踩

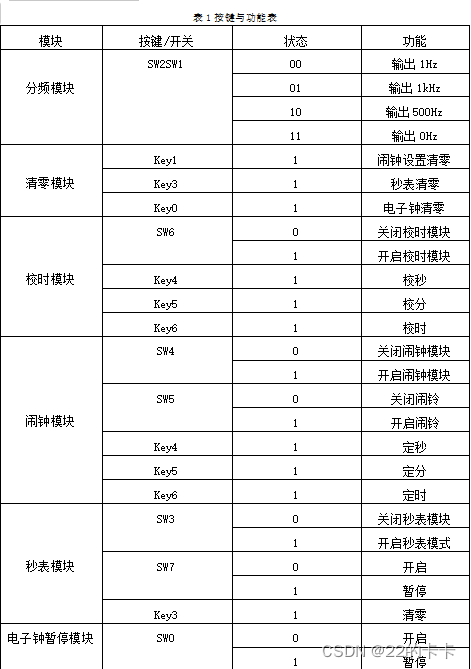

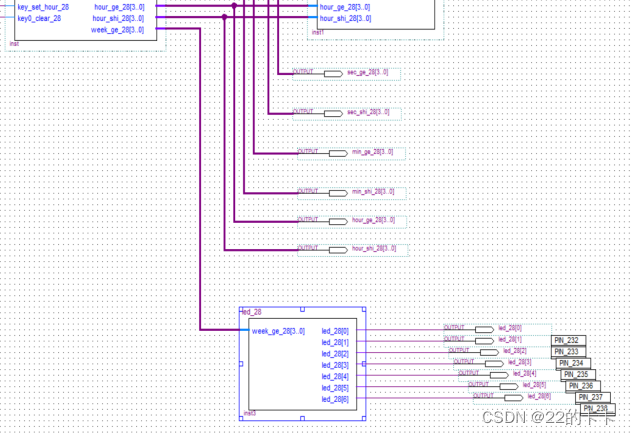

1.系统顶层模块设计

(1) 按键、开关功能介绍

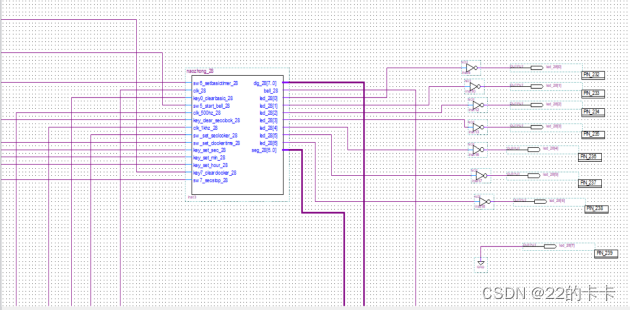

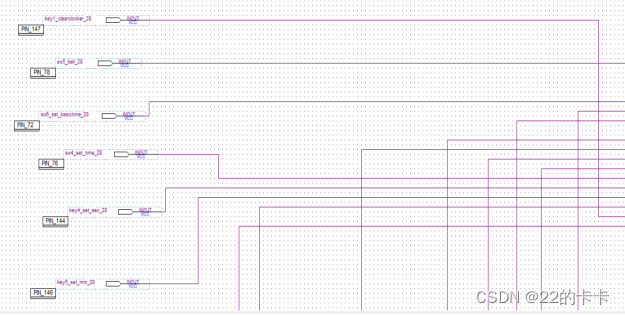

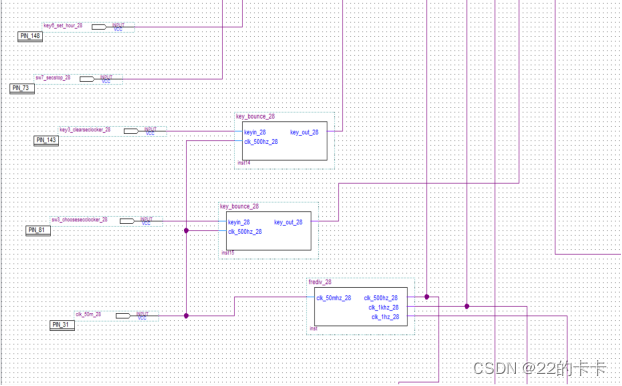

(2) 顶层设计原理框图

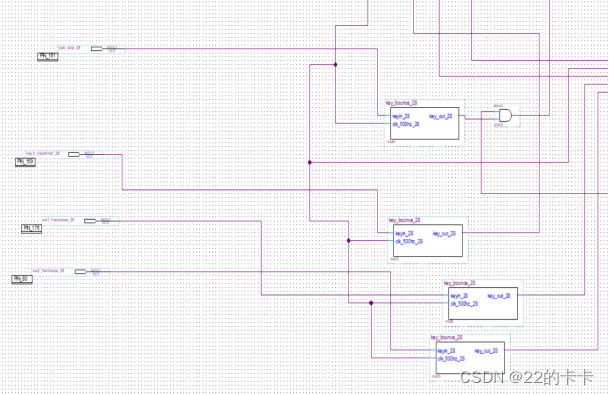

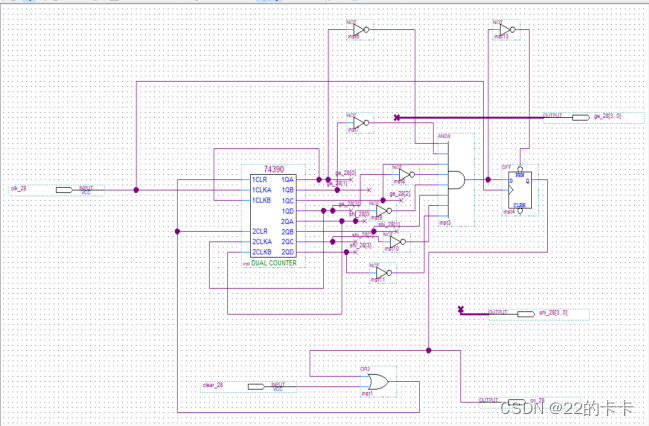

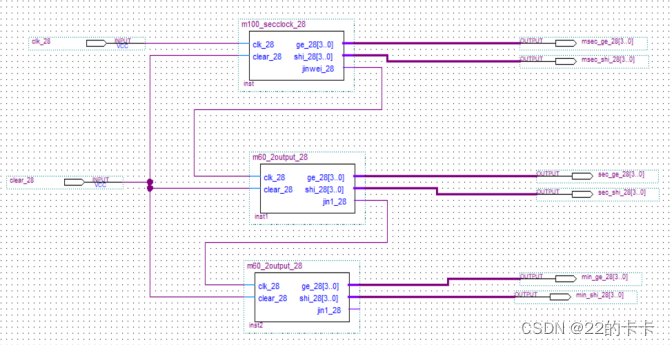

图1系统顶层设计电路图①

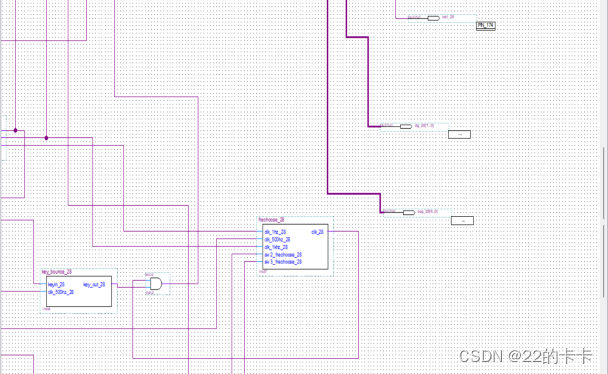

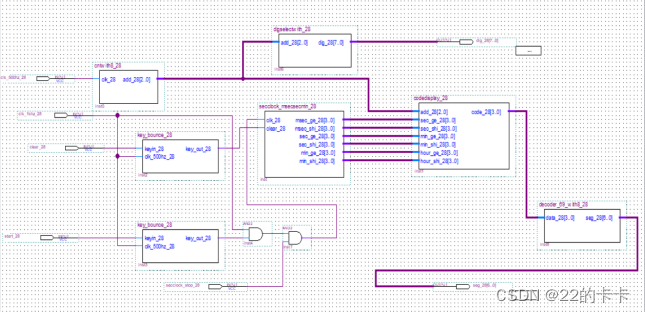

图2系统顶层设计电路图②

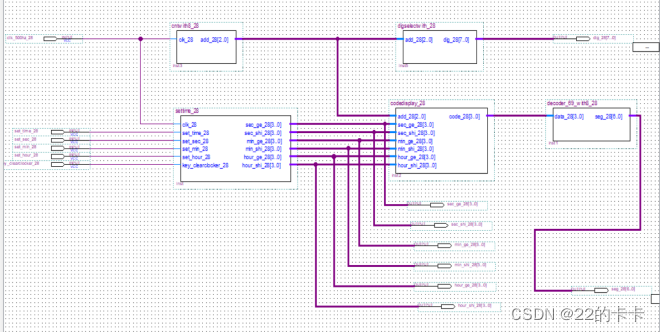

图3系统顶层设计电路图③

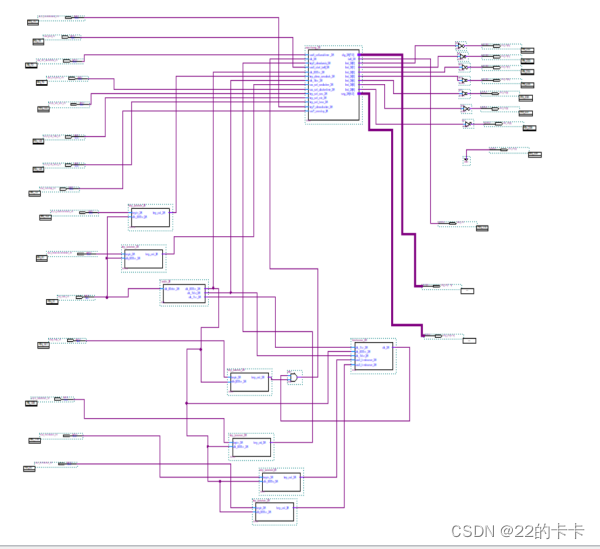

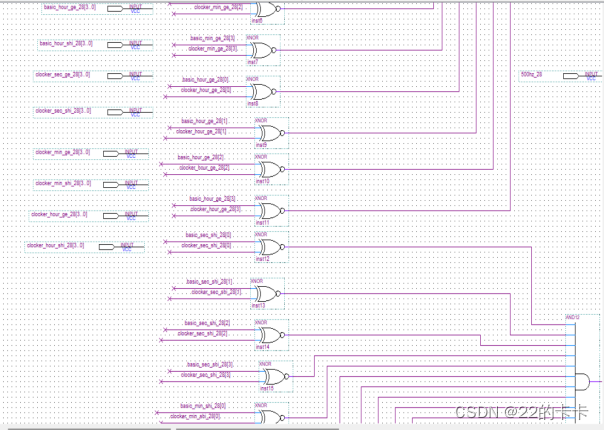

图4系统顶层设计电路图④

图5系统顶层设计电路图⑤

图6系统顶层设计电路图(总)

(3) 设计思路:

电路由4个基本功能和9个扩展功能组成。基本功能有秒计数,分计数,小时计数,进位。扩展功能有清零,暂停,调频,星期,闹钟模块,秒表模块,校时模块,69补段,加杠。

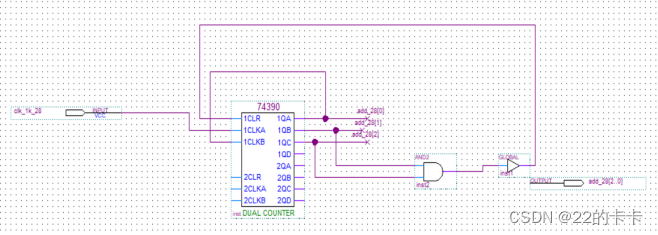

2.分频模块电路设计及仿真

(1)模块功能

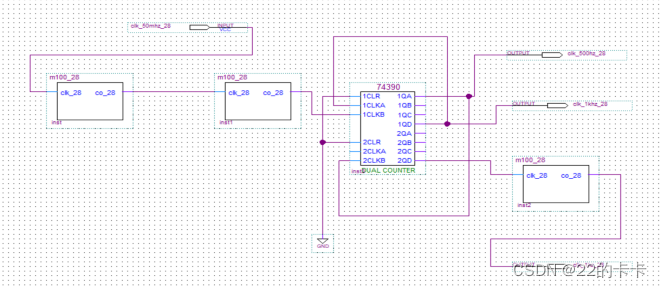

将50MHz的时钟信号分成500Hz,1KHz和1Hz三个频率。

(2)设计思路

利用74390芯片和模100的计数器进行分频,计数的模值就是频率的分频比。所以先用两个m100的计数器将频率分到5KHz,然后再利用74390的m5分到1KHz,用74390的m10分到500Hz,用74390的m50分到100Hz,然后再用一个m100得到1Hz。

(3)设计结果(电路)

图7分频功能电路图

(4)测试结果

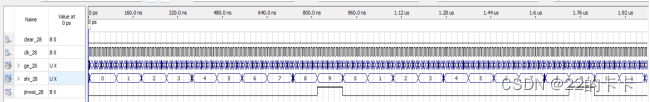

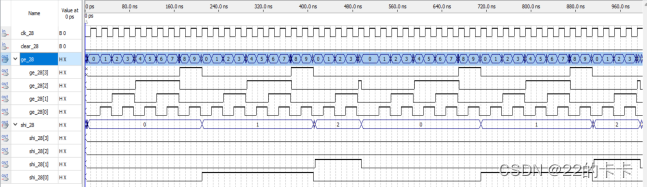

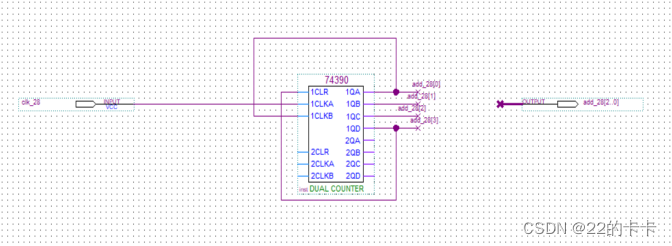

图8m100计数器波形图

(5)仿真波形数据分析

从00到99计数100次,并且在接近99的时候产生进位信号。然后又重新从0开始计数,所以仿真成功。

3.计时模块设计及仿真

3.1分、秒计时模块(模60计数)

(1)模块功能(计数、进位)

计数60次,并且将1QA-1QD作为个位输出,2QA-2QD作为十位输出。此外在暂态60(01100000)的时候进位,计数器同时清零。

(2)设计思路

利用74390芯片首先实现一个m100,然后当到达暂态60(01100000)的时候清零,可以得2QB和2QC相与的时候清零,同时可以将清零时候的时钟信号作为进位的脉冲,清零一次就进一次位。

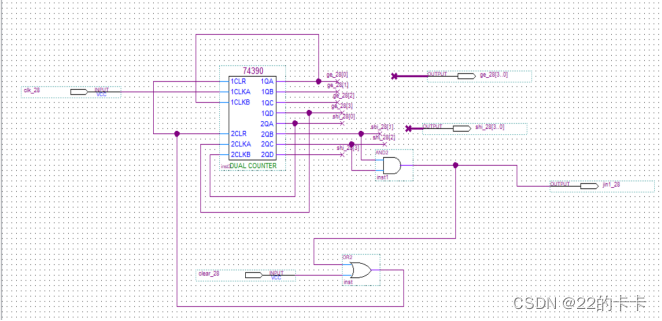

(3)设计结果(电路)

图9m60计数电路图

(4)仿真测试

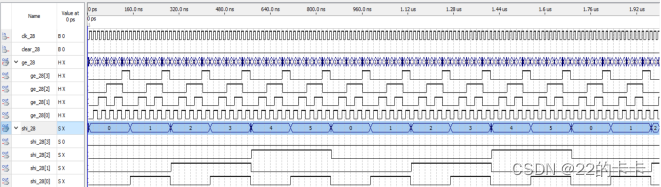

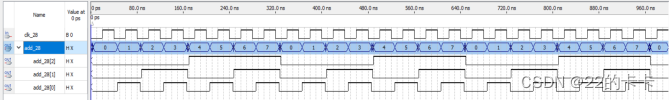

图10m60计数器波形图(两个周期)

图11m60计数器波形图(局部)

(5)仿真波形数据分析

个位从0到9,十位从0到5之后就清零,并且是从00到59依次出现。所以波形仿真结果正确。

3.2小时计时模块(模24计数)

(1)模块功能

计数24次,实现从0到23计数,当到暂态24(00100100)时清零,并且向前进位。并且将1QA-1QD作为个位输出,2QA-2QD作为十位输出。

(2)设计思路

利用74390芯片首先实现一个m100,然后当到达暂态24(00100100)的时候清零,同时可以将清零时候的时钟信号作为进位的脉冲,清零一次就进一次位。

(3)设计结果(电路)

图12m24计数器电路图

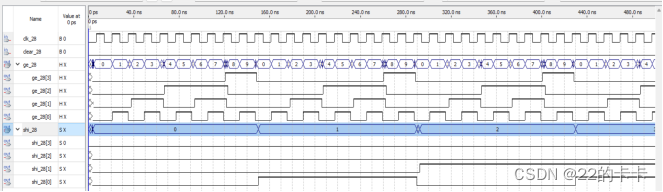

(4)仿真测试

图13m24计数器波形仿真图

(5)仿真波形数据分析

依次从00到23计数,当到达暂态24时,清零,又重新从00开始计数。所以仿真结果正确。

4.数码管动态显示模块

4.1动态显示模块的设计

(1) 设计思路:

利用人的视觉停留来实现动态显示功能,依次选择dig0-dig7的数码管,同时选择出数据的2进制码,然后将2进制码转换为数码管的七段码。

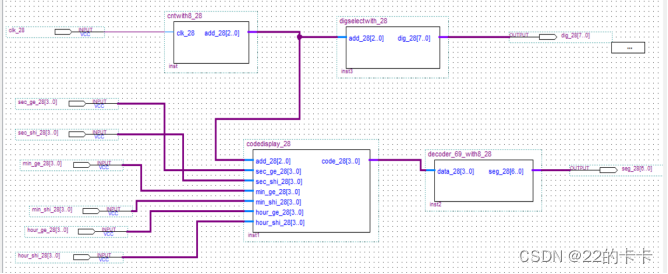

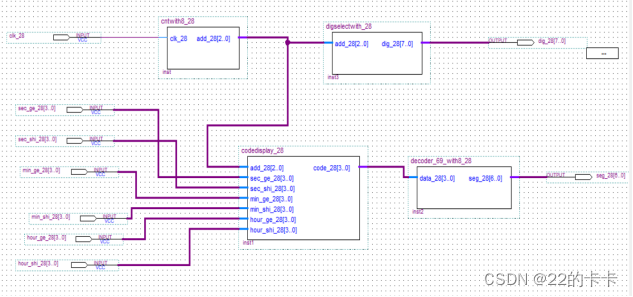

(2) 功能框图:

图14动态显示模块电路图

4.2扫描模块cnt6

(1)模块功能

从000到101计数6次,依次选择数码管dig0-dig5进行扫描。

(2)设计思路

首先做一个m10的计数器,当到暂态6(110)时清零。

(3)设计结果(电路)

图15扫描模块cnt6电路图

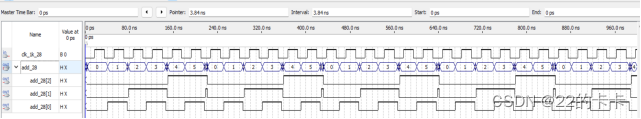

(4)仿真测试

图16扫描模块cnt6波形仿真图

(5)仿真波形数据分析

数据从0到5,当为6的时候就清零重新开始,所以仿真结果正确。

4.3位选模块dig_select

(1)模块功能

根据add_28[2…0]得到的地址,选择相应的数码管

(2)设计思路

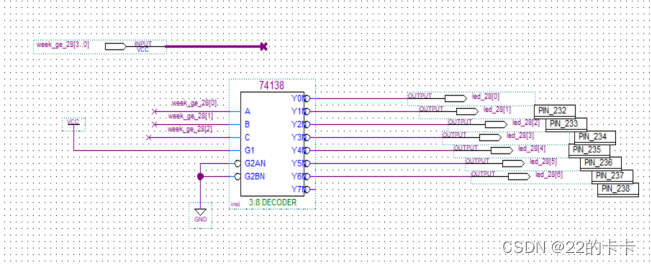

利用三线-八线译码器74138,将得到的地址转化为8位的二进制码,输出低电平的引脚就会被选择。

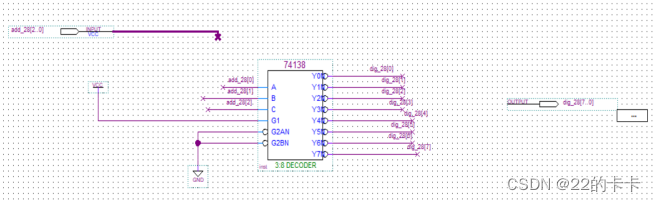

(3)设计结果(电路)

图17位选模块dig_select电路图

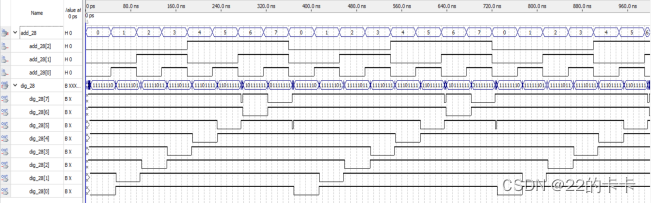

(4)仿真测试

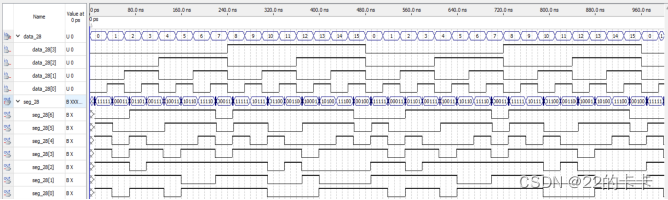

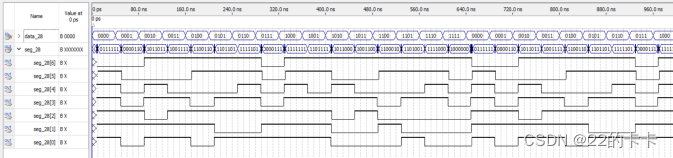

图18位选模块dig_select波形仿真图

(5)仿真波形数据分析

当add_28依次是0到7时,可以看到对应的dig_28输出低电平,就会被选择,所以成功。

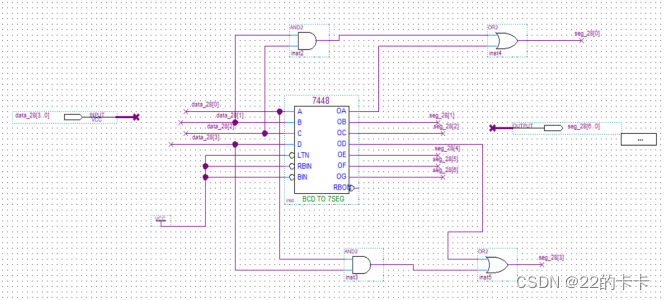

4.4译码模块

(1)模块功能

将二进制码转化为七段码,同时对6,9进行补段

(2)设计思路

因为7448具有译码的功能,可以将四位二进制数译码为七段码。此外,当为6(0110)的时候要补段a,所以当BC相与为1的时候要让seg[0]输出1;当9(1001)的时候补段d,所以AD相与为1的时候让seg[3]输出1。

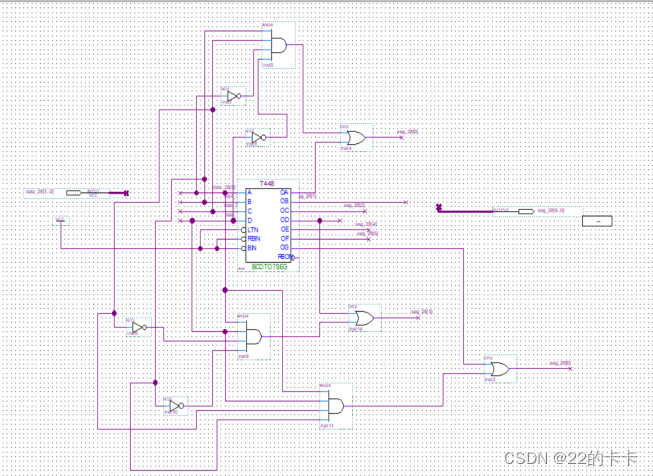

(3)设计结果

图19译码模块decoder电路图

(4)仿真测试

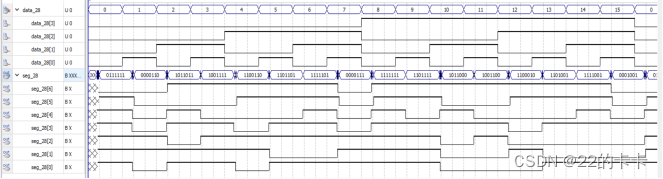

图20译码模块decoder波形仿真图(两周期)

图21译码模块decoder波形仿真图(一周期)

(5)仿真波形数据分析

这里主要是看0到9得到的seg的输出结果。当data为0的时候,只有seg[6]不亮,刚好是0的七段码正确,当为1的时候,seg[1]和seg[2]亮,可以也对应,依次看下去注意到6的时候已经补段成功了,seg[0]显示为,为9的时候,seg[3]显示为1。所以成功。

4.5动态显示模块电路图

图22动态显示模块电路图

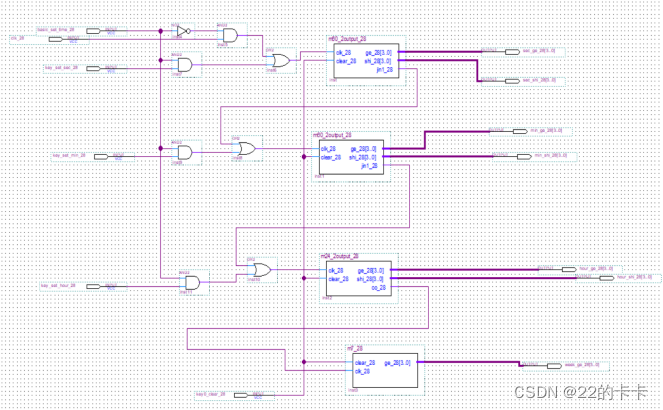

5.其他扩展功能

5.1手动校时模块

(1)模块功能

在电子钟的基础上可以设置时间,按不同的按钮一次,对应的时分秒就加一。

(2)设计思路

当按钮按下一次就给时钟信号一个脉冲,因为按下的时候刚好是一个上升沿,所以计数就会加一,实现校时功能。

(3)设计结果

图23校时模块关键电路图

5.2秒表模块

(1)模块功能

实现秒表的功能的清零,暂停,计时功能。

(2)设计思路

因为秒表是通过m100的毫秒然后进位到m60的秒,然后进位到m60的分钟,然后频率差不多是1khz,所以这里给时钟信号1khz,同时,我们将计数器的清零用一个按钮和原本的进位信号相或,就可以实现当按下按钮时,实现清零功能,同时,我们用一个开关控制暂停和开启,让开关和时钟信号相与,要一起开启才会开始,否则就会暂停时钟信号的输入。

(3)设计结果

图24秒表模块关键电路图

图25秒表模块整体电路图

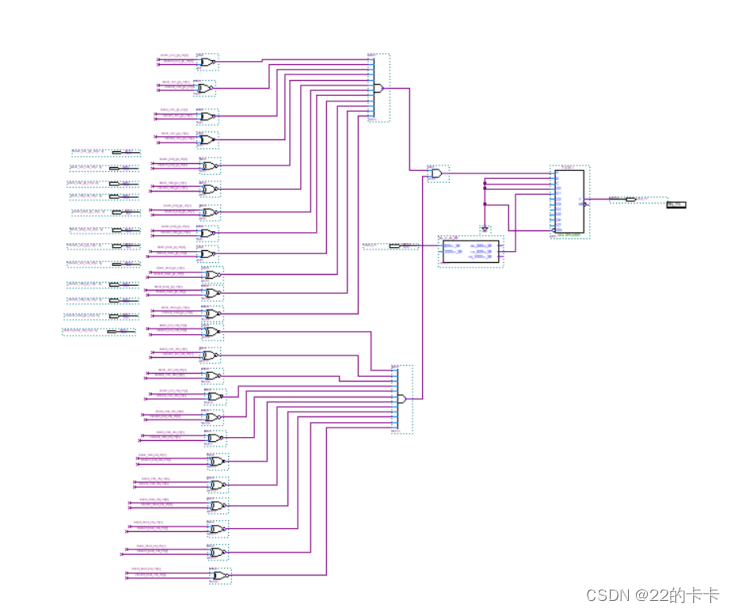

5.3闹钟模块

(1)模块功能

可以手动设置一个闹钟时间,然后让闹钟时间和电子钟时间进行比较,当到相同时间的时候蜂鸣器会发出声音。

(2)设计思路

首先设置闹钟时间和手动校时差不多,然后将闹钟和电子钟的时分秒的个位和十位通过同或门依次进行比较,当完全相同的时候就会让蜂鸣器发出声音。

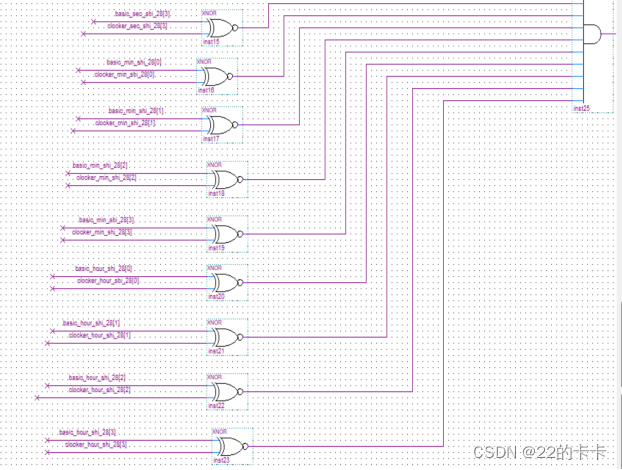

(3)设计结果

图26闹钟设置时间模块电路图

图27闹钟比较响铃模块电路图①

图28闹钟比较响铃模块电路图②

图29闹钟比较响铃模块电路图③

图30闹钟比较响铃模块电路图④

图31闹钟比较响铃模块电路图(总)

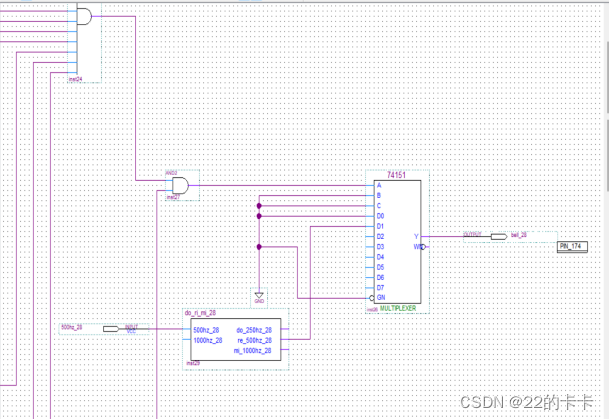

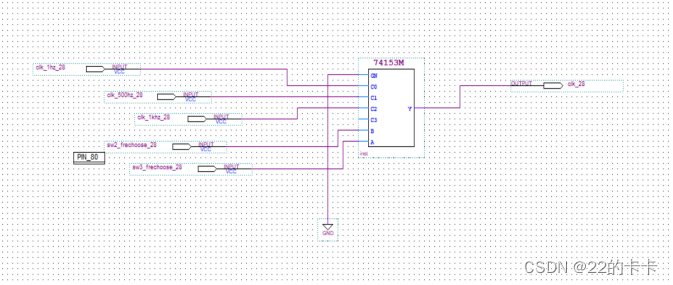

5.4调频模块

(1)模块功能

使用两个开关实现电子钟500hz,1khz,1hz和0hz的调节。

(2)设计思路

用74153四选一芯片,通过两个开关从四个不同频率的时钟脉冲里面进行选择。00为1hz,01为1khz,10为500hz,11为0hz。

(3)设计结果

图32调频模块电路图

(4)仿真测试

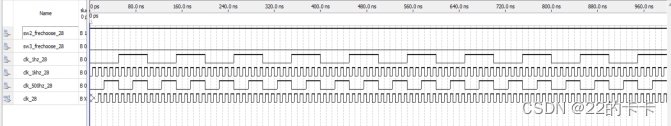

图33调频模块波形仿真图①(01)

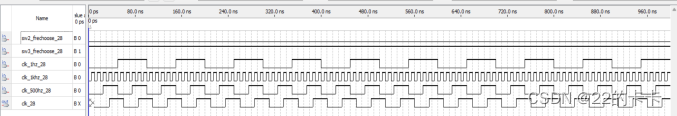

图34调频模块波形仿真图②(10)

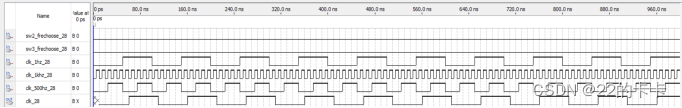

图35调频模块波形仿真图③(00)

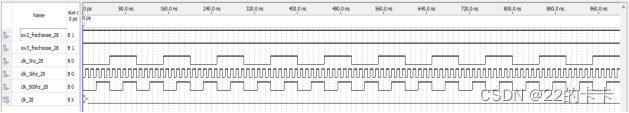

图36调频模块波形仿真图(11)

(5)仿真波形数据分析

当sw2sw3=01时,我们可以看到,clk输出为1khz的波形,当sw2sw3=10时,clk输出500hz的波形,当sw2sw3=11时,clk输出为0hz,当sw2sw3=00时,clk输出为1hz的波形。所以正确。

5.5星期模块

(1)模块功能

使用LED灯实现星期的显示。

(2)设计思路

通过一个由74161芯片组成的m7的计数器(我们先将ABCD置数0001,因为是m7,且是同步清零,所以当为7(0111)的时候清零,将QAQBQC相与后接到清零端),将时钟m24的进位信号作为星期m7计数器的时钟信号。然后使用74138译码器将m7的输出译为8位二进制码,将选择的数据作为低电平输出。

(3)设计结果

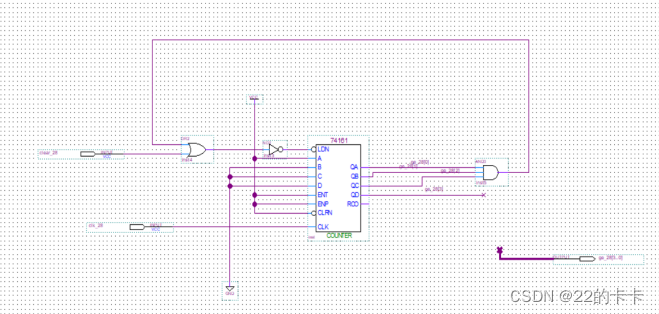

图37m7电路图

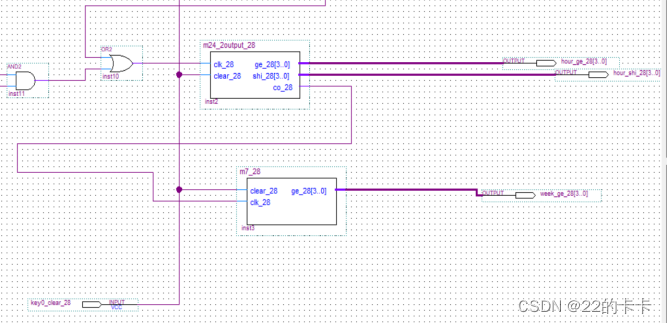

图38星期输出电路图

图39LED模块电路图

图40星期模块电路图

(4)仿真测试

图41m7波形仿真图

(5)仿真波形数据分析

可以看到数据是从1到7进行计数,仿真数据正确。

5.68位数码管显示功能

5.6.1 cnt8模块

(1)模块功能

显示8位数码管同时将第三个和第六个数码管显示杠。

(2)设计思路

将cnt6改为cnt8,同时让第三个和第六个数码管的code为1111。

(3)设计结果

图42m8电路图

(4)仿真测试

图43m8波形仿真图

(5)仿真波形数据分析

可以看到add从0到7依次计数,所以成功。

5.6.2译码模块decoder加杠

(1)模块功能

除了之前的对6,9补杠,还有将第三位和第六位显示杠。

(2)设计思路

因为第三位和第六为输出总是1111,所以当data为1111的时候seg_28[6]输出为1。

(3)设计结果

图44decoder模块电路图

(4)仿真测试

图45decoder模块波形仿真图

(5)仿真波形数据分析

可以看到除了之前对6,9的补段和其他0-9的数字的七段码正确之外,当七段码为1111的时候,只有seg[6]为1,其他seg都为0,正确。