热门标签

热门文章

- 1AI大模型时代,如何与大模型交流(Prompt)?应用实战告诉你!_prompt在ai领域的应用解析

- 2Hive优化的十大方法

- 3在MacOS中制作通义千问14B大模型的容器镜像_mac 搭建通义千问

- 4利用ESP32-C3将TF卡内容变成U盘进行读取_esp32 u盘

- 5Linux系统安装配置与使用_linux 操作系统服务器 的常用服务和应用的安装与配 置

- 6Python实现根据评论评分信息预测 (协同过滤,LFM,词向量)_评论预测评分代码

- 7发消息就用消息队列——kafka、rocketMQ(一)_消息队列的应用场景rockmq,kfaka

- 8Google的Apache Beam是什么_google beam

- 9Android应用开发学习笔记_下列选项中,()模式会判断要启动的activity实例是否位于栈顶,如果位于栈顶则直接复

- 10pritunl 和 JumpServer_pritunl客户端下载

当前位置: article > 正文

基于FPGA的以太网设计(4)----详解PHY的使用(以YT8531为例)_yt8531原理图设计参考

作者:秋刀鱼在做梦 | 2024-08-12 20:33:38

赞

踩

yt8531原理图设计参考

目录

3.1、Basic Control Register (0x00)

3.2、Basic StatusRegister (0x01)

3.3、PHY Specific Status Register (0x11)

文章总目录点这里:《FPGA接口与协议》专栏的说明与导航

1、前言

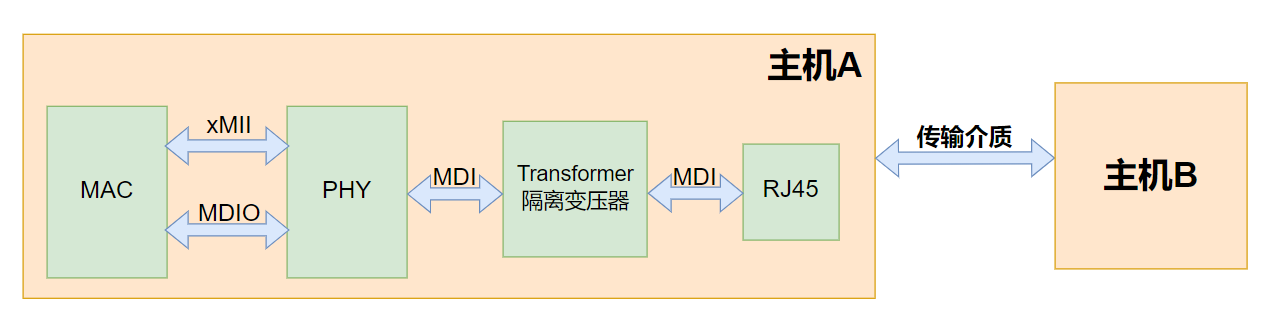

在前面的文章,我们已经了解了FPGA实现千兆以太网的电路架构,即 MAC + PHY + 变压器 + RJ45,其示意图如下:

变压器和RJ45实现的都只是电气方面的功能,比较简单,我们并不需要对其进行设置,所以不需要做过多了解。MAC的实现则是重点,它需要用FPGA写代码来实现数据链路层的功能,也就是说FGPA就是架构里的MAC(后面的文章会着重讲解如下实现这些功能)。

PHY呢?现在的千兆网主流方案基本都是使用独立的PHY(集成芯片),这意味着我们作为一个FPGAer,其实并不需要深入了解PHY的原理,只要了解PHY的对外接口,能正常地实现数据收发就行了。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/秋刀鱼在做梦/article/detail/971445

推荐阅读

相关标签