- 1八股文之linux中redis常用命令_linux redis 命令

- 2数据库-ER图转换为关系模型_数据库er图转换关系模型

- 34K智能处理平台机器视觉行业应用_4k图像实时检测

- 4kafka的leader和follower_kafka partition leader follow

- 5Comfyui 接入ollama出现502问题另一个解决方案_localhost访问ollama端口正常,ip访问出现502

- 6应急响应 Windows和Linux操作系统(查杀 后门木马,处理 勒索病毒.)_火绒linux进程叫什么

- 7Git命令-版本回滚_版本回滚相关的命令?

- 8极智芯中国芯 | 全网最全解读国产AI算力产品矩阵系列

- 9HIVE面试

- 10深度神经网络——什么是NLP(自然语言处理)?

利用SPI协议配置AD9361寄存器_spi clk频率

赞

踩

MSB代表一组二进制中最高位(一般为符号位),LSB代表二进制中的最低位。

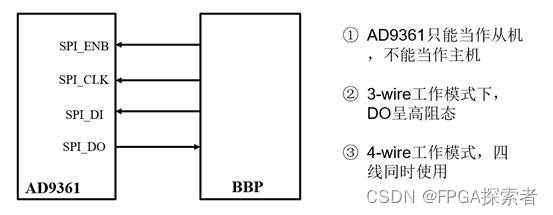

AD9361接口规范

串行外设接口(SPI)

SPI总线为AD9361的全数字控制提供了可能。每个SPI寄存器的位宽为8位,每个寄存器包含控制位、状态监测或控制设备所有功能的其他设置。以下各节解释了该接口的细节。

SPI功能层

![]()

可以通过设置SPI寄存器0x000中的位值来配置SPI总线。寄存器0x000是对称的;也就是说,

D7相当于D0,

D6相当于D1,

D5相当于D2

D4和D3未使用

设备在默认模式(MSB优先寻址)下通电,但由于这种对称性,可以接受LSB首次写入0x000。对称位一起被OR,所以设置一个位就可以同时设置这两个位。正确配置后,所有后续寄存器写入必须遵循所选格式。

默认情况下,总线配置为4线接口。D7和D0置0然后才能更改其他寄存器。寄存器0x000的默认状态为0x00。

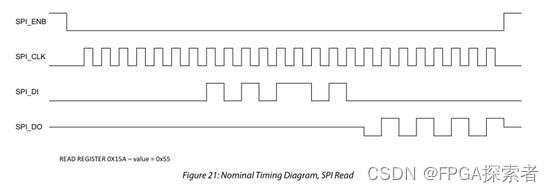

SPI_ENB(片选引脚,低电平选中)

SPI_ENB是从BBP驱动至AD9361的总线使能信号。在第一个SPI_CLK上升沿之前,SPI_ENB拉低,而在最后一个SPI_CLK下降沿之后,SPI_ENB通常再次拉高。

当SPI_ENB为高电平,SPI_DO和SPI_DI引脚为高阻态,AD9361忽略时钟和数据信号。

如果AD9361是SPI总线上的唯一设备,则SPI_ENB可以连接到低位。

如果在任何通信循环中SPI_ENB被驱动为高电平,该循环将暂停,直到SPI_ENB被重新激活为低电平。

SPI_CLK

SPI_CLK是BBP驱动AD9361的接口参考时钟。它仅在SPI_ENB较低时激活。最大SPI_CLK频率为50 MHz。

SPI_DI, SPI_DO and SPI_DIO

当配置为4线总线时,SPI利用两个数据信号SPI_DI和SPI_DO。

SPI_DI是从BBP到AD9361的数据输入线,

SPI_DO是在这种配置下从AD9361到BBP的数据输出。

当配置为3线总线时,SP_DI用作双向数据信号,接收和传输串行数据。

数据信号由BBP和AD9361在SPI_CLK的上升沿发射,并在SPI_CLK的下降沿采样。SPI_DI(或SPI_DIO)将控制字段从BBP传输到AD9361,在写入时将写入数据字段传输到AD9361。SPI_DO(或SPI_DIO)在读取时将返回的读取数据字段从AD9361传输到BBP。

AD9361在这些引脚上不提供任何微弱的上拉或下拉。当SPI_DO处于非活动状态时,它在高阻抗状态下浮动。如果始终需要SPI_DO上的有效逻辑状态,则应在PCB上添加外部弱上拉/下拉。

SPI DATA TRANSFER PROTOCOL

AD9361 SPI是一种灵活的同步串行通信总线,允许与许多行业标准微控制器和微处理器无缝接口。串行I/O与大多数同步传输格式兼容,包括摩托罗拉SPI和英特尔SSR协议。AD9361的控制字段宽度仅限于16位,并且允许多字节IO操作。AD9361不能用于控制总线上的其他设备,它只能作为从设备运行。

一个通信周期分为两个阶段。

第一阶段是控制周期,即将控制字(指令+地址)写入AD9361。阶段1的控制字段定义即将进行的数据传输是读还是写。它还定义了正在访问的寄存器地址。

第二阶段是(数据)交换阶段。

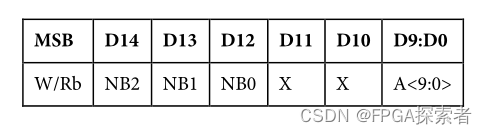

第一阶段的指令格式

16位控制字段包含以下信息:

W/Rb:1写 0读

D11:D10:指令字的<11:10>位未使用

D9:D0:指定IO操作第2阶段期间数据传输的起始字节地址

所有字节地址,包括起始地址和内部生成的地址,都被认为是有效的。也就是说,如果访问了无效地址(未定义的寄存器),IO操作将继续,就像地址空间是有效的一样。对于写操作,写入位被丢弃,而读操作在输出端产生逻辑零。

第二阶段数据交换

单字节数据传输:

当NB2、NB1和NB0都为零时,选择单字节数据传输。紧随地址位的结束,八个数据位会写入到SPI寄存器或从该寄存器读出八位数据。之后,通信进入空闲状态或紧接着写下一个指令周期。

多字节数据传输:

当NB2、NB1和NB0都非零时,选择多字节数据传输。在此模式下传输的数据的格式和顺序取决于设备是配置为LSB first还是MSB first数据传输。

LSB first:紧随地址位的结束,有X个字节会依照起始地址自增,依次写入到这些SPI寄存器或从这些寄存器读出八位数据。之后,通信进入空闲状态或紧接着写下一个指令周期。

MSB first:紧随地址位的结束,有X个字节会依照起始地址自减,依次写入到这些SPI寄存器或从这些寄存器读出八位数据。之后,通信进入空闲状态或紧接着写下一个指令周期。

时序图

- NB2、NB1、NB0:指明第二阶段传输数据字节数

- D7和D0:1,重置所有SPI寄存器为默认值

- D6和D1:1,3-wire SPI模式;0,4-wire SPI模式

- D5和D2:1,LSB First;0,MSB First

- D4和D3:未使用

- AD9361的SPI寄存器地址是十位宽

- SPI配置寄存器具有对称性,或运算