热门标签

热门文章

- 1关于安卓以及微软用户chatgpt上一篇文章如今第五点无法正常进入更新解决方法以及附加本地部署_chat-shared1.zhile.i/shared.html

- 2ai取代程序员_未来50%的工作都将被人工智能给取代,程序员会被机器人取代吗?...

- 3集群分为几种,用的软件分别是什么?_集群软件是啥

- 4本科论文查重会检测AI辅写疑似度吗?一篇文章为你揭秘!_查重率包括aigc吗

- 5【Planning】路径规划方法汇总_深度学习 planning方法汇总

- 6MAC 安装 Homebrew(使用国内镜像源)

- 7第十四届蓝桥杯大赛软件赛省赛(C/C++ 大学B组)_第十四届蓝桥杯大赛软件赛决赛 ca-6

- 8机器学习中的判别式模型和生成式模型_人工智能 区分式模型 生成式模型

- 9计算文本相似度_lstm段文本相似度

- 10oracle左连接查询从表去重,oracle查询/子查询/复制表和数据

当前位置: article > 正文

FPGA_学习_15_IP核_VIO_fpga vio

作者:繁依Fanyi0 | 2024-03-24 17:26:46

赞

踩

fpga vio

前一篇博客我们提到在线调试的时候, 可执行文件只要烧进板子,程序它就会自己跑起来,不会等你点

这个按钮,它才开始跑。我们测试的模块中,里面可能有几个我们关心的信号,它会在程序刚运行很短的时间内发生状态跳变。 当我们打算去捕获它的状态变化的时候,这个时候程序已经跑过了,这导致我们无法抓取到。那这个时候我们应该怎么办呢? 引入VIO这个工具,用VIO的输出信号作为我们测试模块的使能信号,这样我们就能控制待测试的模块什么时候运行。

VIO是个特别简单的IP核,丝毫不用有畏难情绪。

1 VIO是什么

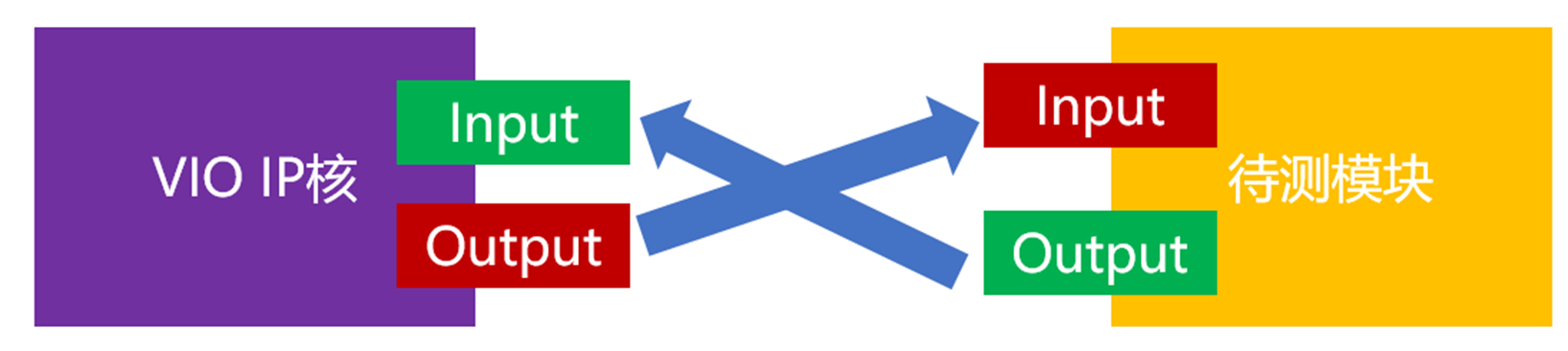

VIO是虚拟输入/输出(Virtual Input/Output),可以实时监测和驱动FPGA内部信号。 在线调试的时候,Vivado会提供一个VIO的界面,你可以修改VIO对待测模块的输出,也可以监测待测模块对VIO的输入。VIO和待测模块的信号如下图所示,就行串口通信一样,你的Tx要接到我的Rx,

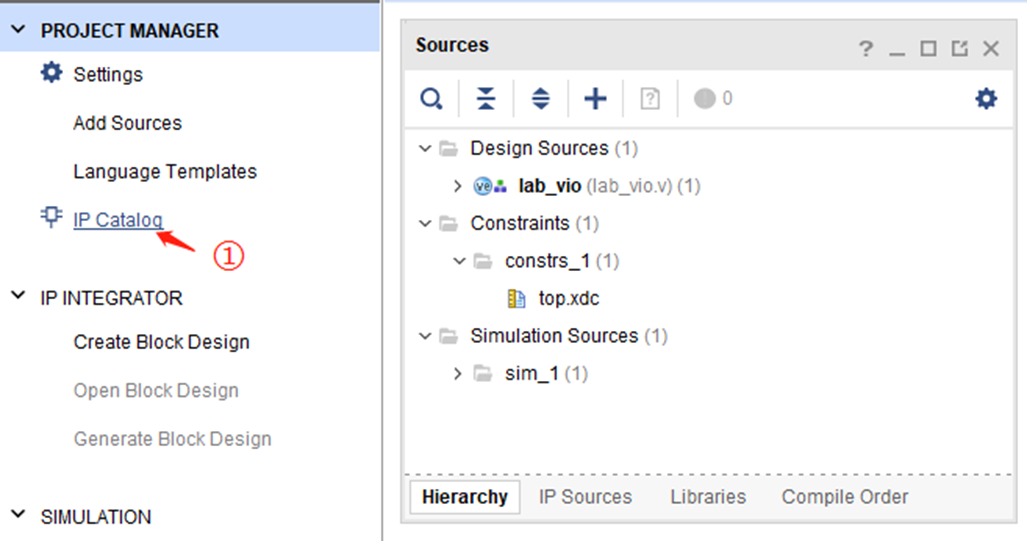

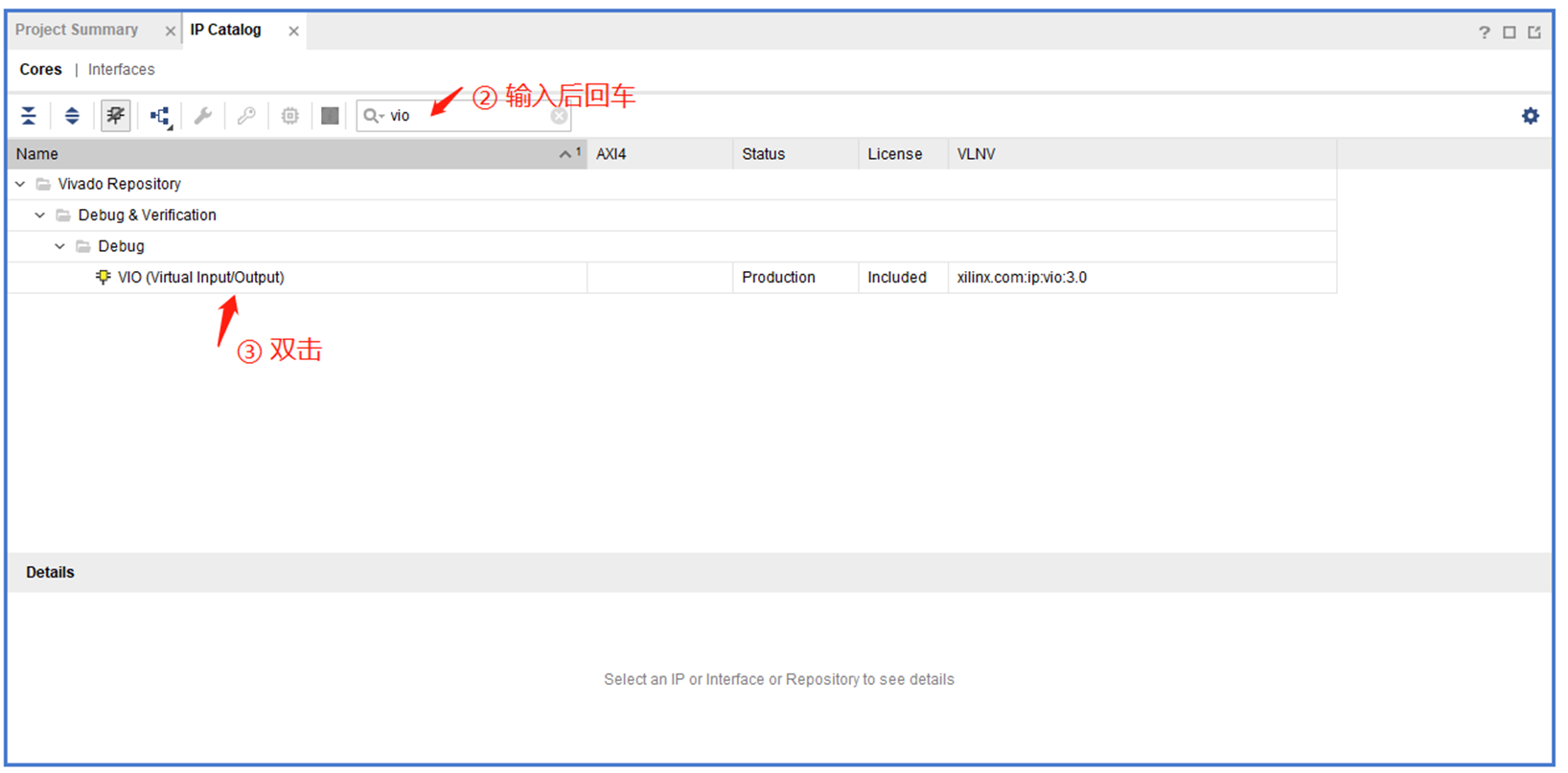

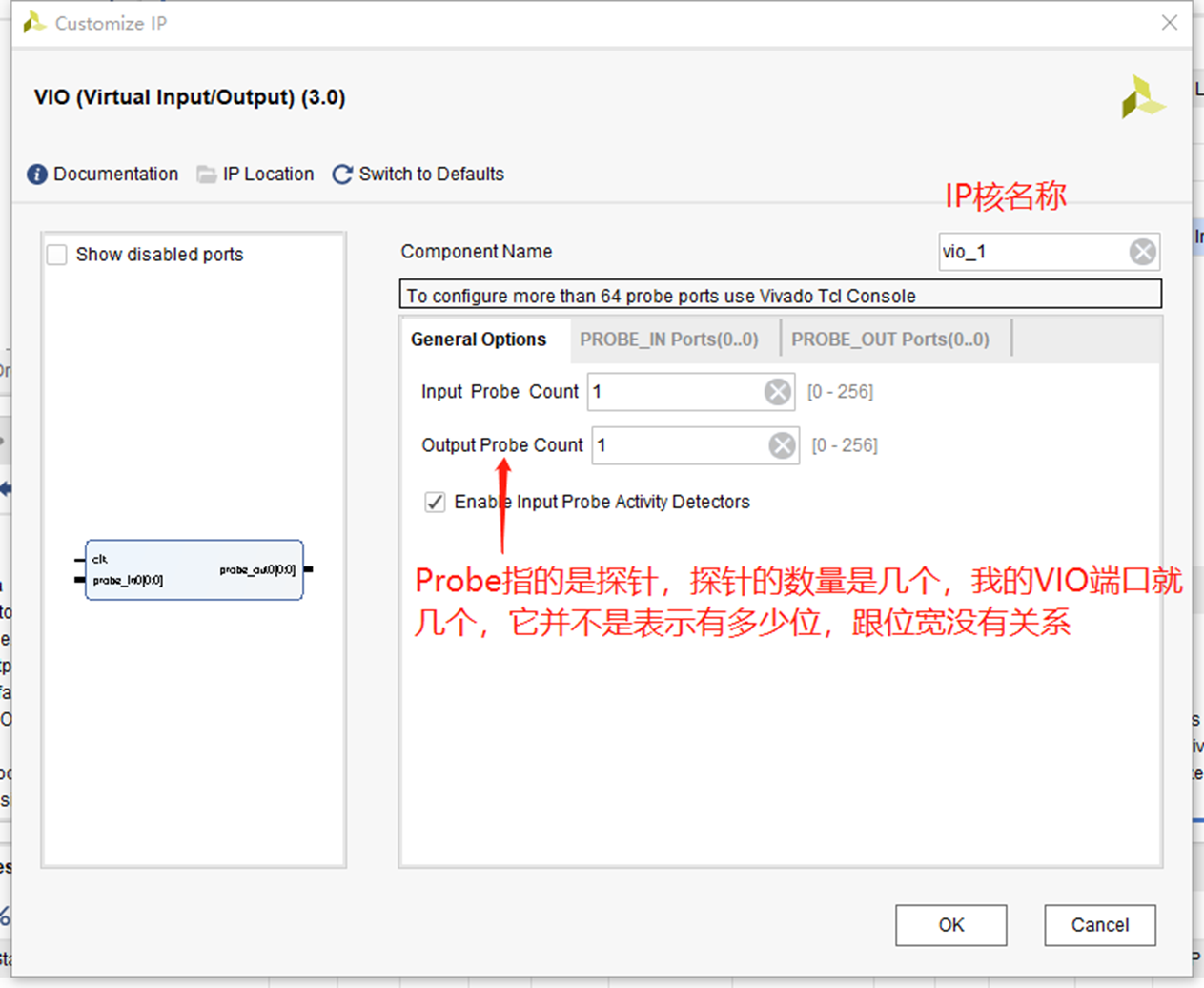

2 VIO IP 配置

截图警告!

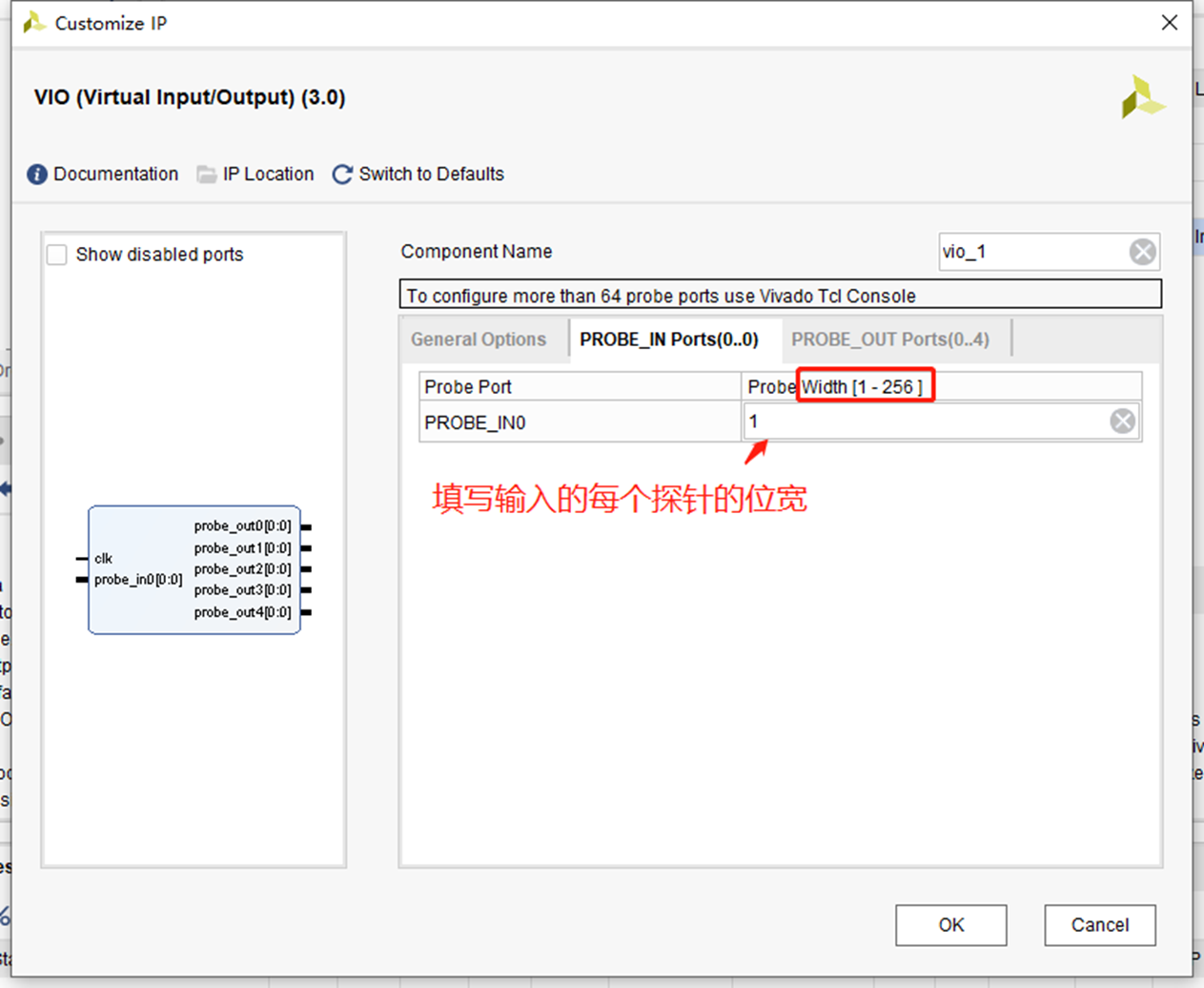

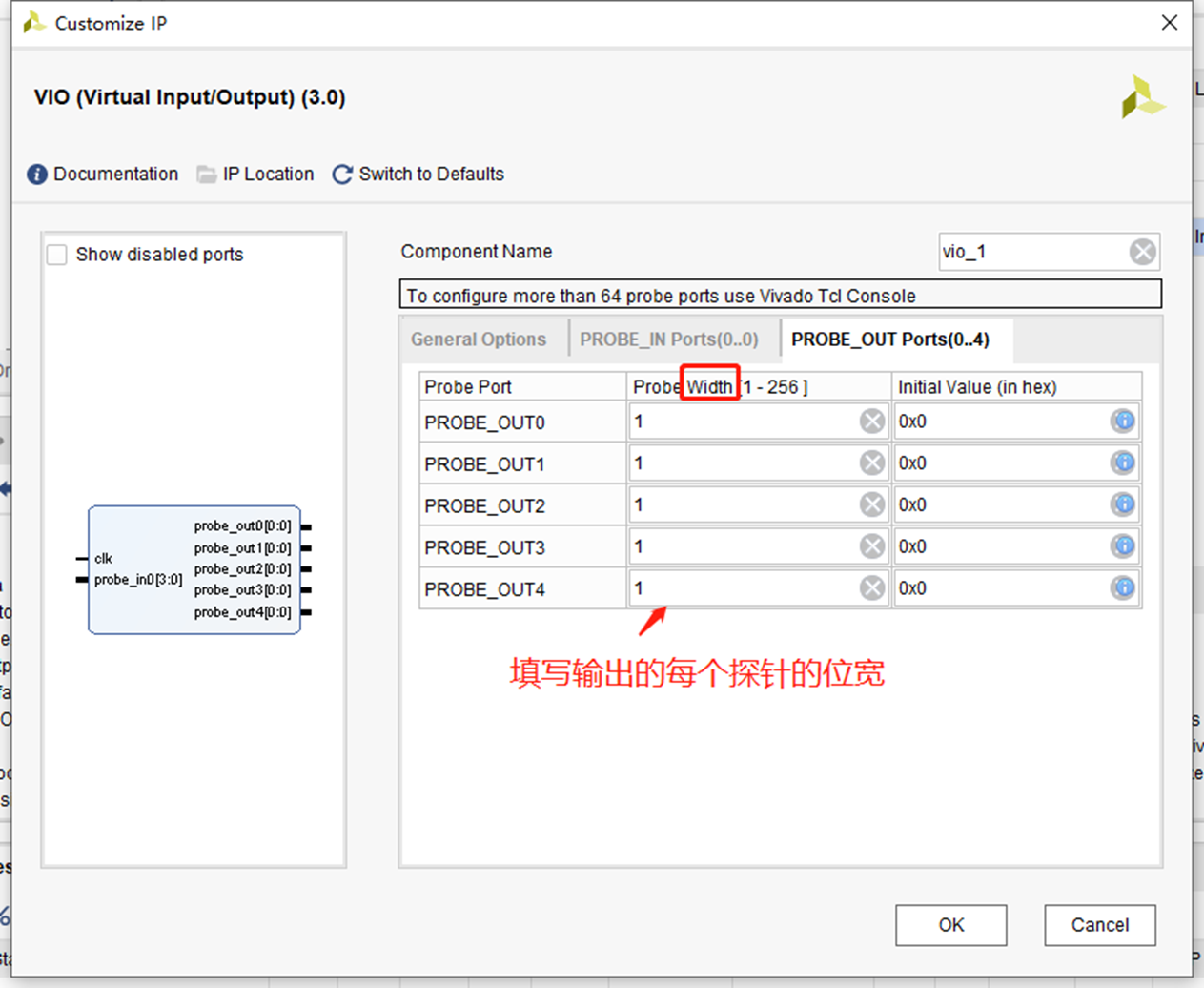

我对下面这个截图稍微补充一下哈, 截图只是在介绍这个东西是什么,而我们的VIO例程里,这输入探针数量是1,输出探针数量是5。 IP核名称是vio_0。

我对下面这个截图稍微补充一下哈, 截图只是在介绍这个东西是什么,而我们的VIO例程里,这输入探针位宽是4。

我对下面这个截图稍微补充一下哈, 截图只是在介绍这个东西是什么,而我们的VIO例程里,这5个输出探针位宽是2。

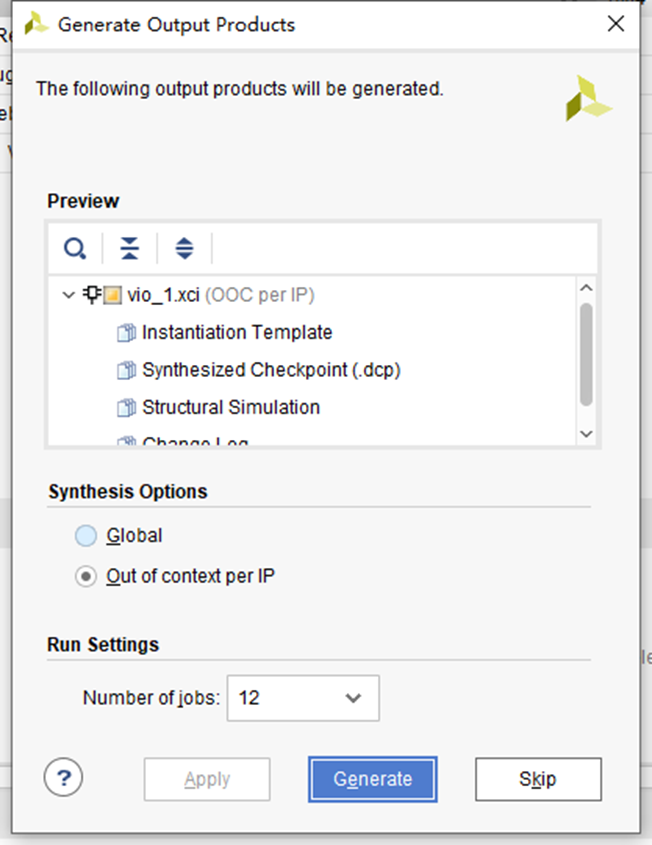

Ok之后直接Generate

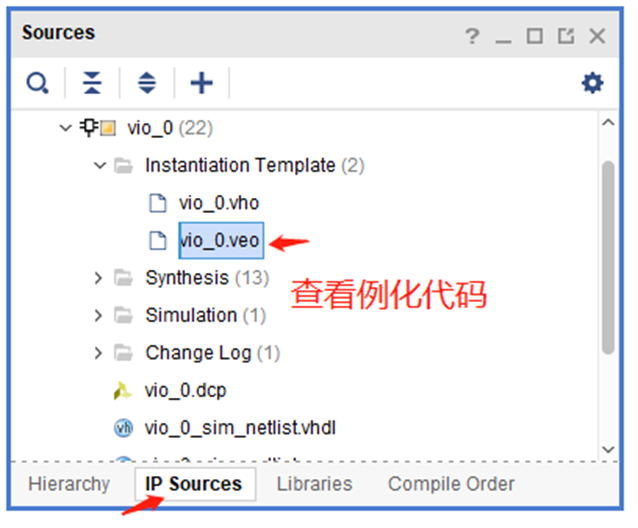

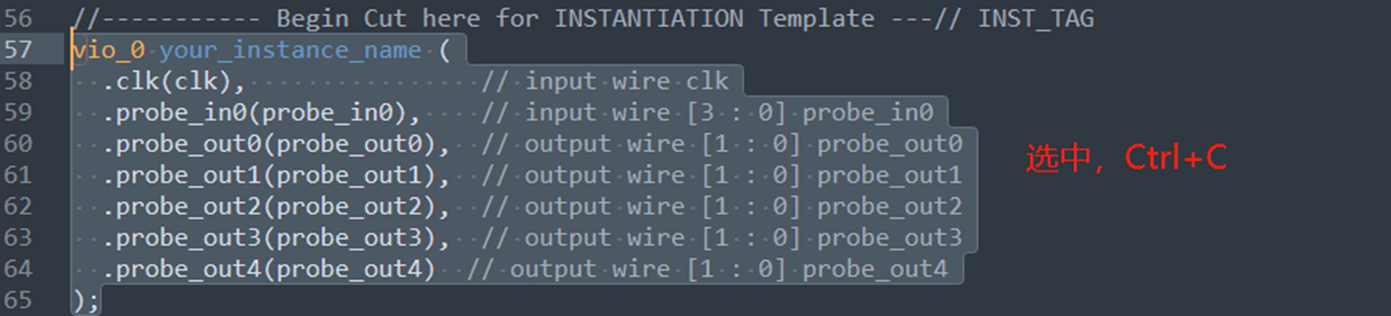

IP核生成完了之后,都要去抄一下怎么例化。

3 VIO测试用例:4选1-选择器

- `timescale 1ns / 1ps

-

- module lab_vio(

- input wire clk

- );

-

- reg [3:0] out; // 待测模块的输出 VIO的输入

- wire [1:0] a, b, c, d; // VIO的输出 待测模块的输入

- wire [1:0] sel; // VIO的输出 待测模块的输入

-

- always @(*) begin

- case(sel)

- 2'b00: out <= a;

- 2'b01: out <= b;

- 2'b10: out <= c;

- 2'b11: out <= d;

- default: out <= 2'bx;

- endcase

- end

- vio_0 vio_0_inst (

- .clk(clk), // input wire clk

- .probe_in0(out), // input wire [3 : 0] probe_in0

- .probe_out0(a), // output wire [1 : 0] probe_out0

- .probe_out1(b), // output wire [1 : 0] probe_out1

- .probe_out2(c), // output wire [1 : 0] probe_out2

- .probe_out3(d), // output wire [1 : 0] probe_out3

- .probe_out4(sel) // output wire [1 : 0] probe_out4

- );

- endmodule

管脚约束代码,我们只用到了clk

- create_clock -period 20.000 [get_ports clk]

- set_property PACKAGE_PIN N18 [get_ports clk]

- set_property IOSTANDARD LVCMOS33 [get_ports clk]

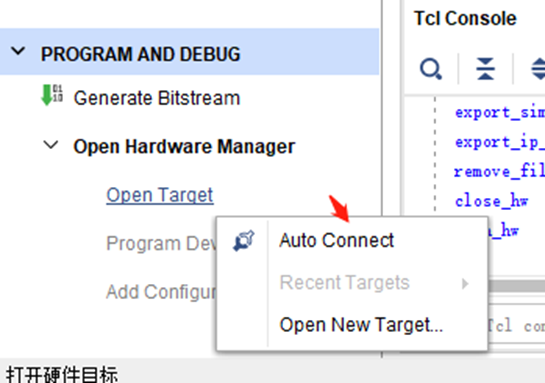

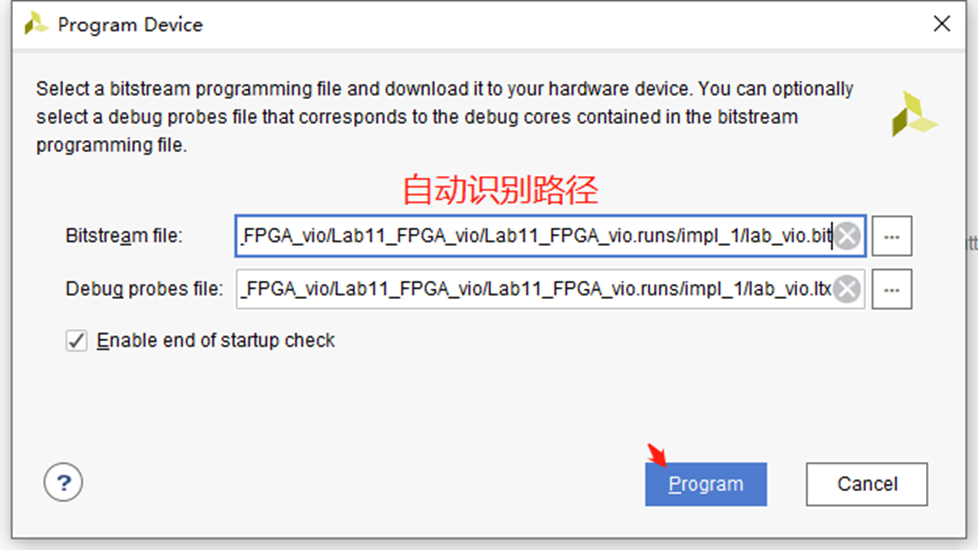

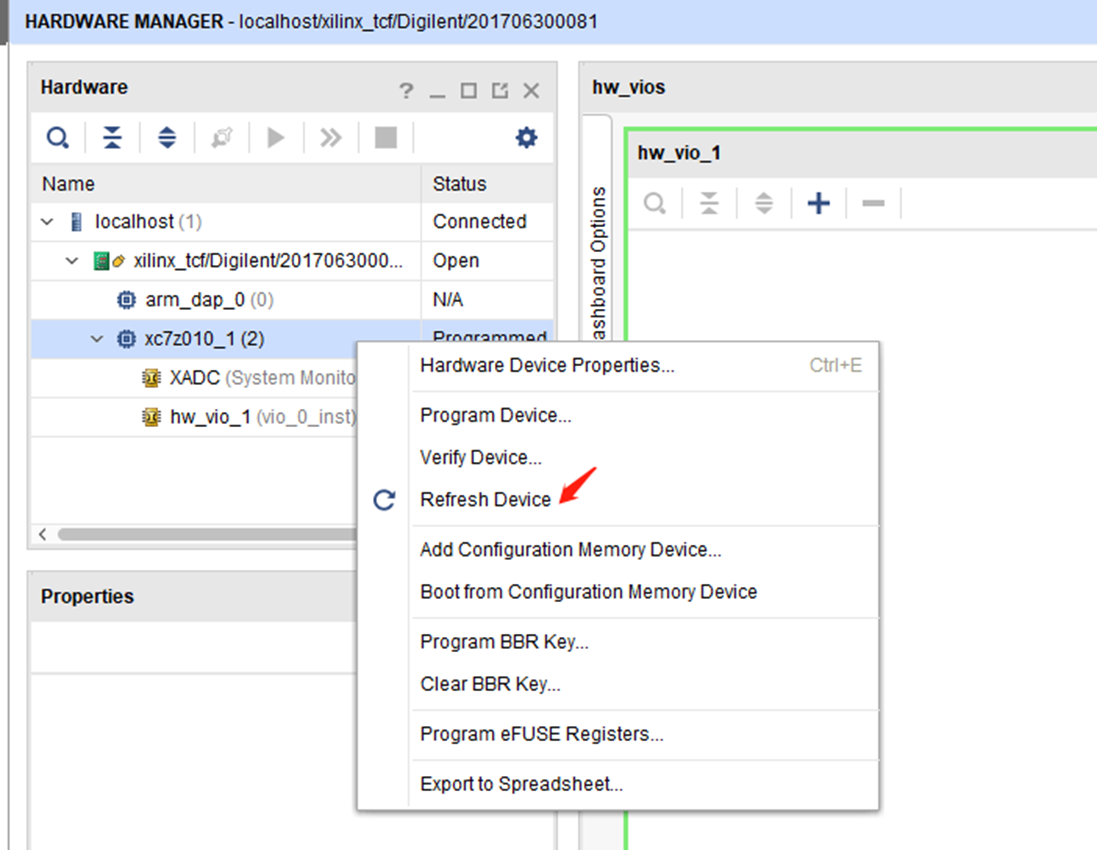

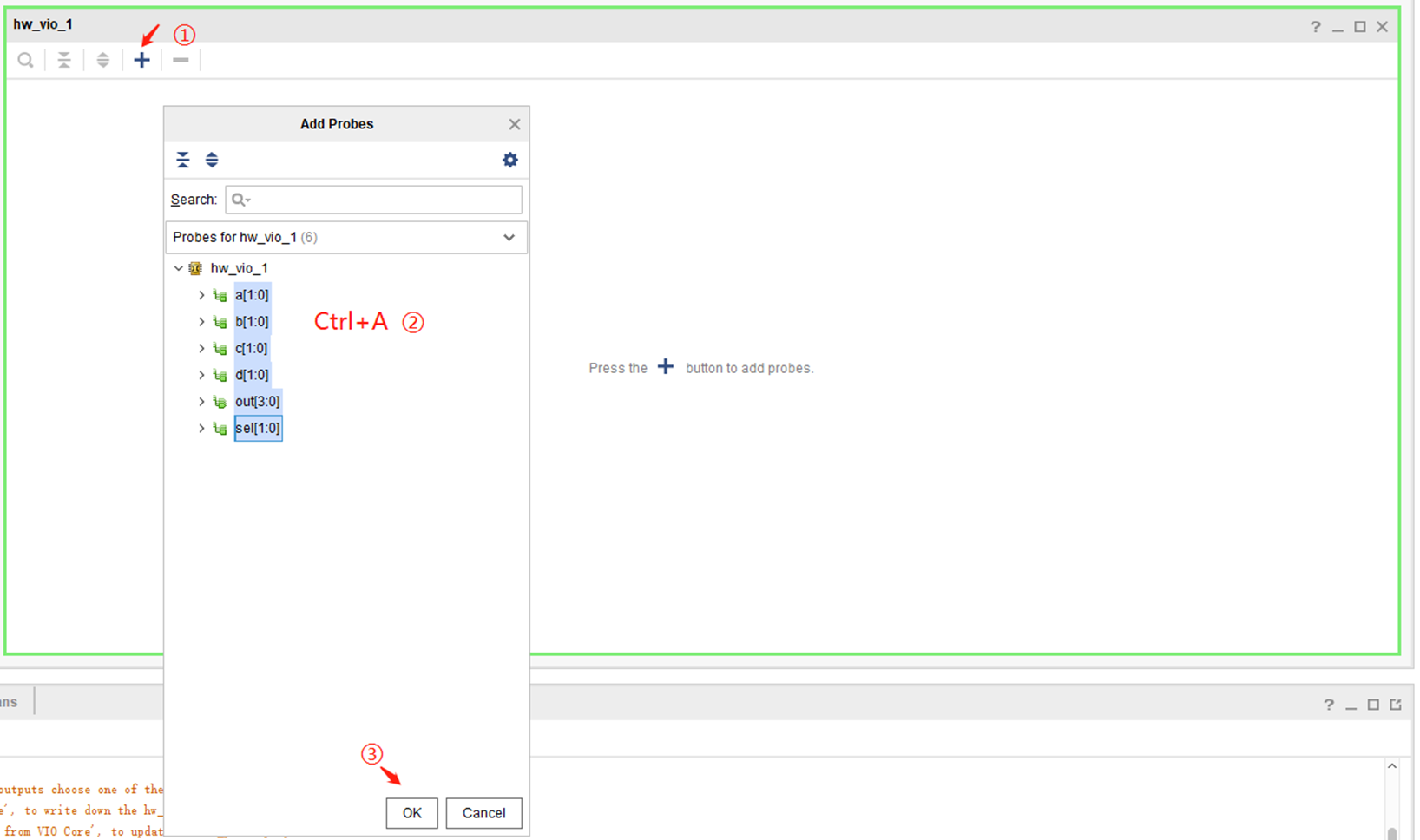

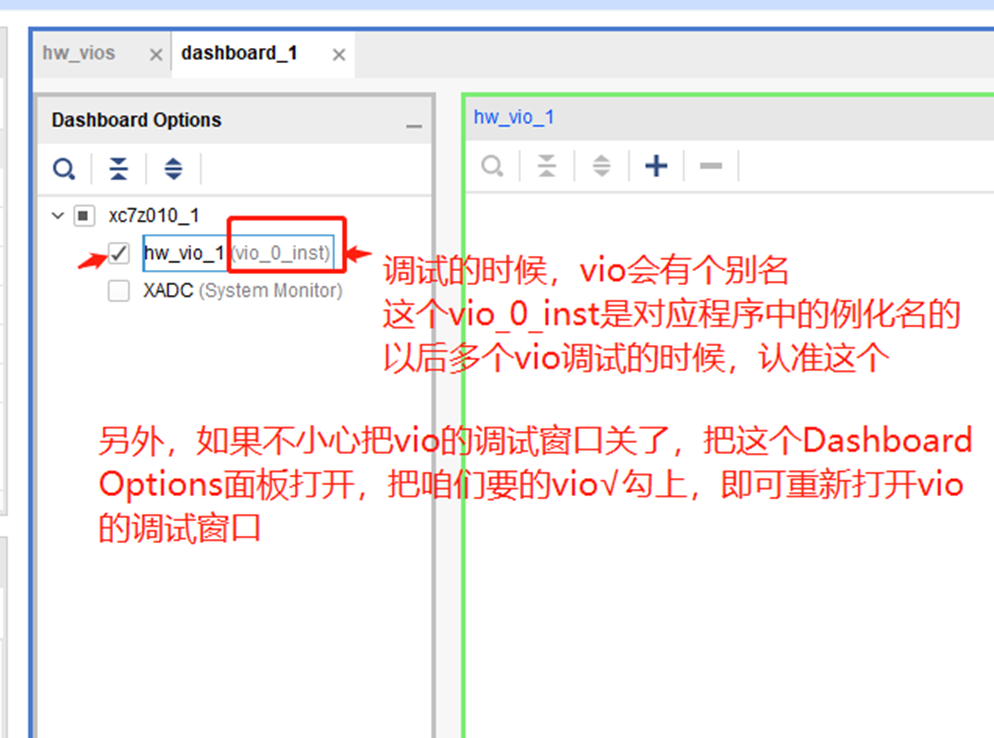

4 在线调试

截图警告!

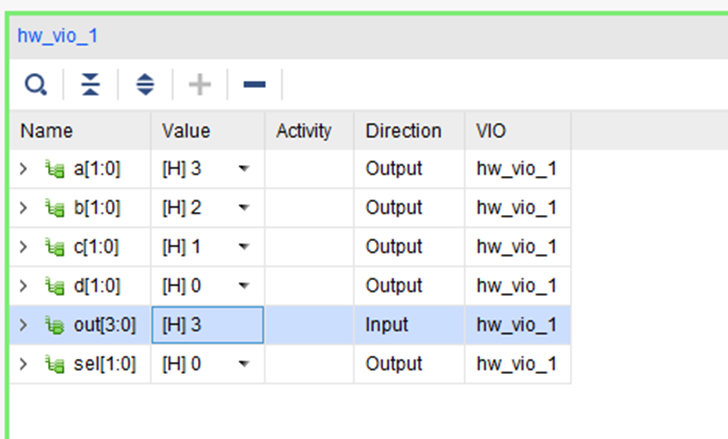

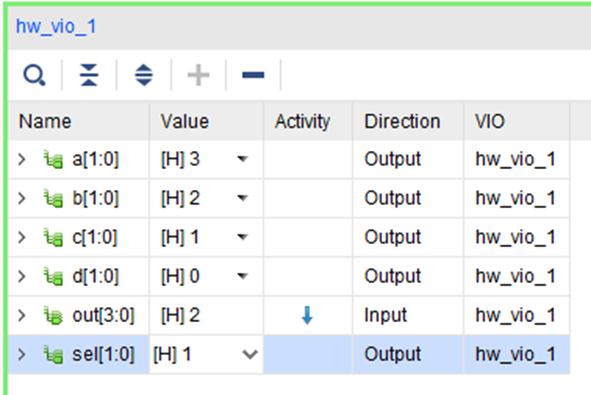

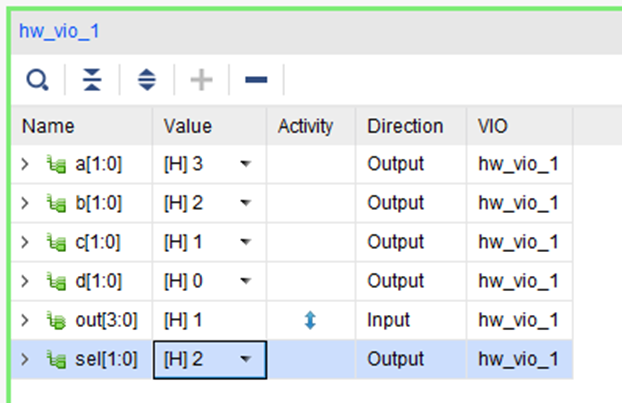

假设我设置 a b c d 分别为3 2 1 0, 然后分别设置sel为0 1 2 3,检测out的变化

|  |

|  |

通过以上的小实验呢,我们就算是基本掌握VIO的用法了,是不是很简单呢?

参考文献

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/繁依Fanyi0/article/detail/303841

推荐阅读

相关标签