- 1Google 的 C++ 代码规范_c++编码规范下载 google

- 2应用软件系统开发-双碳源系统(包调试,安装)

- 3玩转DB里的数据—阿里云DMS任务编排之简介和实操_阿里云 时间变量 任务怎么设置

- 4员工跳槽,你怎么办?_员工跳槽有信心危机怎么解决

- 5matlab三踪示波器,3.2 示波器CSV数据导入MATLAB

- 6jsonhandle 插件下载_json-handle插件下载

- 7ZooKeeper JMX enabled by default Using config......完美解决_jmx enabled by default using config: /usr/apps/zoo

- 8外包能转正吗?外包员工能变正式员工吗?_外包转正式是不是很难

- 9字节跳动测试开发岗 3+1 面经+经验分享(收到offer,入职月薪27K)_字节跳动测试开发岗位面经

- 10C++ STL list详解_c++弹出list头元素

DDS原理与实现

赞

踩

一、DDS基本原理

DDS(Direct Digital Synthesizer)即数字合成器,是一种新型的频率合成技术,具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点。较容易实现频率、相位以及幅度的数控调制,广泛应用于通信领域。

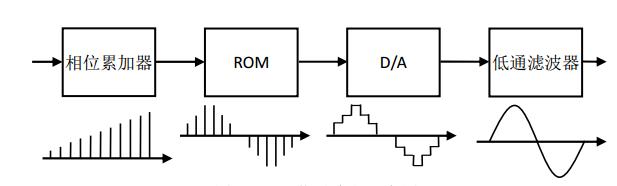

DDS 的基本结构图如图所示:

由图可以看出,DDS主要由相位累加器、相位调制器、波形数据表以及 D/A 转换器构成。

其中相位累加器由 N 位加法器与 N 位寄存器构成。每个时钟周期的时钟上升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是DDS输出的信号频率。相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。波形存储器的输出数据送到D/A转换器,由D/A转换器将数字信号转换成模拟信号输出。

DDS 信号流程示意图如图所示:

这里相位累加器位数为N位(N的取值范围实际应用中一般为24~32),相当于把正弦信号在相位上的精度定义为N位,所以其分辨率为1/2N。

若DDS的时钟频率为Fclk,频率控制字fword为1,则输出频率为Fout=Fclk/2N,这个频率相当于“基频”。若fword为B,则输出频率为Fout= B×Fclk/2N。

从上式分析可得,当系统输入时钟频率Fclk不变时,输出信号频率由频率控制字B所决定,由上式可得:B=2N×Fout/Fclk。其中B为频率字且只能取整数。为了合理控制ROM的容量,此处选取ROM查询的地址时,可以采用截断式,即只取32位累加器的高M位。这里相位寄存器输出的位数一般取10~16 位。

一个完整周期的正弦信号的波形总共有 33 个采样点,其中第 1 点和第

33 点的值相同,第 33 点为下一个周期的起始点,因此,实际一个周期为 32 个采样点