热门标签

热门文章

- 1Kafka【第一篇】Kafka集群搭建

- 2【Python BUG】anaconda安装报错Error:Cannot unpack file_anaconda安装报错cannot up

- 3Windows Git的安装_windows git 安装

- 4Meta开源多感官大模型,AI用6种模态体验虚拟世界,听引擎声就会画汽车|CVPR2023...

- 5Verilog学习笔记(5):Verilog高级程序设计_verilog 多项式乘法

- 6安装部署Stable Diffusion WebUI实现AI绘画_commit hash: cf2772fab0af5573da775e7437e6acdca424f

- 7Python 异常的传递性_python的异常传递

- 8HBase介绍 HBase和HDFS的联系 HBase和RDBMS的联系_hdfs hbase

- 9JAVA版12306订票代码分享_12306抢票java

- 10AI辅写疑似度高风险?七步改写策略助你化险为夷!_论文aigc 降低

当前位置: article > 正文

VHDL 4-16译码器 三位十进制加法计数器 原理图文件创作bdf创作_vhdl设计4线16线译码器

作者:繁依Fanyi0 | 2024-06-06 05:04:15

赞

踩

vhdl设计4线16线译码器

本文讲述vhdl中如何进行原理图文件编辑,即bdf文件的设计,设计内容为以下三点,详细制作过程,图文描述,逐一讲解步骤PDF以及源程序均在文末链。

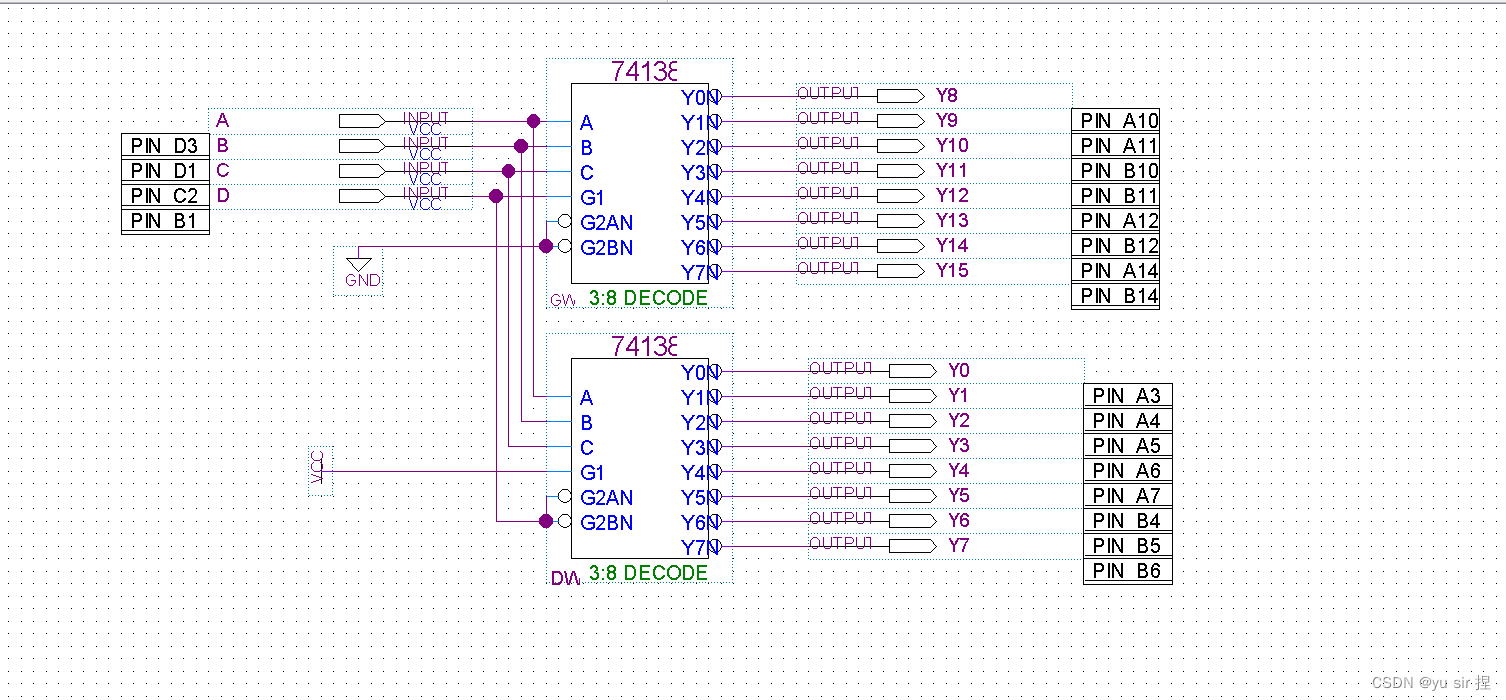

1.在图形编辑器中采用 MF 图元(74138)设计一个 4-16 译码器,以 decod***.gdf 命名保存。 将器件设定为 EP3C16F256C8。输入 D、C、B、A 绑定到 B1,C2,D1,D3 管脚,输出 Y0…Y15 按顺序绑定到 A3,A4,A5,A6,A7,B4,B5,B6,A10,A11,B10,B11,A12,B12,A14,B14 管脚。进行波形仿 真,验证功能正确。分析节点 A 到节点 y15 的最短延时。

2.在图形编辑器中设计一个 3 位的十进制加法计数器,以***cnt3.gdf 命名保存。器件设定为 EP3C16F256C8。要求能够从 0 计数到 999。从 999 归零时产生一个高电平的报警信号。进 行波形仿真,验证功能正确。分析此电路的最高计数频率。

3.在上述设计基础上增加加法计数/减法计数控制功能和置数功能,并使其计数到 119 就归 零。文件名修改为***119.gdf

链接:https://pan.baidu.com/s/1qTwgY2DjKI66gGNc_qDvmw

提取码:nm7p

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/繁依Fanyi0/article/detail/679623

推荐阅读

相关标签