热门标签

热门文章

- 1自创设计模式-----答题卡模式_element-plus, 答题卡

- 221-阴影映射_samplecmplevelzero

- 32024年【危险化学品经营单位安全管理人员】考试报名及危险化学品经营单位安全管理人员找解析

- 4原本以为汽修可以“赚大钱”,没想到转行软件测试才是我的出路···_软件测试和汽修

- 5RANSAC算法(仅供学习使用)

- 6链表(一)——无头单向非循环链表实现_无头链表 csdn

- 7【瞎搞】 ZOJ 1546 Fillword

- 8这家无人驾驶公司,竟做起了“有人驾驶”运输业务

- 9vue项目引用 iView 组件——Modal连续调用两次,第二次会出现一闪而过的问题_this.$modal.success,在onok调用 this.$modal.success,为何

- 10CJson源码解析之重要的数据结构cJSON

当前位置: article > 正文

静态时序分析—无效信号(set_case_analysis)_set case analysis

作者:繁依Fanyi0 | 2024-06-14 16:30:55

赞

踩

set case analysis

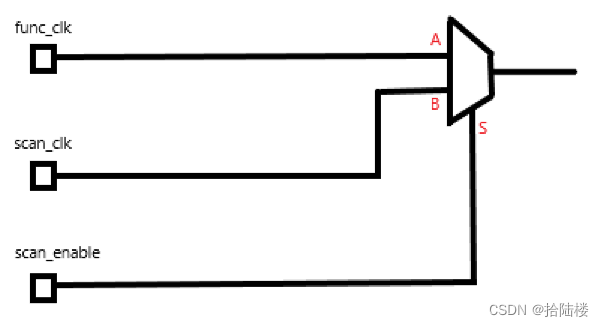

set_case_analysis常应用于多mode的设计,给一些pin/port设置常量0或1,来实现切换mode分析时序的作用。举例来说,设计中存在SCAN mode和FUNC mode,在FUNC mode下将SCAN enbale信号用set_case_analysis设置为0,在FUNC mode下就不会分析scan clock的时序。

set_case_analysis 0 [get_ports scan_enable]

一般情况下,set_case_analysis作用于MUX多路选择器的选择信号,来实现mode的选择。如图1。

- create_clock [get_ports func_clk] -name func_clk -period 10 -waveform {0 5}

- create_clock [get_ports scan_clk] -name scan_clk -period 100 -waveform {0 50}

-

- set_case_analysis 0 [get_ports scan_ena]

图1

这里容易踩坑的是,一些前端写sdc时想用set_case_analysis来切换同mode下的clock,却没有考虑到芯片工作中是否能够

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/繁依Fanyi0/article/detail/718725

推荐阅读

相关标签