- 1推荐算法岗面试题收集_推荐算法面试题

- 2一年Java开发经验,阿里巴巴五面(已offer)面经,我自己都没有想到我会过_阿里巴巴java offer

- 3【PostgreSQL】导出数据库表(或序列)的结构和数据_pgsql导出表结构

- 4云监控(华为) | 实训学习day4(10)

- 5基于python-opencv学习系列——读取图像_python opencv读取图像

- 6Kafka知识总结(消费者+重平衡)

- 7Midjourney表情包制作及变现最全教程_mid journey制作表情包

- 8100页PPT云计算运营服务体系框架、应用体系、应用场景方案_云计算运营服务体系框架、应用体系、应用场景方案ppt

- 9我还是与他分手_xiao 77

- 10按照CIS-Tomcat7最新基线标准进行中间件层面基线检测_cis安全标准 tomcat

FPGA基础--【Altera】IP核(2)---RAM随机存取存储器_fpga板上ram

赞

踩

本节文章主打Intel FPGA 开发工具Quartus中RAM IP核的调用方法

系列文章目录

【Altera】IP核(1)—PLL锁相环

【Altera】IP核(2)—RAM随机存取存储器

【Altera】IP核(3)—FIFO先进先出存储器

前言

之前已经学习了Quartus 的PLL IP核如何调用的过程。本节文章来学习RAM IP核的调用方法。

一、RAM是什么

RAM(Random Access Memory),即随机存取存储器,可以随时把数据写入任一指定的地址内的存储单元,还可以随时从任一指定地址读出数据。时钟频率决定了数据读写速度。主要用来存放程序以及程序执行过程中产生的中间数据和运算结果。

Altera 的RAM 主要分两种:单端口RAM和双端口RAM。

单端口RAM:只有一组地址线控制着写数据端口和读数据端口。

双端口RAM:由两组地址线分别控制写数据端口和读数据端口。

(1)单端口RAM

| 端口名 | 端口描述 |

|---|---|

| data | RAM读写数据 |

| address | RAM读写地址,读地址写地址共用同一个地址 |

| wren | 写使能信号,高电平有效 |

| rden | 读使能信号,高电平有效 |

| clken | 时钟使能信号 |

| aclr | 复位信号,高电平有效 |

| inclock/outclock | 单端口RAM支持双时钟模式和单时钟模式 |

(2)双端口RAM

简单双端口RAM:一组读数据和读地址线,一组写数据和写地址线,能同时进行读写操作,但是不能同时对同一地址进行读写操作。

真双端口RAM:有两组读数据线和读地址线,两组写数据线和写地址线,能够同时进行两个端口的读写,也能同时一个端口读,另一个端口写。

二、IP调用

本节文章以Quatrus为例,用文字加图片的方式展示调用RAM的方法

1.调用IP

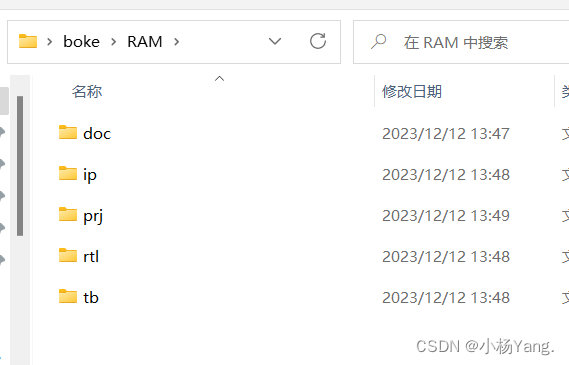

(1)创建文件

创建RAM IP测试文件夹,并且在prj中创建一个quartus的工程。(芯片类型自己选,我用的EP4CE6F17C8,芯片无所谓,本工程没用到开发板。)

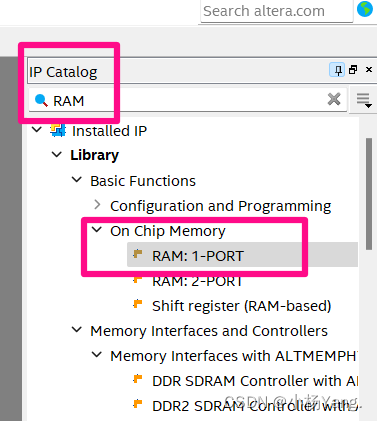

(2)调用IP

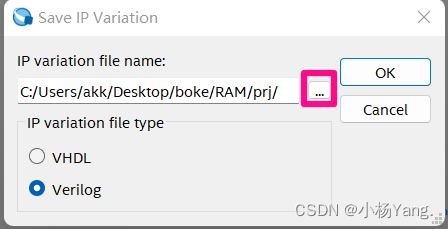

在IP Catalog 搜索栏中搜索“RAM”,然后选择“RAM:1-PORT”。

接下来的步骤就是将调用的IP文件保存到哪里,可以看上一章这一块的步骤。

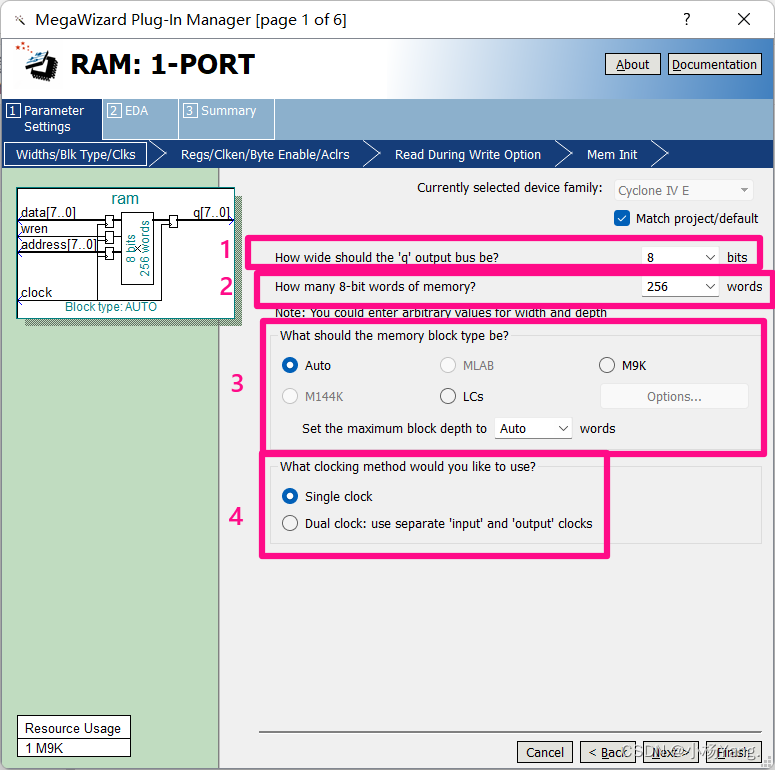

(3)配置IP

接下来就是配置参数:

1、IP核的输出数据位宽。

2、IP核的存储容量。

3、存储单元类型,默认即可。

4、选择时钟模式,单时钟或双时钟。这里选择单时钟。

然后点击“NEXT”进入下一界面。

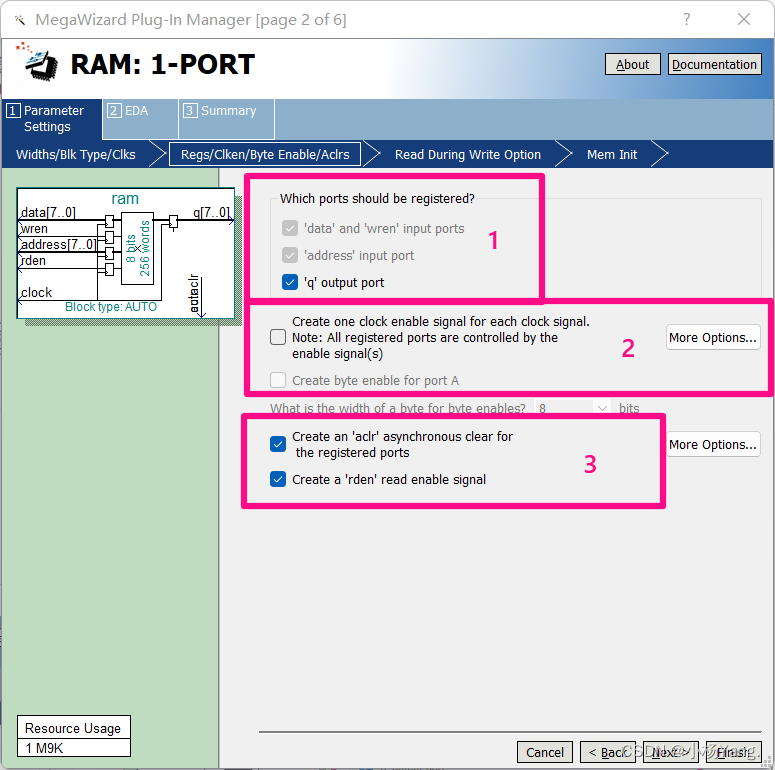

下图

1、选择输出端口q是否寄存。

2、时钟使能信号,通常默认不勾选。

3、选择是否创建已补复位信号“aclr”和读使能信号“rden”。这里都勾选。

点击“NEXT”进入下一界面。

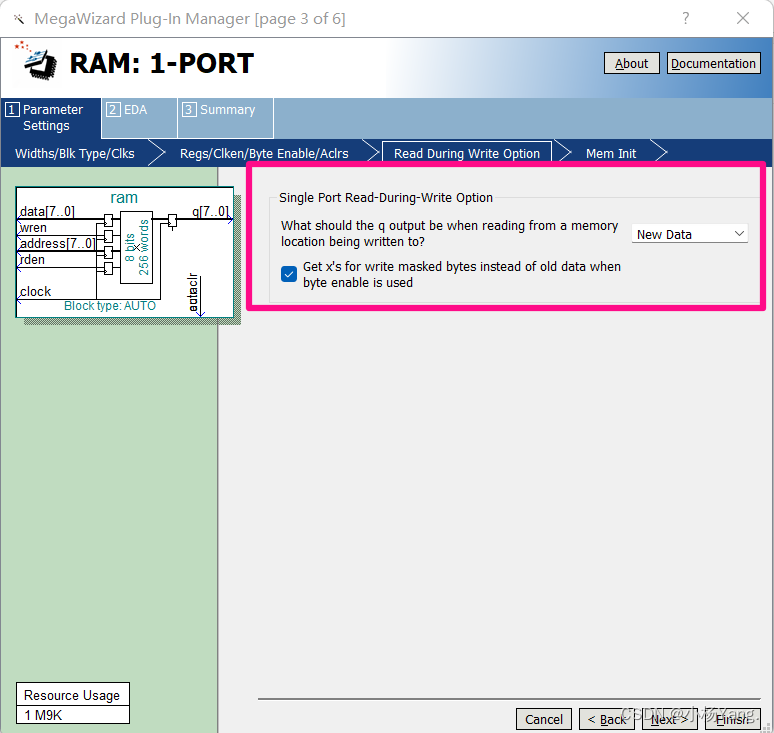

下图是配置某个地址写入数据同时读取数据的情况,通常保持默认“New data”即可。

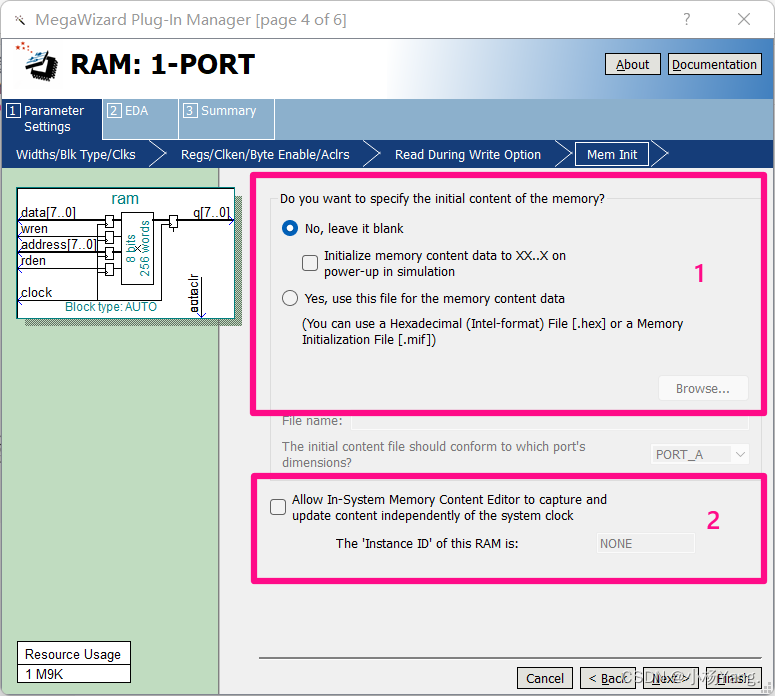

下图是配置RAM存储器初始化参数

1、是否配置初始化文件,根据需求选择,这里默认不改。

2、选择是否允许系统存储器内容编辑器采集和更新内容在与系统时钟无关的情况下,默认不勾选。

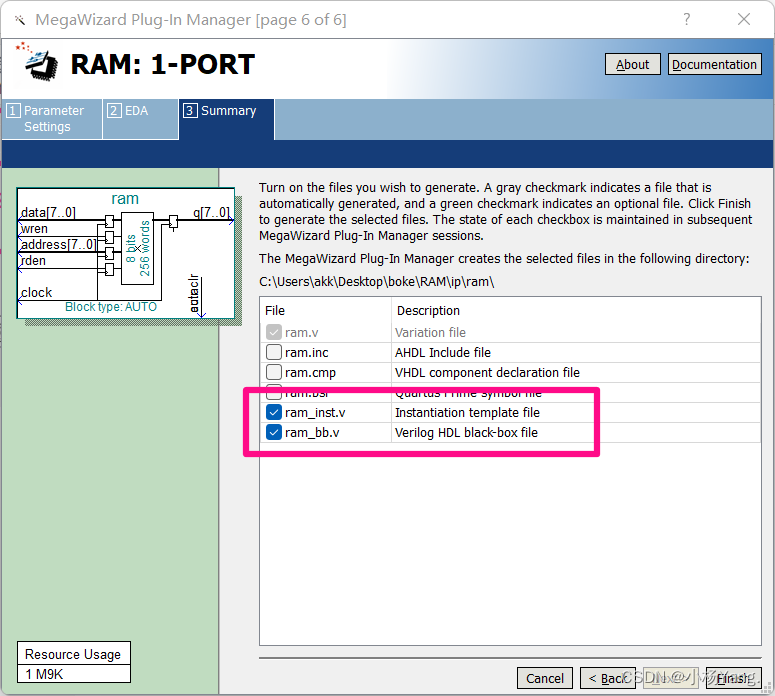

直接到下图将inst文件勾选上点击finish完成配置。

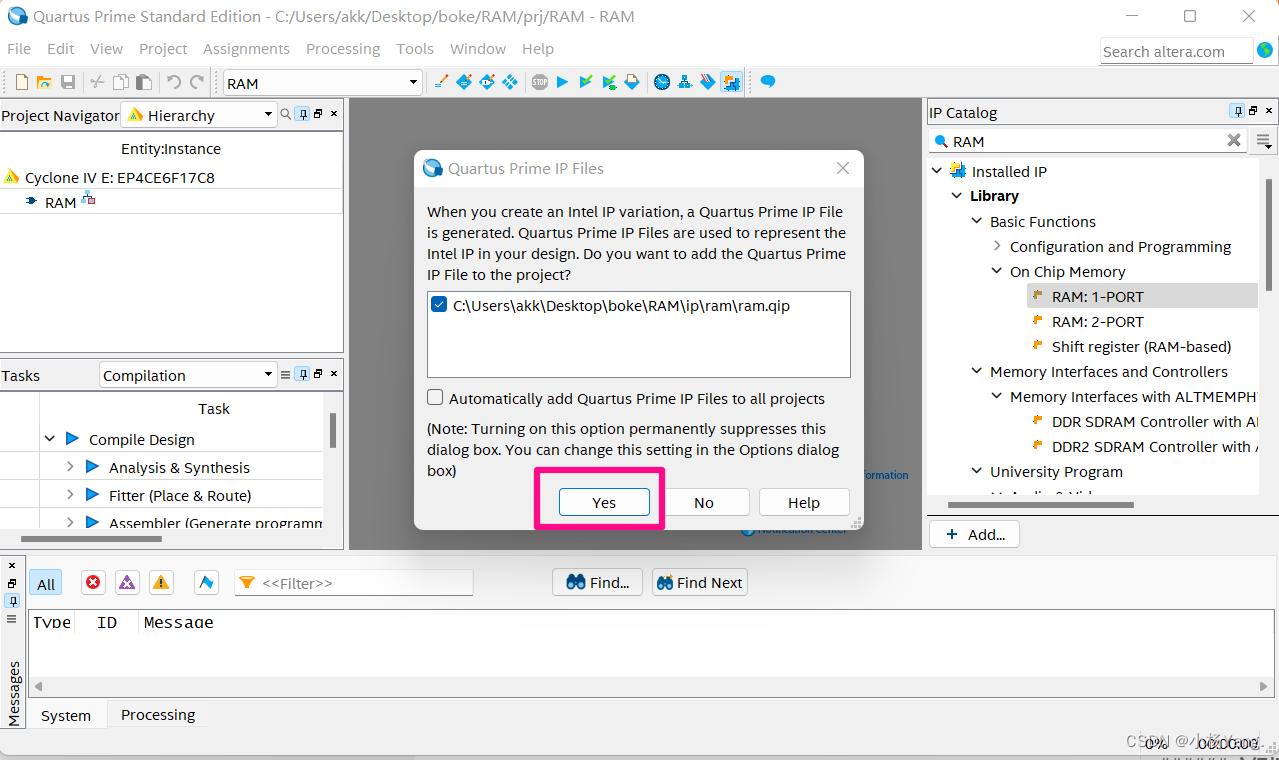

点击Yes

2.代码

IP核配置完成后就直接在文件夹中的rtl中新建“.v”文件编写代码:

将inst文件例化进代码中,然后把文件加入工程并编译:

/* * @Proj: RAM_test * @Module: test * @Author: Yang. * @Date: 2023-12-12 13:48:32 * @LastEditors: Yang. * @LastEditTime: 2023-12-12 15:11:48 */ //---------<模块及端口声名>--------------------------------------------- module ram_ip( input clk , input rst_n , input [5:0] address , input [7:0] data , input redn , input wren , output [7:0] q ); ram ram_inst ( .aclr ( ~rst_n ), .address ( address ), .clock ( clk ), .data ( data ), .rden ( rden ), .wren ( wren ), .q ( q ) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

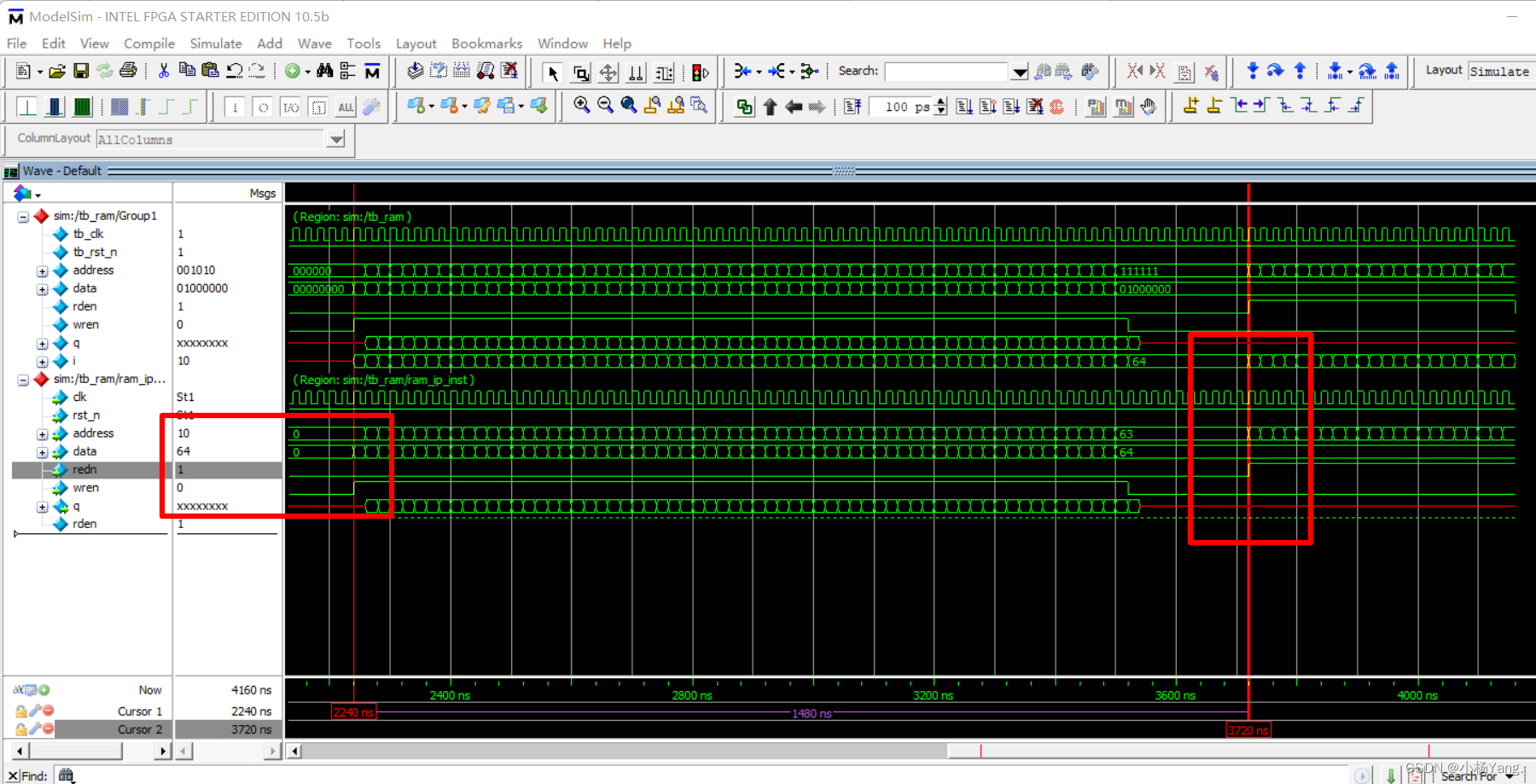

3、仿真

代码写完就要写仿真,验证IP核是否调用成功。

这个仿真的意思就是将地址依次增加,并且每加一次写进去一个数据。

之后再从头的地址读数据。

`timescale 1ns/1ns module tb_ram(); reg tb_clk ; reg tb_rst_n ; reg [5:0] address ; reg [7:0] data ; reg rden ; reg wren ; wire [7:0] q ; parameter CYCLE = 20; ram_ip ram_ip_inst( /*input */.clk ( tb_clk ) , /*input */.rst_n ( tb_rst_n ) , /*input [5:0] */.address ( address ) , /*input [7:0] */.data ( data ) , /*input */.redn ( rden ) , /*input */.wren ( wren ) , /*output [7:0] */.q ( q ) ); always #(CYCLE/2) tb_clk = ~tb_clk; integer i; initial begin tb_clk = 1'b1; tb_rst_n = 1'b1; #(CYCLE*2); tb_rst_n = 1'b0; address = 0;//复位赋初值 data = 0; rden = 0; wren = 0; #(CYCLE*10); tb_rst_n = 1'b1; #(100*CYCLE); for (i=0;i<64 ;i=i+1 ) begin //写入数据 address = i; data = i+1; wren = 1'b1; #CYCLE; end wren = 0; #(CYCLE*10); for (i=10;i<32 ;i=i+1 ) begin //读取数据 address = i; rden = 1'b1; #CYCLE; end rden = 0; $stop; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

总结

整体仿真,可以看出来“wren”先为高,表示向对应的地址中写入相应的数据。

“redn”为高时,表示从对应的地址读出相应的数据。

可以看出这个IP核调用成功。

已经学完了PLL和RAM IP核的调用,接下来就是FIFO,之后就发,继续关注。

有问题网站发私信,就是网站回复可能不及时,或者加qq:35二4291零六5 qq回复及时。

具体工程去百度网盘:

链接:https://pan.baidu.com/s/1lQqqWZXfb3i6XHwkKf52zg

提取码:yang

压缩包和具体工程都有,资源里就是一些万能代码。

加油学习吧家人们。