- 1IOS自动化测试环境搭建(Python & Java)_python ios 自动化测试

- 2大模型时代,目标检测任务会走向何方?

- 3SpringBoot-03 | SpringBoot自动配置_springboot3.0外部自动配置类

- 4312. 戳气球(区间dp)_打气球区间dp

- 5IT入门知识第七部分《移动开发》(7/10)

- 6苹果系统macOS 中安装 StableDiffusionWebUI 的终极指南_mac stable-diffusion-webui

- 7自动化测试基础——Pytest测试框架_pytest框架

- 8html 引入vue Element ui 的方式_vue 开发实战二十一:html 项目中引入 elementui 的实现

- 9Qwen2大语言模型微调、导出、部署实践

- 108254初始化编程例题

FPGA工程建立及其仿真_fpga 高速信号线仿真教程

赞

踩

初步学习FPGA,总结学习的知识,不当之处请指正。

分为3个部分,

1.工程建立及编译

2.引脚分配方法

3.quartusII自带仿真工具的使用

1.工程建立及编译

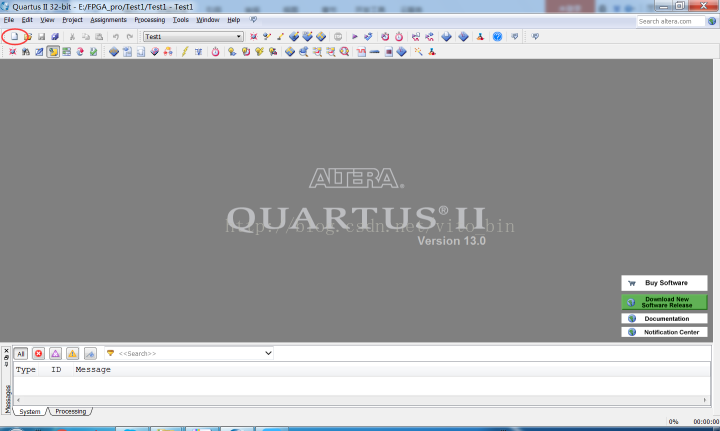

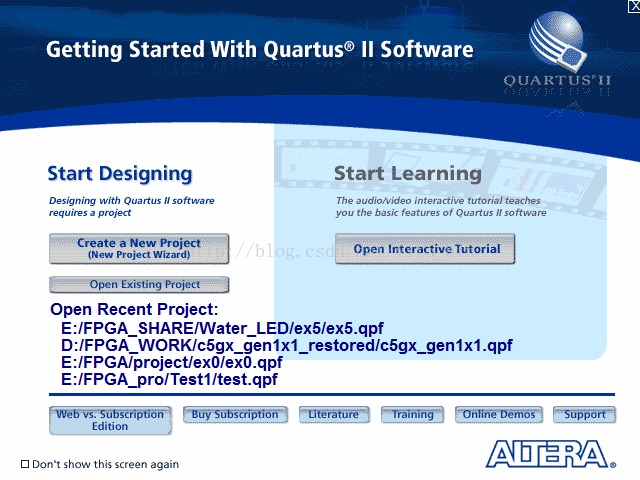

打开quartus II可以看到这样的弹窗,选择Create a new Project。(tool version:13.0 web)

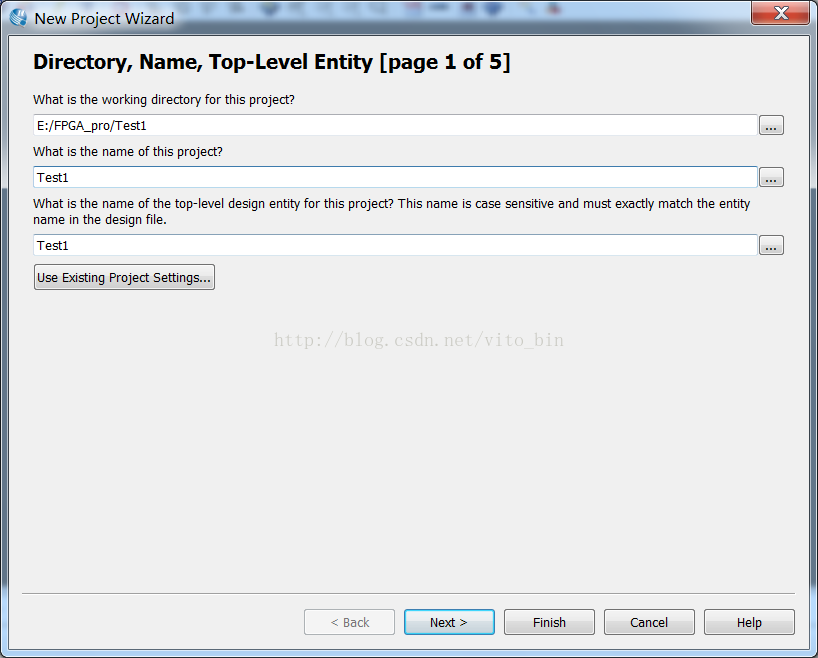

选择project存放路径(注:路径中不能含有汉子及非法字符),填写工程名。

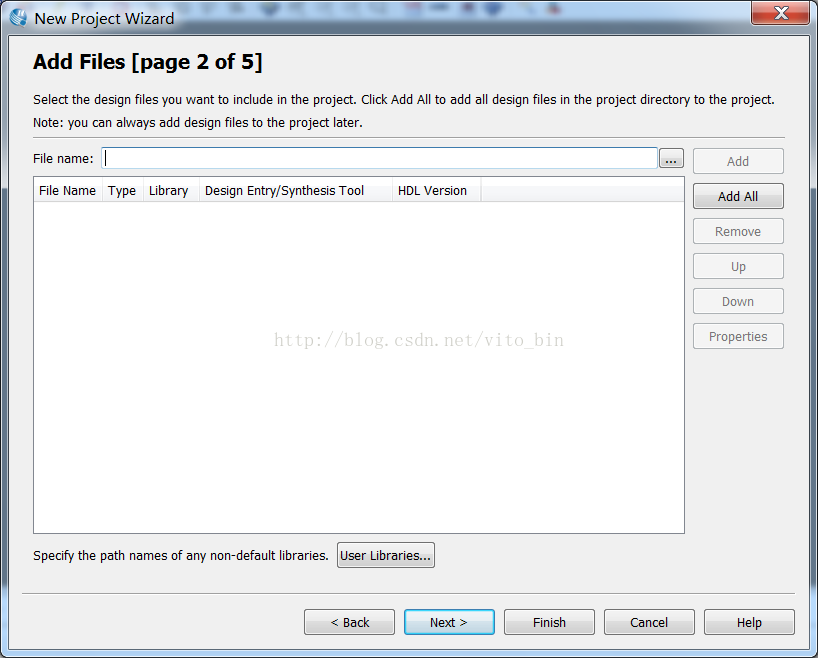

选择一个你要添加到工程的文件,如.v,也可不选,next

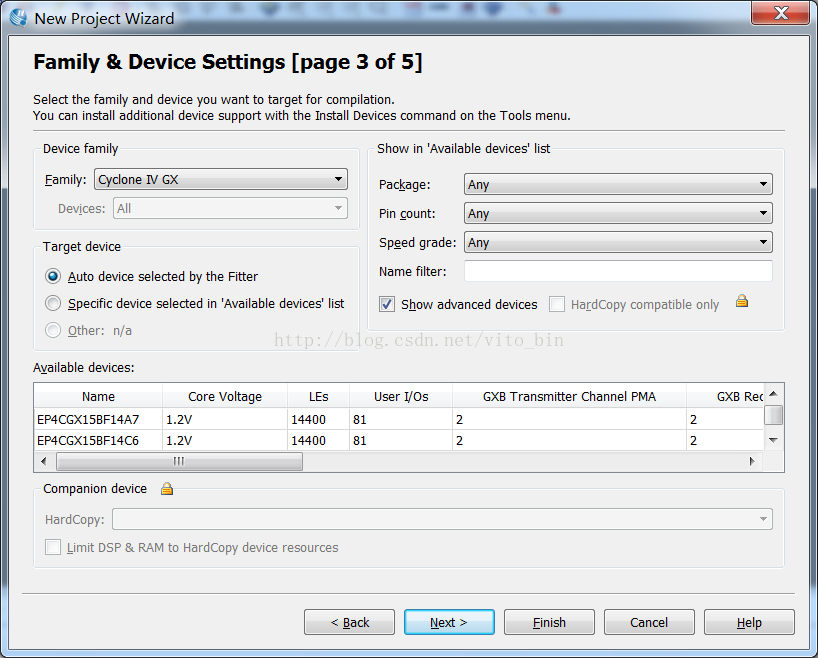

选择需要的FPGA器件,可以不选,next

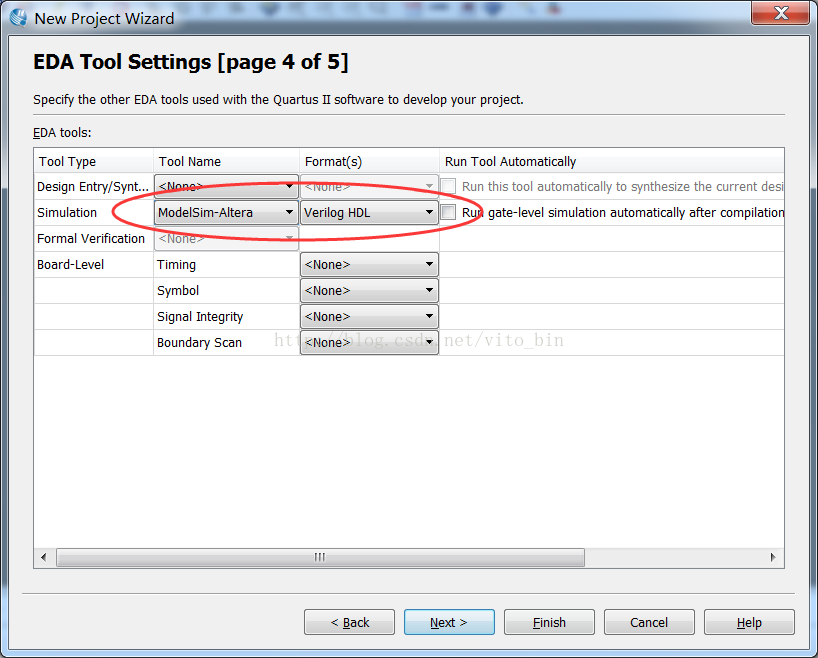

仿真工具选择Simulation-Altera,编程语言选择Verilog。Next:

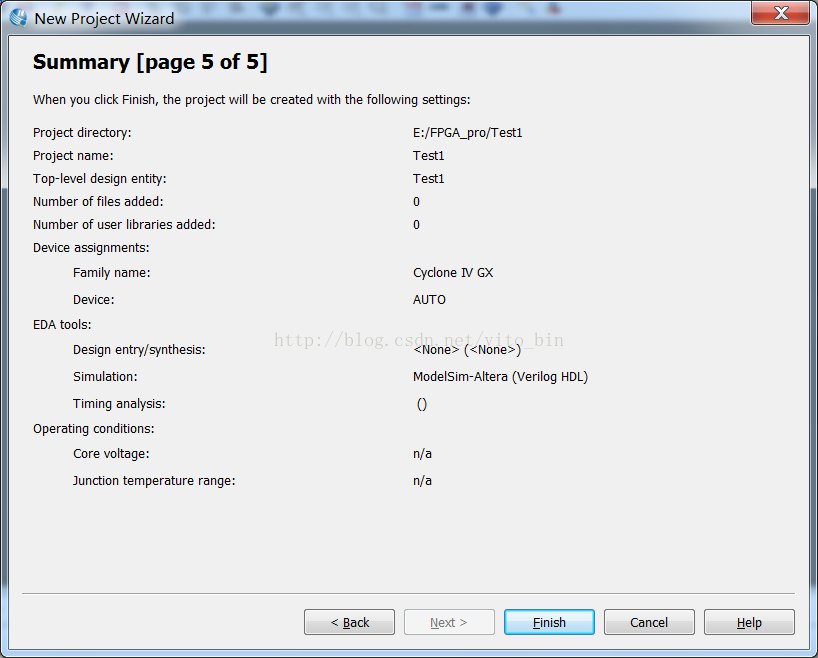

Next:show相关信息。

打开一个新的页面:

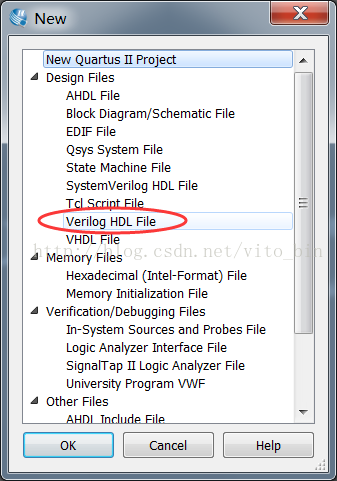

或者File中选择new,快捷键:ctrl+N

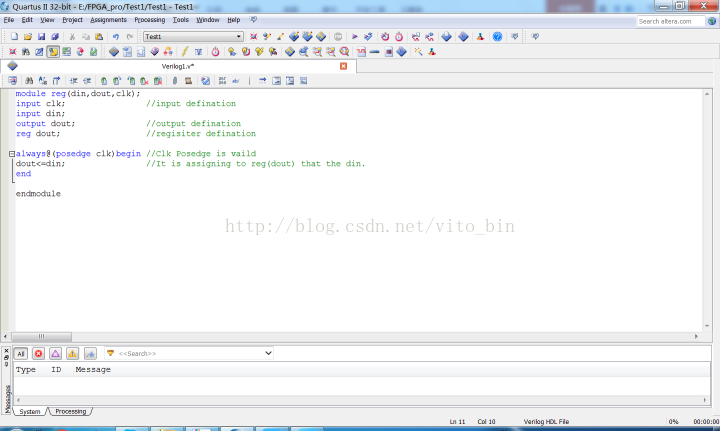

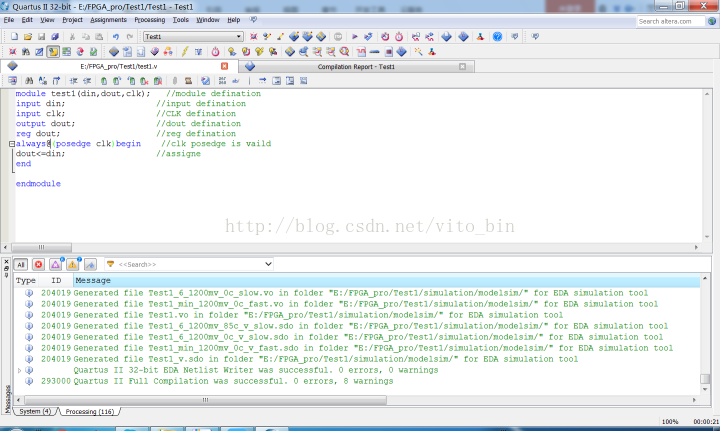

选择Verilog语言。输入程序:简单的寄存器的编写:

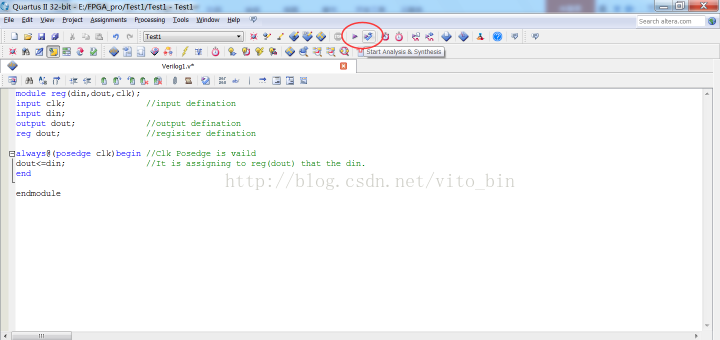

分析&&编译

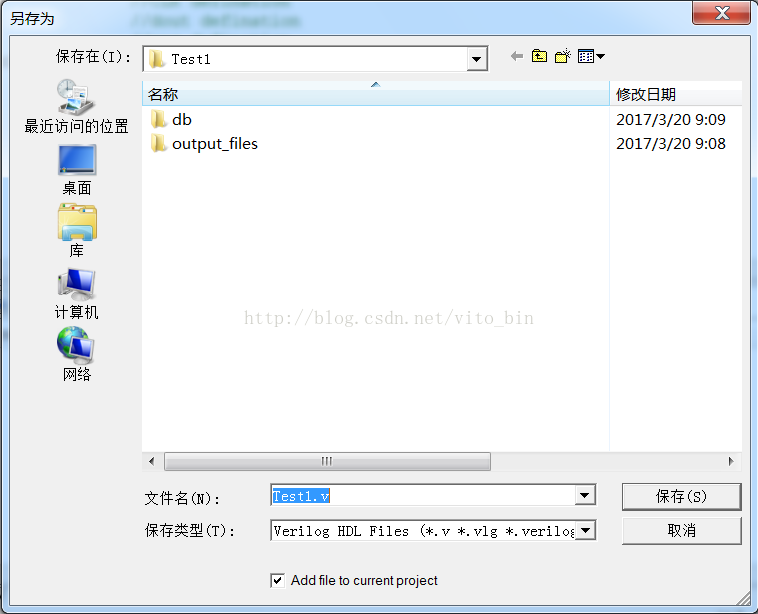

保存:文件名需要与工程名保持一致!一般默认该文件为顶层文件,如果不是,则需要设置

编译通过。

2.引脚分配方法

关于引脚分配,需要根据实际使用的以及硬件电路分配的不同功能的引脚进行适当搭配,

其中引脚分配的方式一般有四种:

1.

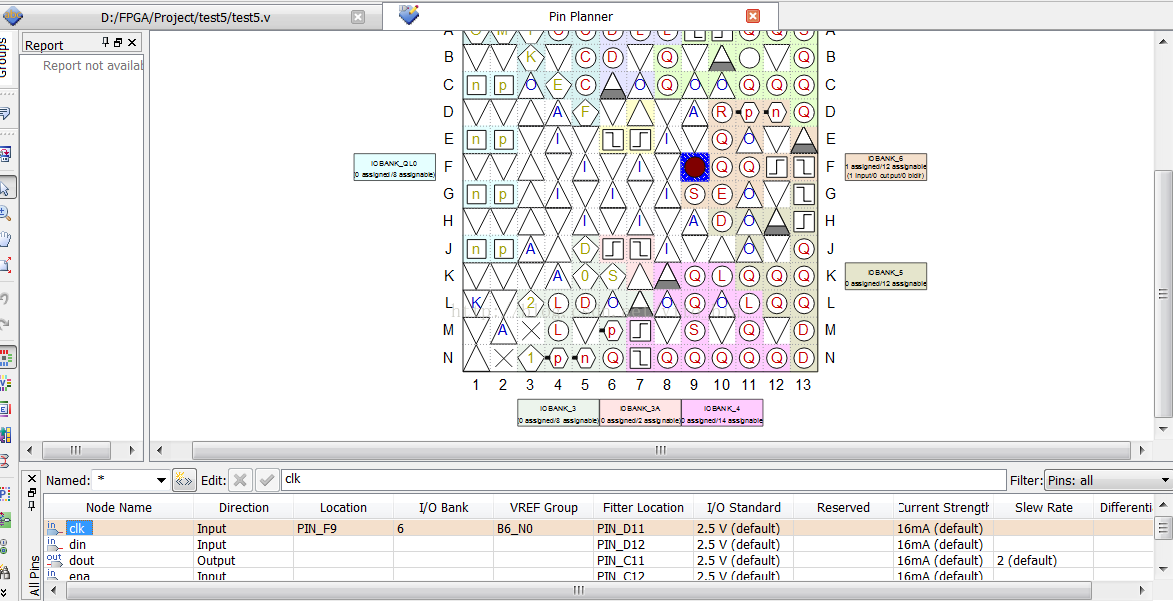

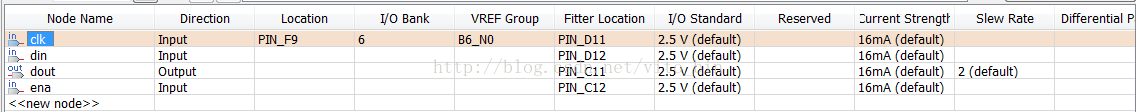

选择Pin planner

鼠标点住Node name ,直接拉到PIN planner引脚图中。

Location选项之中直接输入PIN脚

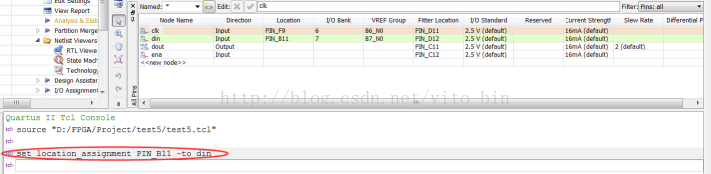

3.TCL语言

语言格式:set_location_assignment 引脚 -to 信号名

如:

在quartus中选择View->Utility Windows->Tcl Console,

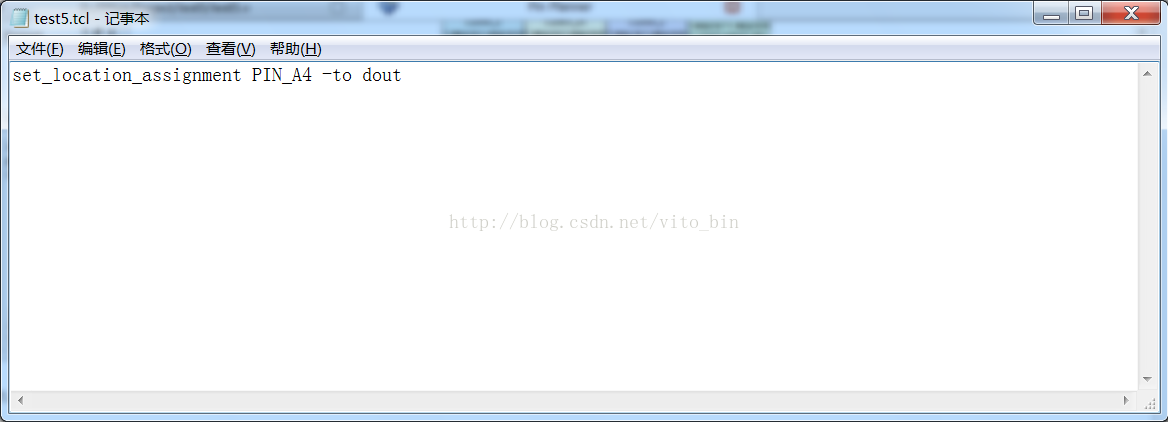

4.TCL Scripts 方式进行引脚分配

首先需要在工程文件夹目录下建立一个后缀名为tcl的文件,编辑内容:

保存,

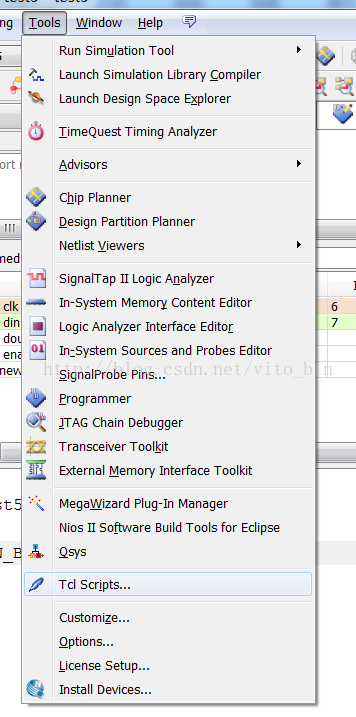

选择tool->tcl script

选择刚刚的tcl文件,run。

引脚配置成功。

3.quartusII自带仿真工具的使用

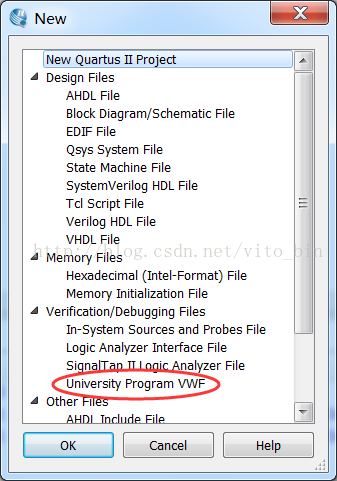

打开文件,选择new ->VMF

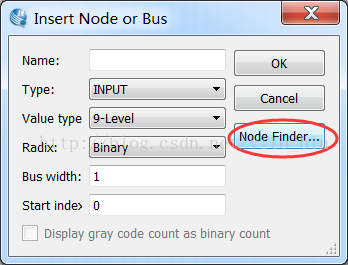

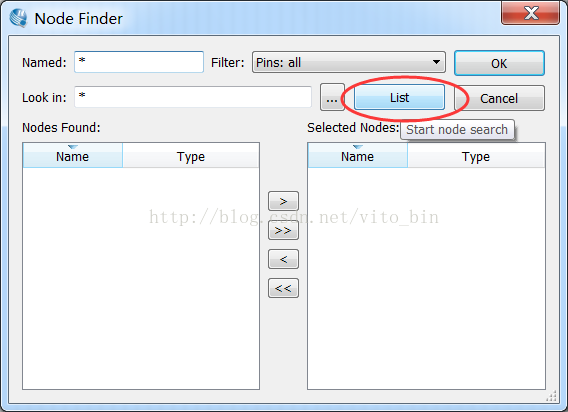

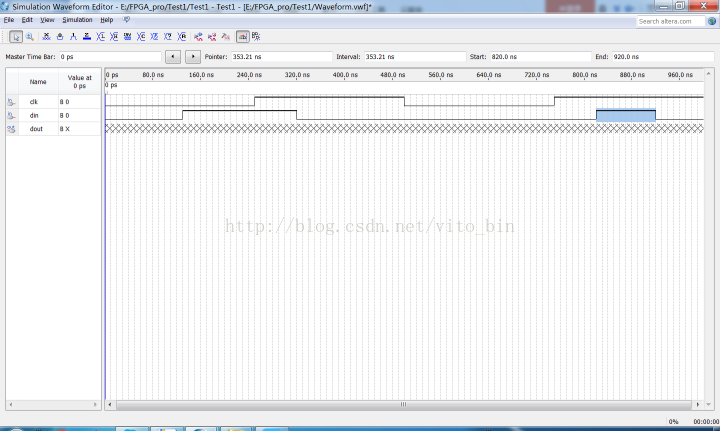

添加文件:流程如图

添加引脚:

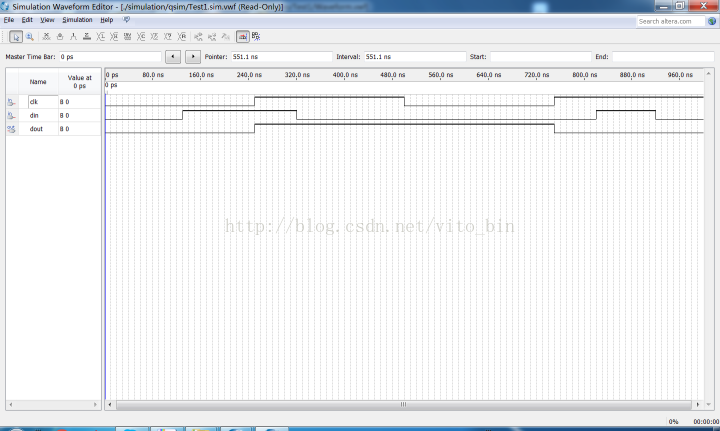

选择OK后,配置引脚信号

保存编译:

寄存器功能验证结果:clk上升沿有效,将din的值赋给dout,非上升沿时,dout保持当前状态。