- 1微信小程序之view布局

- 2YOLOv5 实例分割 用 OPenCV DNN C++ 部署_opencv yolov5 实例分割

- 3USB驱动之XHCI驱动调试总结二_xhci-hcd

- 4Android常用9种自动化测试框架对比,Appium有哪些优势?_android端自动化测试框架分析

- 5hellocharts-Android图标库

- 6[Docker]六.Docker自动部署nodejs以及golang项目_go 项目 docker 更新部署

- 7【Straw-Uniapp-uView】基于 Uniapp + uView 搭建项目基础模板_uniapp + uview模板

- 8SpringBoot多配置文件(多环境)配置(超详细)_springboot 多环境配置文件

- 9Gradle配置最佳实践

- 10Python语音基础操作--3.1语音分帧与加窗_ython语音基础操作–3.1语音分帧与加窗

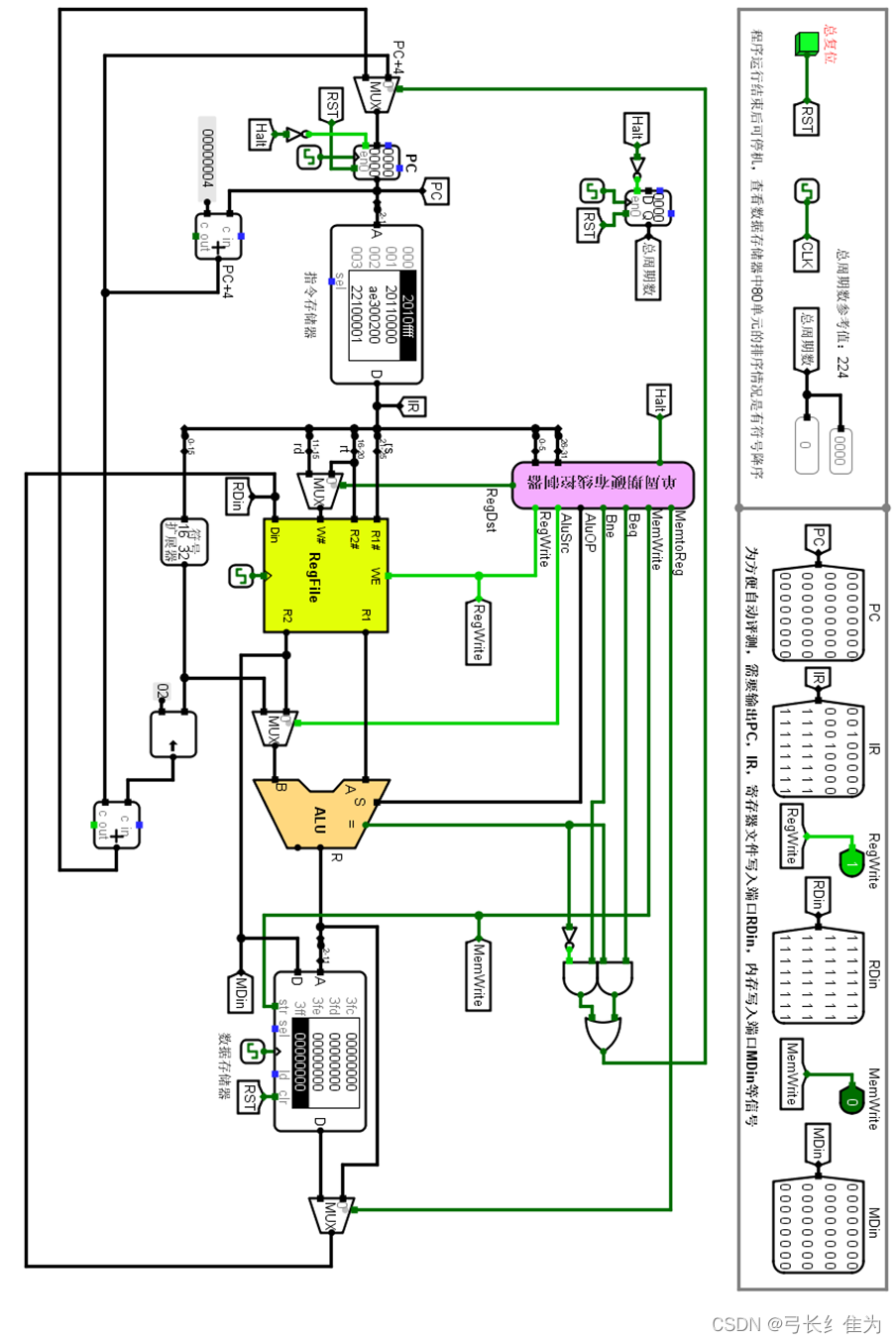

【计算机组成原理】单周期MIPS CPU的设计_单周期处理器

赞

踩

1、实验目的

掌握控制器设计的基本原理,能够利用硬布线控制器的设计原理在Logisim平台中设计实现MIPS单周期CPU。

2、主要任务

单周期处理器是指所有指令均在一个时钟周期内完成的处理器,尽管不同指令执行时间不同,但时钟周期必须设计成对所有指令都等长,根据木桶原理,单周期处理器的时钟周期取决于执行速度最慢的指令。需要说明的是,在单周期处理器中,一条指令执行中数据通路的任何资源都不能被重复使用,因此任何需要被多次使用的资源(如加法器)都需要设置多个,否则就会发生资源冲突。此外,取指令和执行指令阶段均需要使用存储器,所以单周期处理器只能采用指令存储器和数据存储器分离的结构(即哈佛结构)。本实验基于MIPS指令系统构建单周期处理器,采用迭代法实现。

- 实验过程

实验方法:迭代法

这种方法比较见简单直观,适合指令数量较少的实验。先完成支持一条固定R指令(如加法指令)的基本数据通路,测试运行通过后再在此基础上不断增加新的数据通路,支持新的指令,直至所有指令都能正常运行。要支持一条指令的运行,必须有取指令逻辑和执行指 令逻辑。

实验过程:

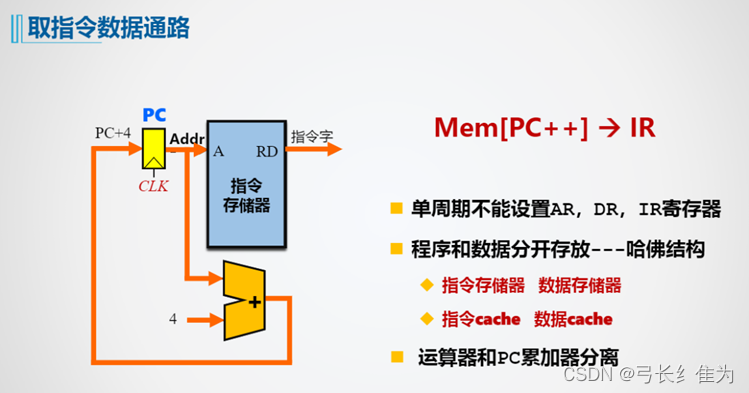

1.设计取指令数据通路

取指令部分数据通路涉及的功能部件包括程序计数器(PC),指令存储器和加法器等。取指令通路应能取出PC锁存地址对应的机器指令,并能在时钟上跳沿到来时实现PC自动加4,从而进入下一条指令的指令周期。

在顺序执行方式下,每一个时钟周期内,CPU 取出指令后将 PC 的值加 4,形成下一条指

令的地址。这里加 4 是因为 32 位 MIPS 机中所有指令字长均为 4 字节,每条指令在存储器

中占用 4个字节的存储单元,而 PC 中存放的地址是字节地址。为避免资源冲突,这里加法器是独立的器件,与CPU中的ALU分开。

指令取出后即可进入执行周期,下面就能设计支持最为简单的R型指令的数据通路,使得执行一条指令的CPU得以运行。

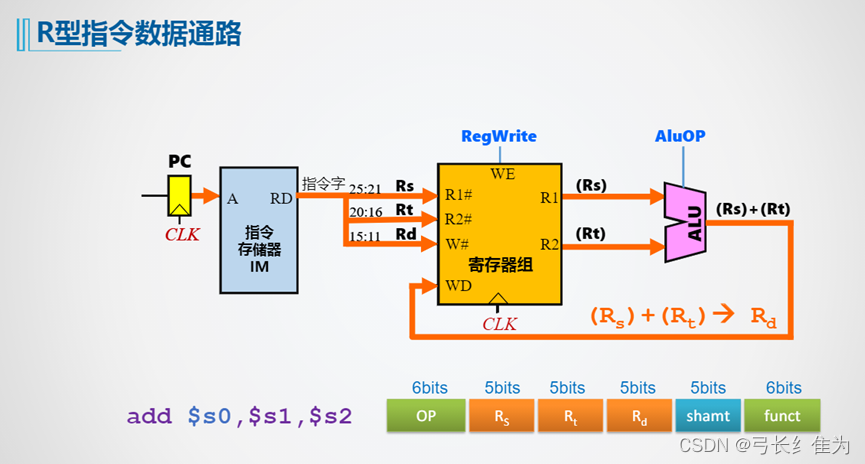

2.构建R型指令的数据通路

MIPS 中算术逻辑运算指令属于 R 型指令,执行过程中涉及的功能部件包括寄存器和 ALU。指令执行过程中 ALU 的两个源操作数均来自于寄存器文件输出,其中 R1是寄存器 R1#的值,R2是寄存器 R2#的值,R1#来自于指令字中的Rs 字段,R2#来自于指令字中的Rt 字段,运算结果写人目的寄存器Rd 中。

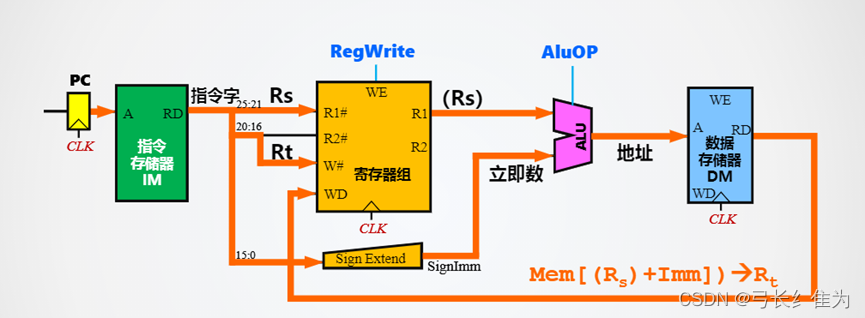

3.构建访存指令的数据通路

MIPS 访存指令属于Ⅰ型指令,访存地址等于变址寄存器Rs 的值加上 16 位立即数,地

址运算通过 ALU 完成,所以需要将Rs 的值送人 ALU,同时要将 16 位立即数进行 32 位符

号扩展(Sign Extend)后送入 ALU,二者进行加法运算得到最终的访存地址。如果是加载指令,则数据存储器的结果将会送回到寄存器文件的 WD端,写入寄存器编号为Rt。如果是存储指令,则Rt 寄存器的值会通过 R2端口输出到数据存储器的写入端口。

4、电路图及相关说明

·将不同类型指令的数据通路进行综合,得到单周期MIPS总的数据通路。

·控制器的输入来自操作码的Op和Func,根据Op可以判断是R型指令还是其它类型指令,根据Func可以知道指令的具体功能。

·使用哈佛结构,指令存储器和数据存储器分离。

·使用了多路选择器MUX,有多个输入源时做出选择。

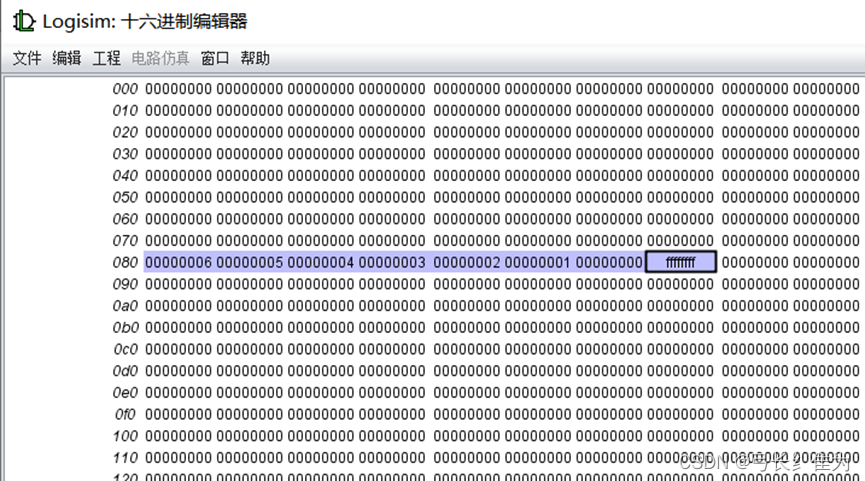

5、实验数据测试与截图