- 1聊一聊nacos是如何进行服务注册的_nacos的服务注册流程

- 2【信管9.3】项目干系人管理

- 3HDC2022丨中软国际发力智联网自主创新,数智赋能千行百业_中软国际2022年研发人员有多少

- 4图神经网络入门_标签输入图网络

- 5李宏毅老师《机器学习》课程笔记-6 GAN_unsupervised learning:generation

- 6华为emul升级_EMUI11正式版下载_华为emui11下载最新完整包2020(附升级教程及支持型号)-刷机之家...

- 7ABAP日期时间函数(转载)_abap 日期加天数

- 8Java的加减乘除工具类,实现精确的加减乘除运算_定义一个钱工具类, * 里面存在一个字段提供加减乘除方法(除法三个方法参数,其它两

- 9Servlet_servlet接口中定义了4个抽象方法

- 10Windows远程登陆Linux桌面的方法

亚稳态及其解决办法

赞

踩

亚稳态

在数字电路中,每一位数据不是1(高电平)就是0(低电平)。当然对于具体的电路来说,并非1(高电平)就是1V,0(低电平)就是0V,对于不同的器件它们都有不同的对应区间。比方说对于某个器件来说,2.25 ~ 2.5V可以识别出来是高电平,0 ~ 0.25V可以识别出来是低电平,但是如果信号的电压处于0.25 ~ 2.25V之间,器件也就无法识别是高电平还是低电平(最终的结果可能是高电平也可能是低电平,无法预测),这种状态也就是亚稳态。

亚稳态的产生原因

寄存器有一种特性,在clk的有效边沿时,采样数据D,输出到Q,此过程如果想要稳定进行,那么要求,数据D在clk有效边沿之前一段时间保持稳定(建立时间),在clk有效边沿之后一段时间保持稳定(保持时间),如果任何一个不满足,就会导致此过程失败,结果就是clk的有效边沿过去后,Q的值可能就不会出现预想值

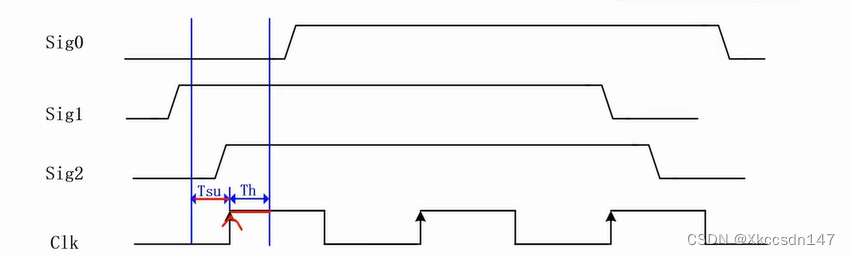

Tsu(setup建立时间)在上升沿到来之前数据保持稳定不变的时间,Th(holdup保持时间)在上升沿来带之后数据保持稳定不变的时间

对于Sig0和Sig1在两段时间内数据都是保持不变的,所以采样不会出错,但是对于Sig2在Tsu和Th内处于不确定的状态,如果sig2在这个上升沿被采样,那么在得到的数据是不稳定(Tmet)的,并且这种状态会向后传递,灰常的危险。

什么是同步异步信号

同步电路中的信号,我们称之为同步信号。

如果在设计中,寄存器的时钟端连接在不同的时钟上,那么称之为异步电路设计。

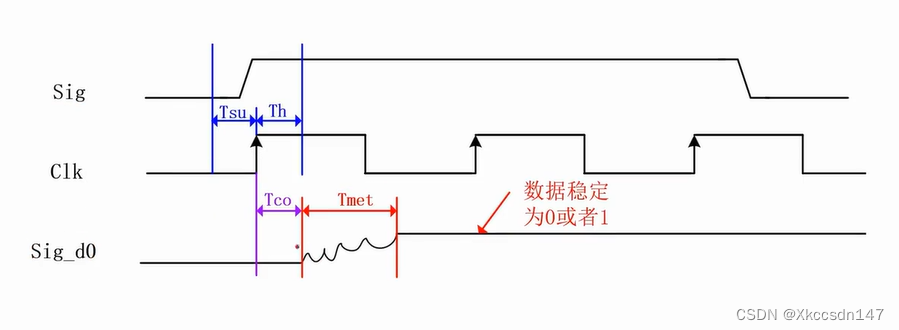

在真实的电路中,各部分元器件都是有延迟的。对于同步电路来说,Q的更新都是在clk上上升沿之后的一段时间(Tco:输出延迟),输出的数据经过组合逻辑或者线路也会有延迟(delay:线路延迟),到达下一个寄存器。此时,信号早就偏离了clk的上升沿。所以对于下级寄存器来说,这个信号也是“异步信号”。所以说真实电路中,全部的信号都是“异步信号”。

那么为什么在同步电路中,我们都称为同步信号呢?

因为在电路中,所有的延迟都是已知的(TCO、delay等等),我们可以通过扩大clk的周期,确保clk的周期大于TCO等等之类延迟之和,那么就可以保证下级寄存器采样到数据。所以这种电路中的信号,我们依然把他称之为同步信号。

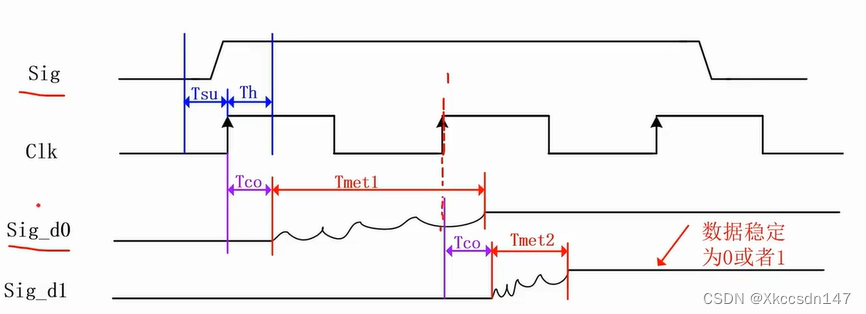

在跨时钟域时,由于两个时钟之间没有任何关系,无论怎么调整周期,都不一定能满足下级寄存器采样到数据,肯定不能调成一致周期,那就变成了同步设计。例:用寄存器采样外部按键的输入,那么此时外部按键的信号对于寄存器来说就是异步信号,因为外部信号是随时都有可能有效,所以无论怎么调整,都不一定能够保证信号满足寄存器的建立保持时间。

那么既然在很多情况下,无论如何也避免不了异步信号带的坏处,那么能不能全部采用同步设计?显然是不太现实,不同接口或者存储器等都有自己频率,全部采用同步电路设计的方式将失去很多功能。例如:千兆以太网的GMII接口,采用125M接口,1080P的HDMI接口采用148.5MHz的接口。

既然无法避免,那就勇敢面对。

怎么消除亚稳态

拍数打得越多越稳定,一般采电平只需要打两拍,如果要采沿变(上升或者下降沿)就需要打三拍

(再多级的寄存器,也无法避免亚稳态,只是级数越多,最后一级输出亚稳态的几率将会越低。)

FPGA零基础学习:在FPGA中,同步信号、异步信号和亚稳态的理解