- 1【机器学习】决策树特征选择准则 信息增益、信息增益率、基尼系数的计算及其python实现_机器学习增益率计算题

- 2Git 中强行拉取,覆盖本地修改_git强制将远程覆盖到本地

- 3图像处理ASIC设计方法 笔记18 轮廓跟踪算法的硬件加速方案

- 4【深入浅出Spring原理及实战】「Web请求读取系列」如何构建一个可重复读取的Request的流机制_javaweb 请求流重复读取

- 5面向中文大模型价值观的评估与对齐研究:给AI的100瓶毒药

- 6uni.app开发小程序如何获取当前经纬度、位置信息以及如何重新发起授权定位_uniapp获取当前经纬度

- 7VHDL仿真ModelSim使用简介_modelsim vhdl

- 8mvc控制器html返回json,asp.net-mvc – 如何从MVC控制器返回Json对象到视图

- 9Meta 新推出的实时语音翻译模型 Seamless_seamless expressive

- 10华纳云:ubuntu中fdisk找不到硬盘怎么解决?

10GUDP协议栈 MAC层设计-(1)10G Ethernet PCS/PMA_10g eth mac层设计

赞

踩

一、引言

对于10G以太网MAC层的实现,Xilinx提供了 3种IP核,分别是 10G Ethernet MAC、10G Ethernet PCS/PMA、10G Ethernet Subsystem。

- 10G Ethernet MAC只包含MAC层,外部需要提供一个PHY芯片进行数据对齐,10G Ethernet MAC与PHY之间的接口为XGMII。

- 10G Ethernet PCS/PMA只包含PHY层,需要用户实现MAC层的功能,两者之间的接口同样也为XGMII

- 10G Ethernet Subsystem包含完整的MAC层和PHY层,用户只需要将数据送入IP核即可。只不过这个IP核是收费的。

本篇简要介绍10G Ethernet PCS/PMA IP核的使用,以及XGMII接口的主要时序。

二、10G Ethernet PCS/PMA IP核

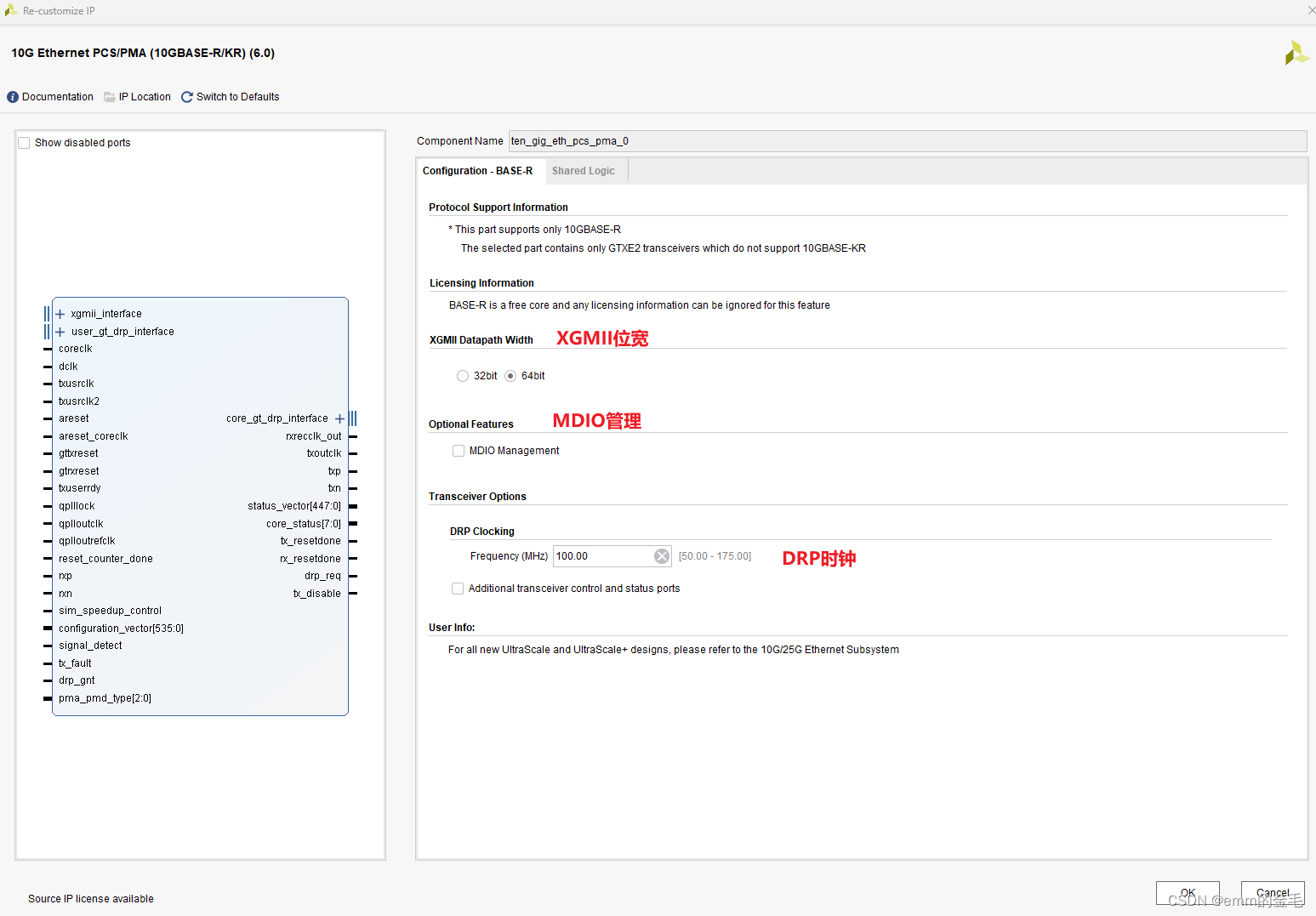

(1)选择XGMII的位宽为64bit,DRP的时钟为100M.

(2)将共享逻辑饱汉子例子工程中

三、XGMII接口时序

三、XGMII接口时序

参考:PG068

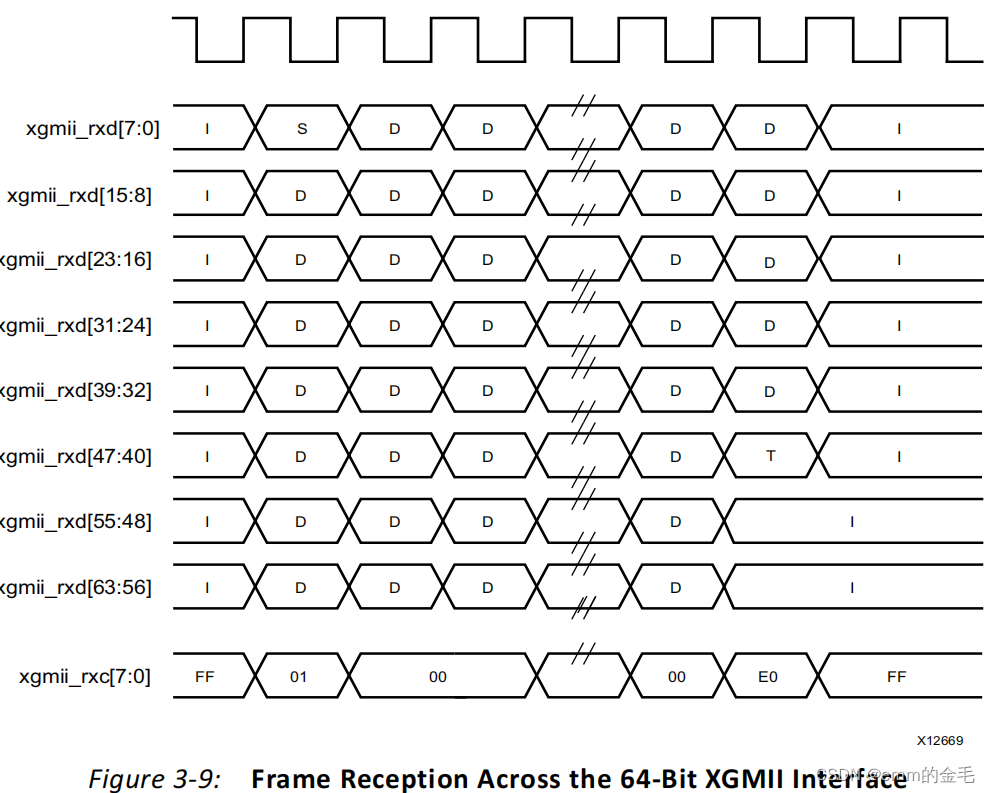

64bitXGMII接口(单侧:发送侧或者接收侧)

7系列需要提供156025MHz的时钟

64bit数据位宽的XGMII接口包含Data Bus、Control Bus,其中控制字符包含4种,分别是空闲字符(Idle)、起始字符(Start)、结束字符(Terminate)、错误字符(Error)。具体数值如下

起始字符(Start)的位置共有两种方式,一种是在数据总线的第4个字节(小端模式),一种是在数据总线的最后一个字节(小端模式)。这两种方式的选定主要是和64b/66b编码有关,具体可以去了解一下64b\66b编码。

起始字符在第4个字节:

起始字符在第一个字节:

32bit XGMII接口 (单侧:发送测或者接收侧)

7系列需要提供312.5MHz的时钟

对于32bit 的XGMII接口,起始字符的位置只有一种,就是在最后一个字节(小端模式)。

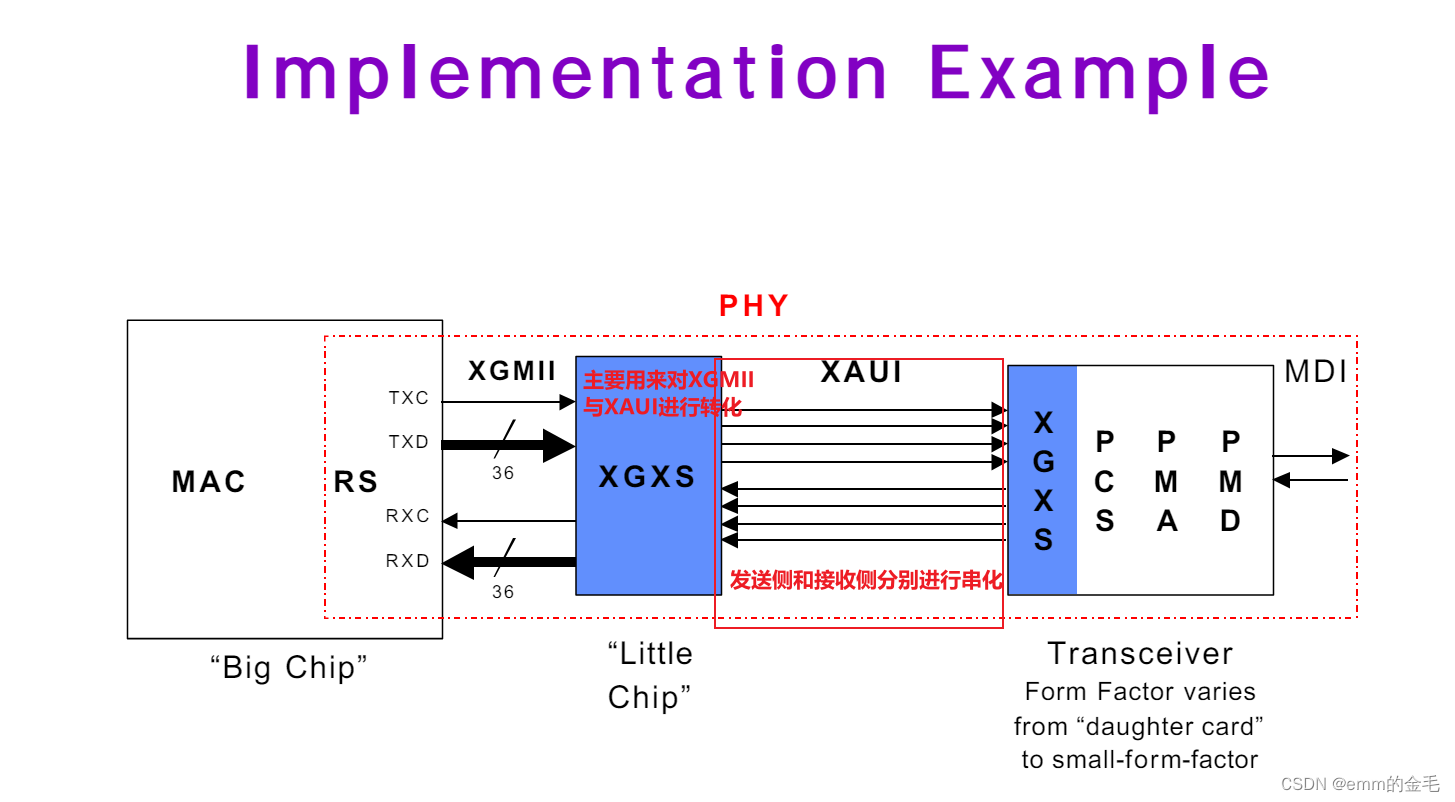

64bitXGMII接口与32bitXGMII接口应用场景

64bit XGMII接口一般用于FPGA逻辑内部,也就是使用FPGA GT资源实现PHY层,PHY和MAC层都在FPGA内部实现。(主要原因接收侧+发送侧的信号数量达到了146,如果采用外部PHY芯片,即便转换成XAUI接口,走线还是太多了)

32bit XGMII接口可以用于外部连接PHY芯片,不过需要转换为XAUI接口,XAUI接口就是对XGMII按照lane进行串化,以减少PCB走线的数量,减小信号衰减和信号间的串扰。

- [7:0] -> 1 Lane

- [15:8] -> 2 Lane

- [23:16] -> 3 Lane

- [31:24] -> 4 Lane

总结:

引用:https://grouper.ieee.org/groups/802/3/ae/public/blue_book.pdf