- 1最大子序和、最长递增子序列的个数_递增子序列最大和

- 2navicate破解失败后删除注册表_navicat注册表误删

- 3ButterKnife10.0.0环境搭建和插件使用_butterknife 10

- 4FloodFill算法---DFS

- 5ArcGIS Engine commands_create steepest path, create line of sight

- 6深度学习框架_深度学习框架是什么意思

- 7第十三届蓝桥杯Python B组国赛题解_pythonb组蓝桥杯小蓝做实验代码思路

- 8selenium之document.querySelector()方法

- 9matlab求动力学模型,MATLAB/Simulink动力学系统建模与仿真

- 10数据结构课程设计——平衡二叉树(有菜单页面,最详细操作)-C_关于二叉树的代码有菜单的

基于FPGA的iic主从机驱动实现Verilog实现iic slave和iic master

赞

踩

基于FPGA的iic主从机驱动实现

Verilog实现iic slave和iic master

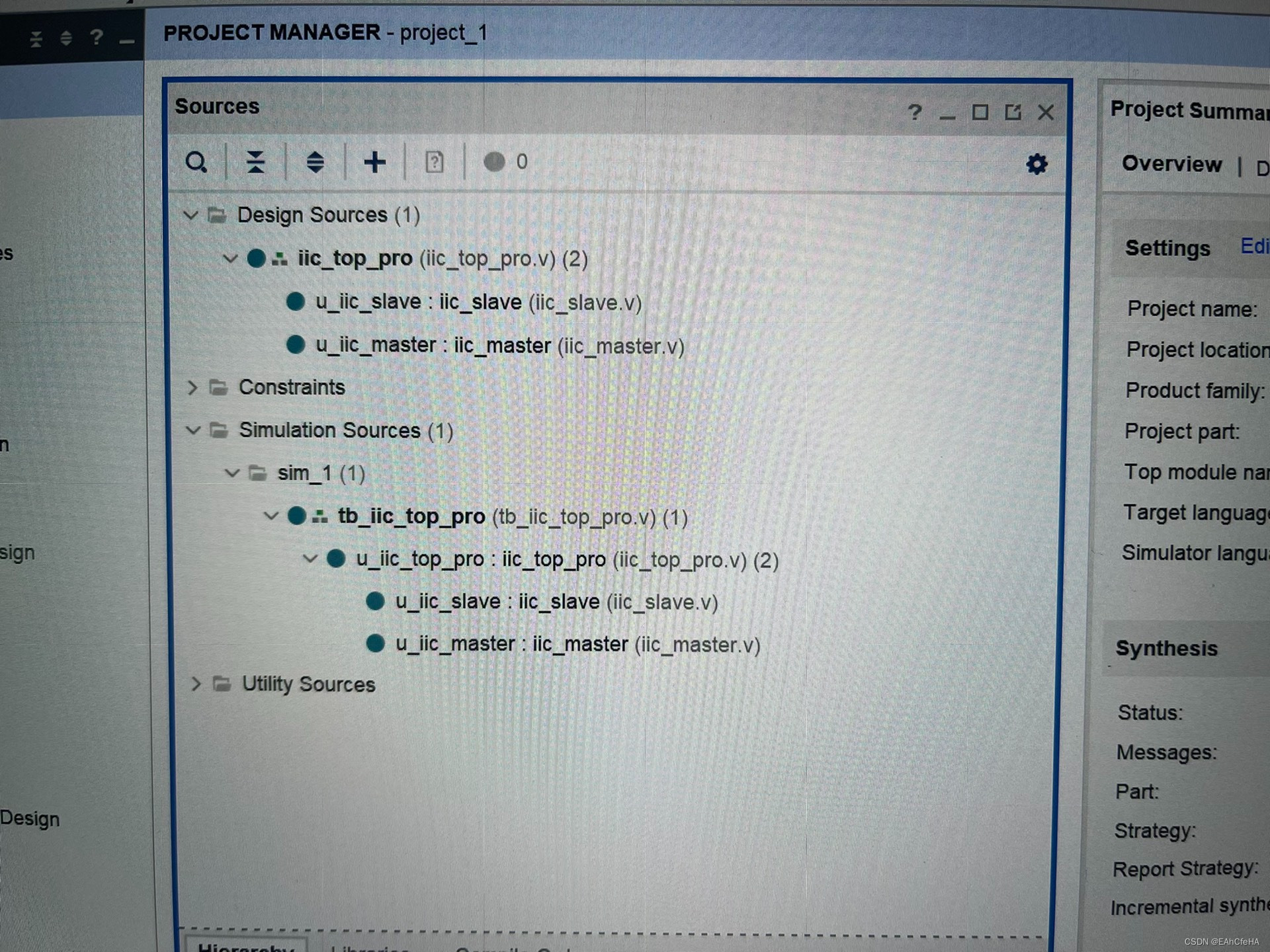

顶层模块实现master对slave自定义的寄存器读取

带仿真模块

基于FPGA的iic主从机驱动实现

随着物联网、智能家居等应用的普及,各种传感器设备、智能终端等设备不断涌现。而这些设备通常需要进行互联互通,需要采用各种不同的通讯协议。其中,iic通讯协议是应用非常广泛的一种协议,它具有低功耗、低成本、可靠性高等优点,因此也成为了众多设备通讯的首选协议之一。

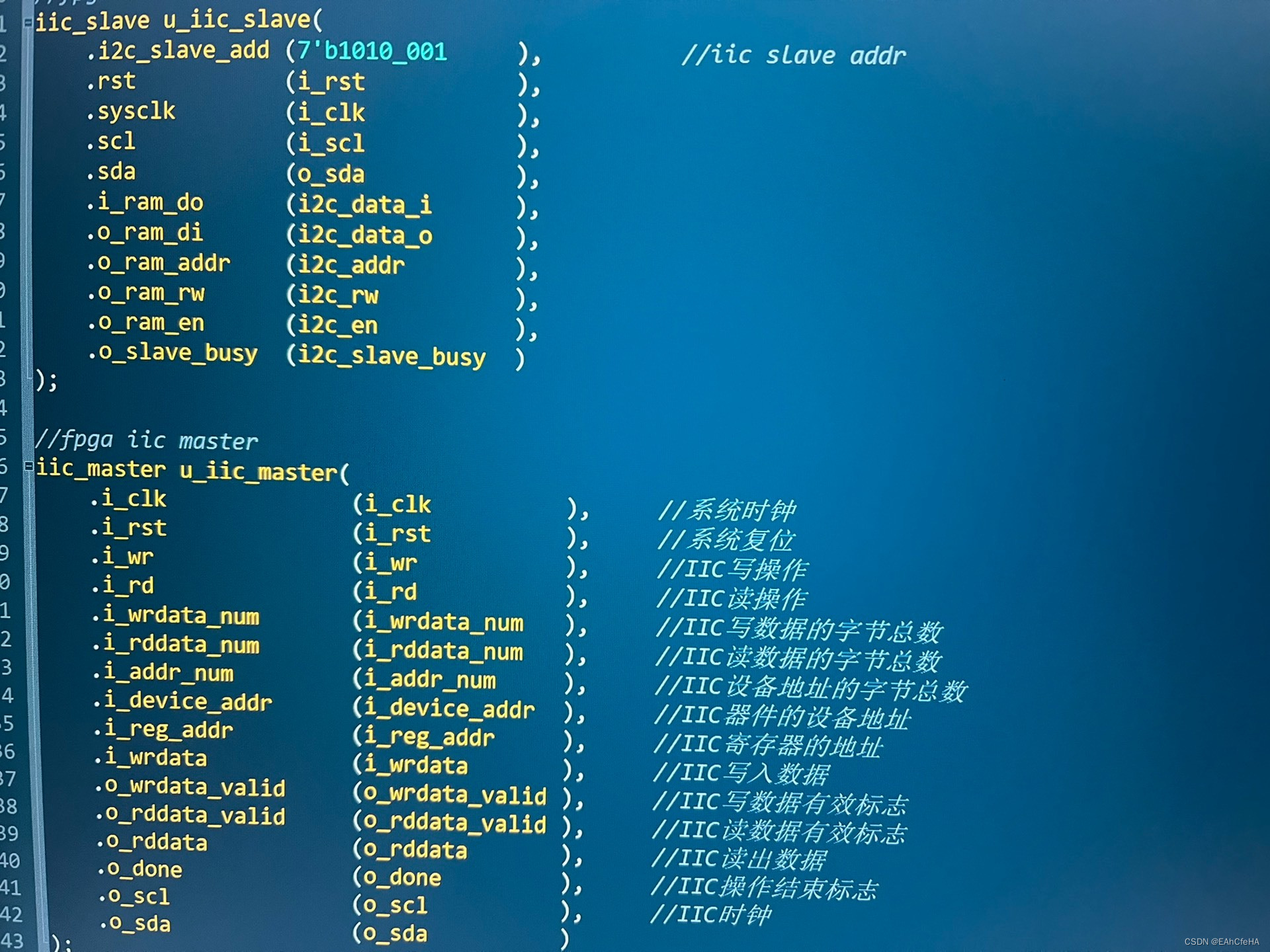

本文主要介绍基于FPGA实现的iic主从机驱动,包括iic slave和iic master的Verilog实现,以及实现master对slave自定义的寄存器读取,并提供带仿真模块的完整实现方案。

- iic slave实现

iic slave实现的主要目的是在iic总线上接收来自iic master的控制信息,并响应相应的操作。我们可以将iic slave的实现分为以下几个步骤:

1.1 时钟信号的产生

iic通讯协议采用双向数据线SCL和SDA进行通讯,在通讯过程中需要有一个时钟信号,由于FPGA本身没有时钟信号,我们需要自行生成时钟信号,通过计数器控制时钟占空比,从而产生时钟信号。计数器的位宽由波特率决定,因此可以通过调整计数器的位宽来控制时钟频率。

1.2 状态机的实现

iic通讯协议的实现需要借助状态机来进行控制。具体来说,iic通讯协议包含以下几种状态:

- Idle:空闲状态,等待iic master发起通讯。

- Address:地址状态,判断iic master是否发送了正确的从设备地址。

- Data:数据状态,接收iic master发送的数据。

- Ack:应答状态,对iic master发送的数据进行应答。

实现状态机需要使用Verilog实现有限状态机(FSM),每种状态下需要实现相应的控制逻辑。

1.3 数据的接收与解析

在Data状态下,iic slave需要接收来自iic master的数据,并进行解析和存储。具体来说,需要实现以下几个模块:

- 数据接收模块:接收iic master发送的数据。

- 数据解析模块:根据iic通讯协议的规定,解析iic master发送的数据。

- 数据存储模块:将解析后的数据存储到相应的寄存器中。

- iic master实现

iic master实现的主要目的是控制iic slave进行数据读写操作。我们可以将iic master实现分为以下几个步骤:

2.1 时钟信号的产生

与iic slave实现类似,iic master的实现也需要产生时钟信号。不同之处在于,iic master需要根据iic通讯协议的规定在时钟线上发送时钟信号,因此需要对时钟信号进行控制。

2.2 状态机的实现

iic master的实现同样需要使用状态机进行控制。具体来说,iic通讯协议包含以下几种状态:

- Idle:空闲状态,等待iic master发起通讯。

- Start:起始状态,发送起始信号。

- Address:地址状态,发送设备地址。

- Data:数据状态,发送数据。

- Ack:应答状态,接收从设备的应答信号。

- Stop:停止状态,发送停止信号。

实现状态机需要使用Verilog实现有限状态机(FSM),每种状态下需要实现相应的控制逻辑。

2.3 数据读取

iic master需要对iic slave设备进行读取操作,具体来说,需要实现以下几个模块:

- 数据读取模块:向iic slave设备发送读取指令并接收返回数据。

- 数据解析模块:根据iic通讯协议的规定,解析iic slave设备返回的数据。

- 数据存储模块:将解析后的数据存储到相应的寄存器中。

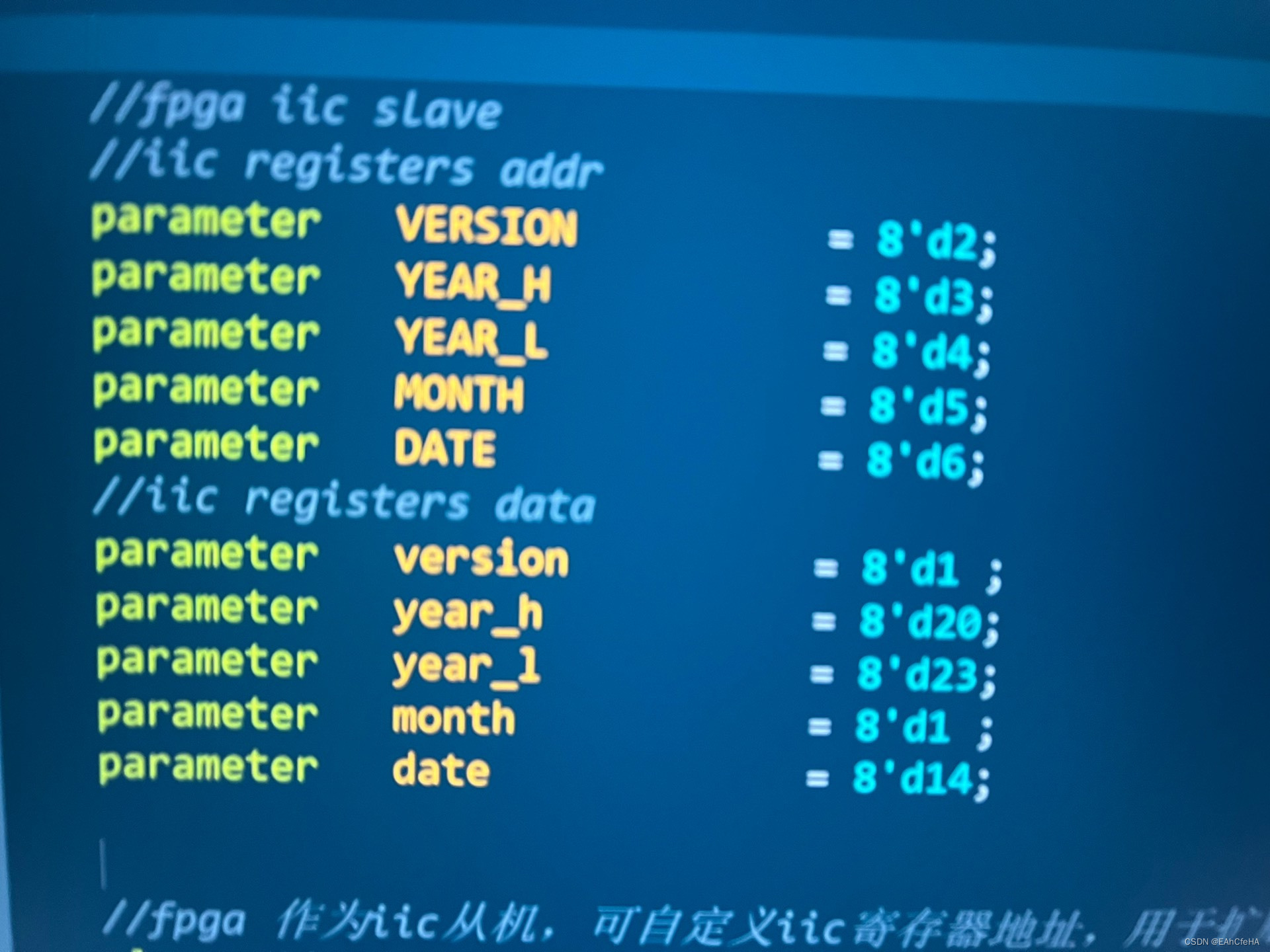

- 顶层模块实现

为了实现master对slave自定义的寄存器读取,我们需要在iic slave的设计中添加一些自定义的寄存器,并在顶层模块中实现对这些寄存器的读取。

具体来说,我们需要在iic slave的设计中添加一个寄存器模块,它包含以下内容:

- 自定义寄存器的定义:定义需要添加的自定义寄存器。

- 寄存器读取模块:实现读取自定义寄存器的操作。

- 寄存器通知模块:在读取寄存器操作完成后,通知顶层模块。

在顶层模块中,我们需要实现对自定义寄存器的读取,具体来说,需要实现以下几个模块:

- 读取寄存器指令的发送模块:向iic slave发送读取指令。

- 数据解析模块:根据iic通讯协议的规定,解析iic slave设备返回的数据。

- 数据存储模块:将解析后的数据存储到相应的寄存器中。

- 带仿真模块的实现方案

为了方便调试和测试,我们需要在iic master和iic slave的实现中添加仿真模块。具体来说,需要实现以下几个模块:

- 时钟模块:产生时钟信号。

- 数据模块:产生数据并向iic通讯总线上发送数据。

- 仿真控制模块:控制仿真的开始、暂停、继续、停止等操作。

通过添加仿真模块,我们可以在硬件实现之前对iic master和iic slave的实现进行仿真调试,确保硬件实现的正确性。同时,通过不同的数据模拟,可以测试iic通讯协议在不同情况下的稳定性和可靠性。

总结:

本文主要介绍了基于FPGA的iic主从机驱动实现,包括iic slave和iic master的Verilog实现,以及实现master对slave自定义的寄存器读取,并提供带仿真模块的完整实现方案。通过本文的介绍,读者可以了解到iic通讯协议的实现原理和具体实现方法,同时也可以学习到Verilog语言的基础知识和有限状态机的实现方法。最终实现的iic主从机驱动可以应用于各种不同的设备间通讯中,具有较高的可靠性和稳定性,为物联网、智能家居等应用的发展提供了有效的支持。

相关代码,程序地址:http://lanzouw.top/697687398406.html