- 1[晓理紫]每日论文分享(有中文摘要,源码或项目地址)--大模型、扩散模型、视觉语言导航_retrieval-augmented score distillation for text-to

- 2MoveIt+ Gazebo 联合仿真环境搭建(巨简单版)_moveit! gazebo

- 3【Python】发送邮件,超详细看图敲码(附完整代码)一一CSDN21天学习挑战赛_python发送邮件代码

- 4java实现Linux服务器下载文件到windows指定目录_java 实现从linux 拷贝文件到window

- 5ComfyUI工作流自学笔记 三阶放大、背景更换、换脸工作流学习_改变背景comfyui 工作流

- 6数据结构——迷宫问题_数据结构迷宫问题

- 7ComfyUI 实力插件/模型 分享_comfyui 模型

- 8保姆级教程:最新下载及安装vscode(含常用插件)_vscode中文插件下载

- 9Spring Boot 从2.1.x 升级到3.0.x的艰辛历程_springboot2升级到3

- 10Android获取签名文件sha1值

Quartus 基本使用简介

赞

踩

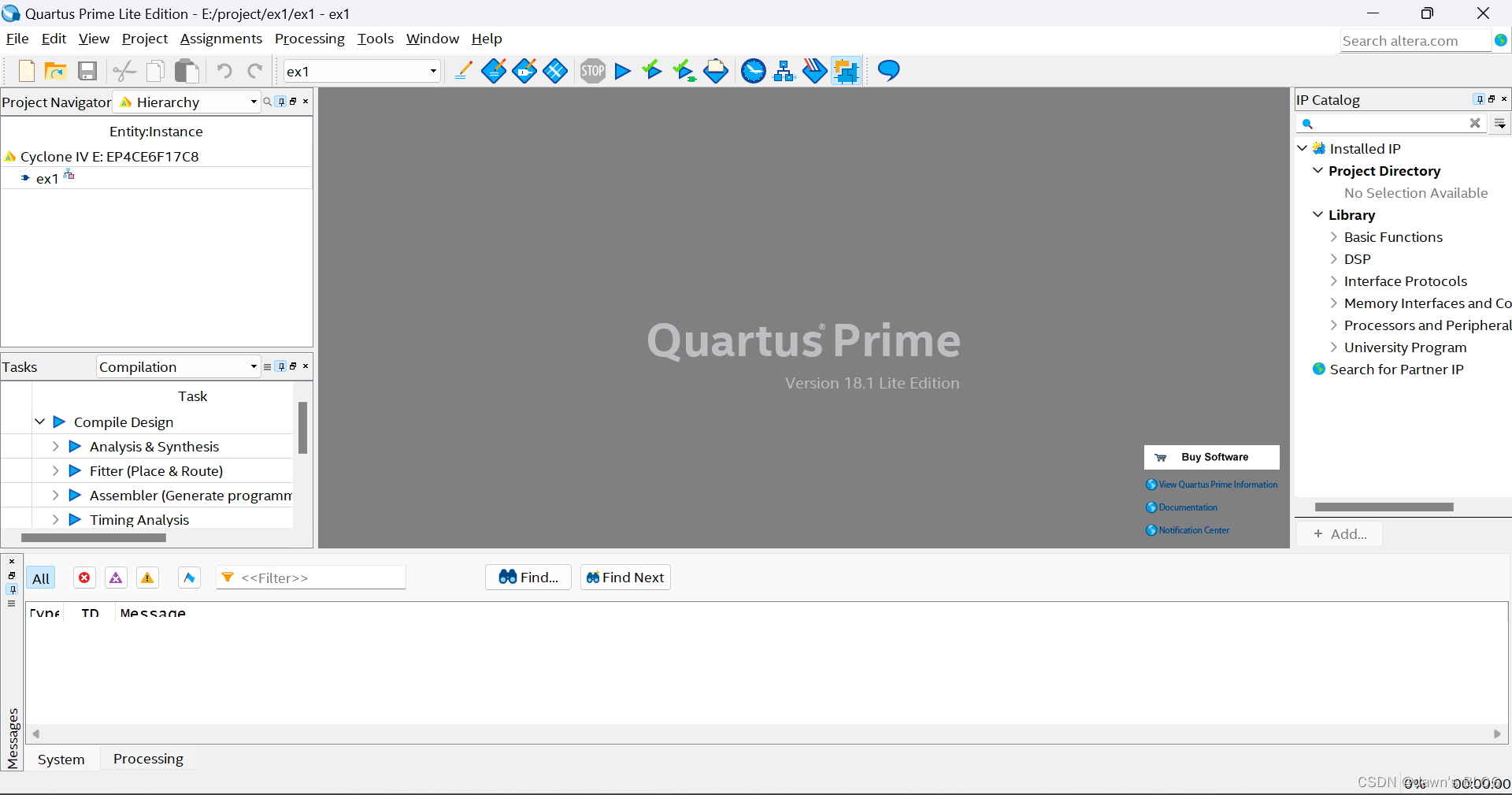

本文主要介绍如何使用Quartus18.1建立工程,并使用VWF进行功能仿真。

一、建立工程

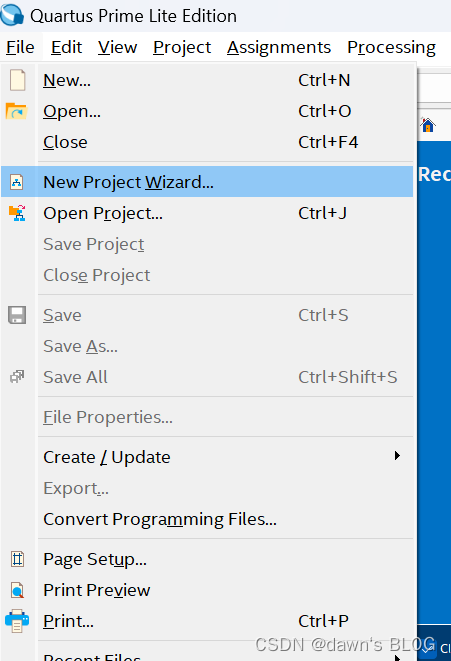

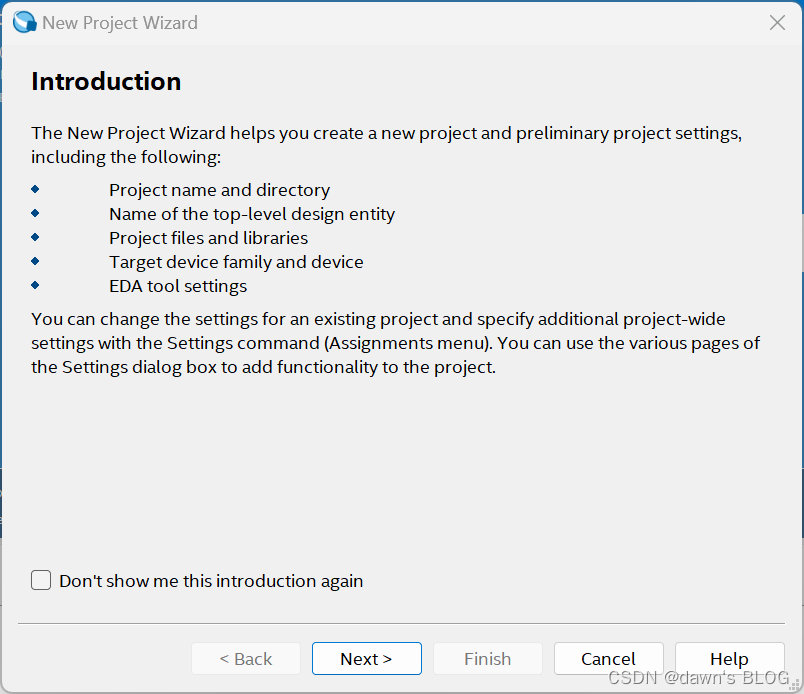

1、打开Quartus软件,选择File>New Project Wizard。进入新建工程向导,单击Next。

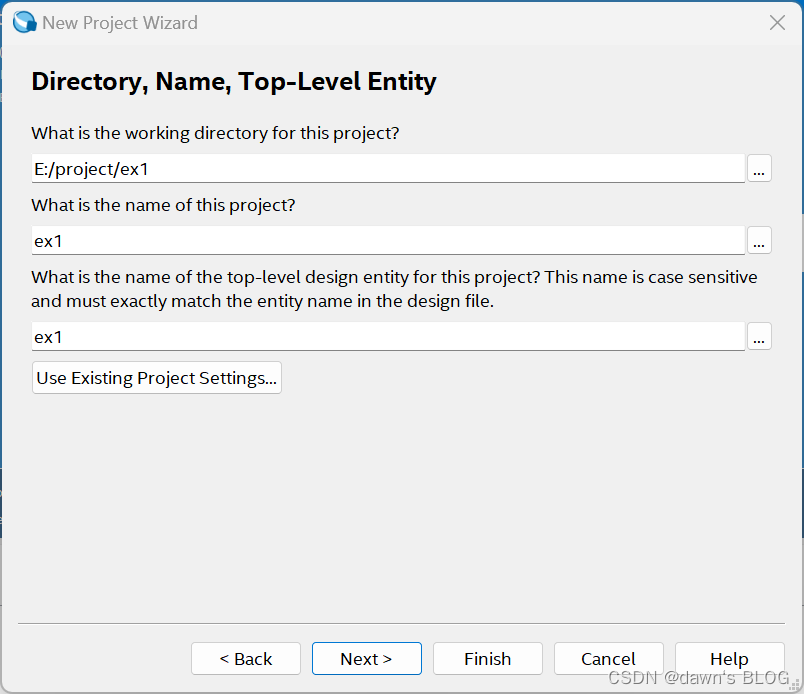

2、设置工程目录和工程名,而后点击Next。这里以ex1为例。

注意:不能有中文路径和空格!!!

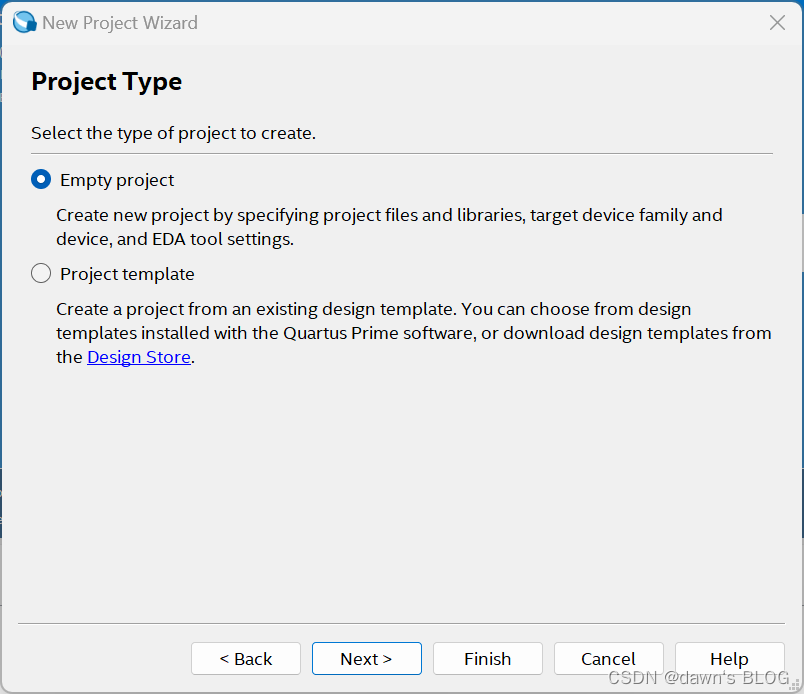

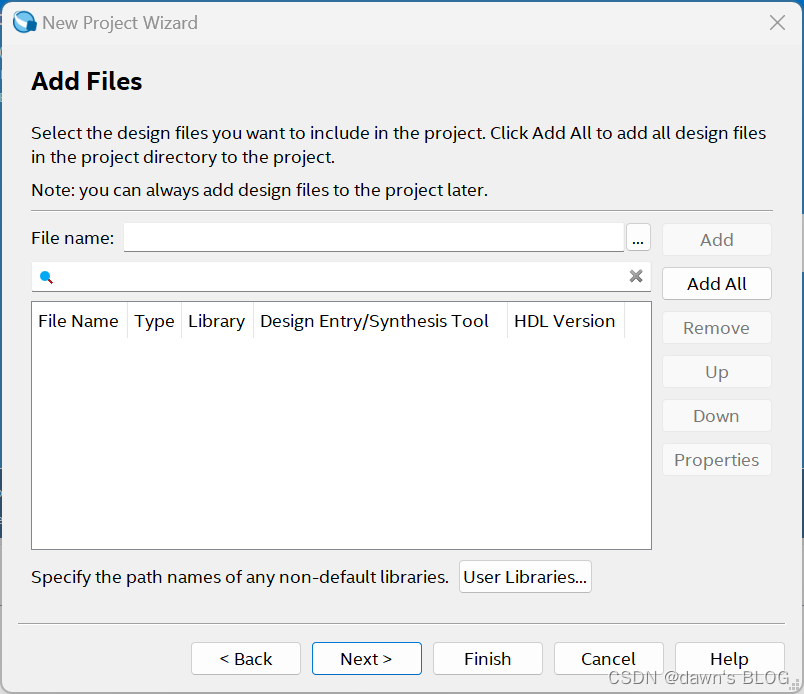

3、建立空白工程即可,点击Next。无需添加文件,继续点击Next。

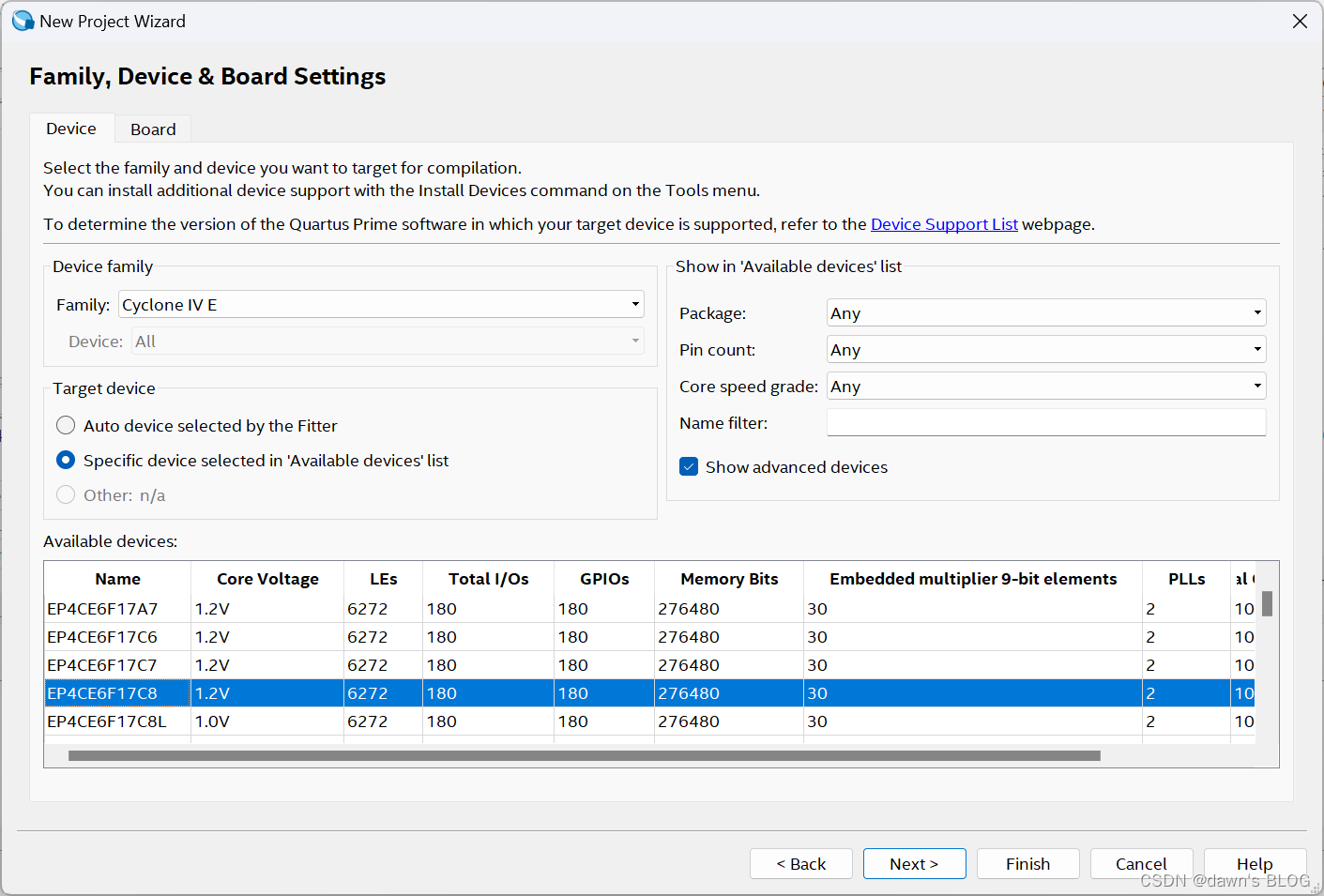

4、选择器件

需要根据开发套件中FPGA的具体型号进行选择,后面可以更改。这里选择的是EP4CE6F17C8。选择后继续点击Next。

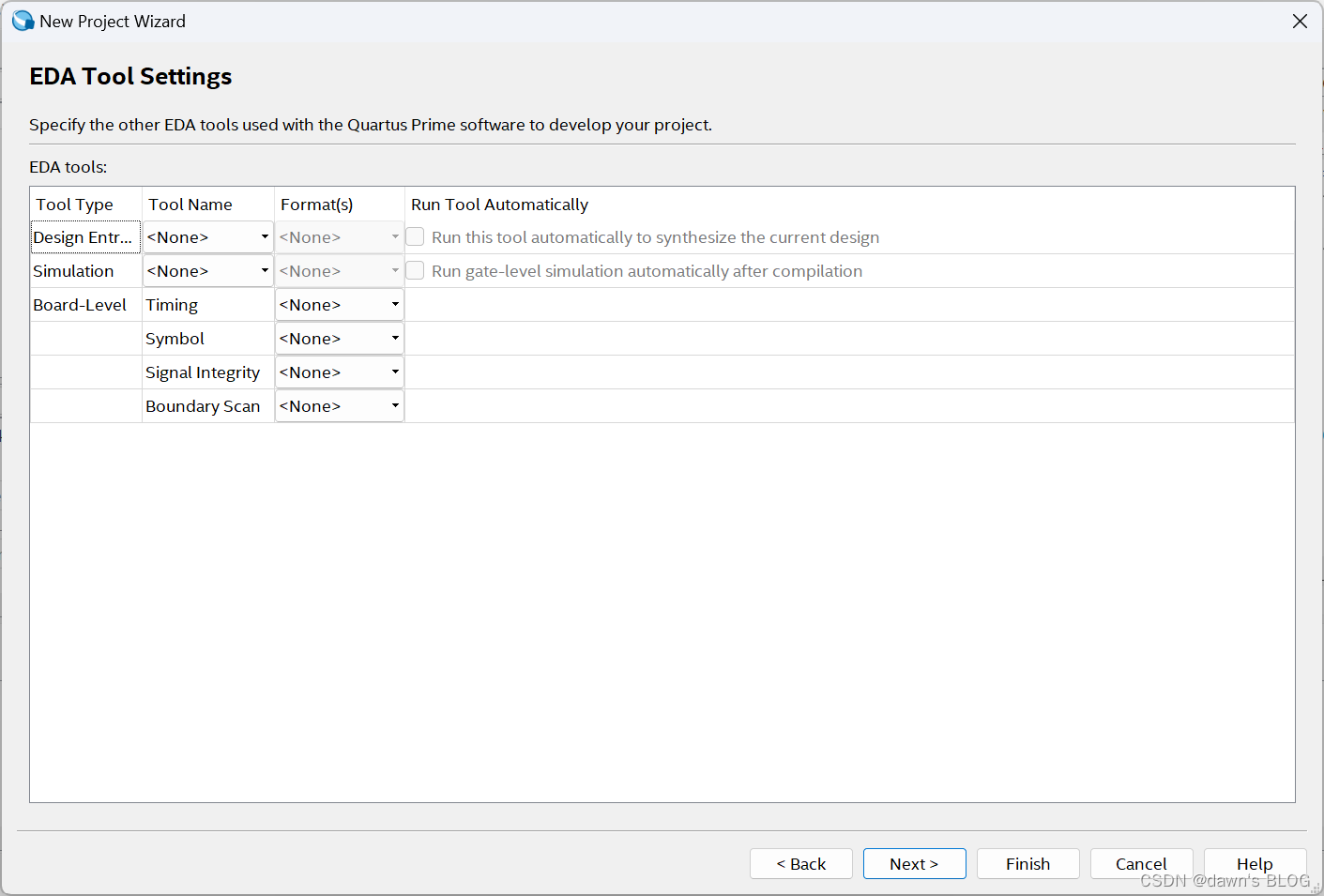

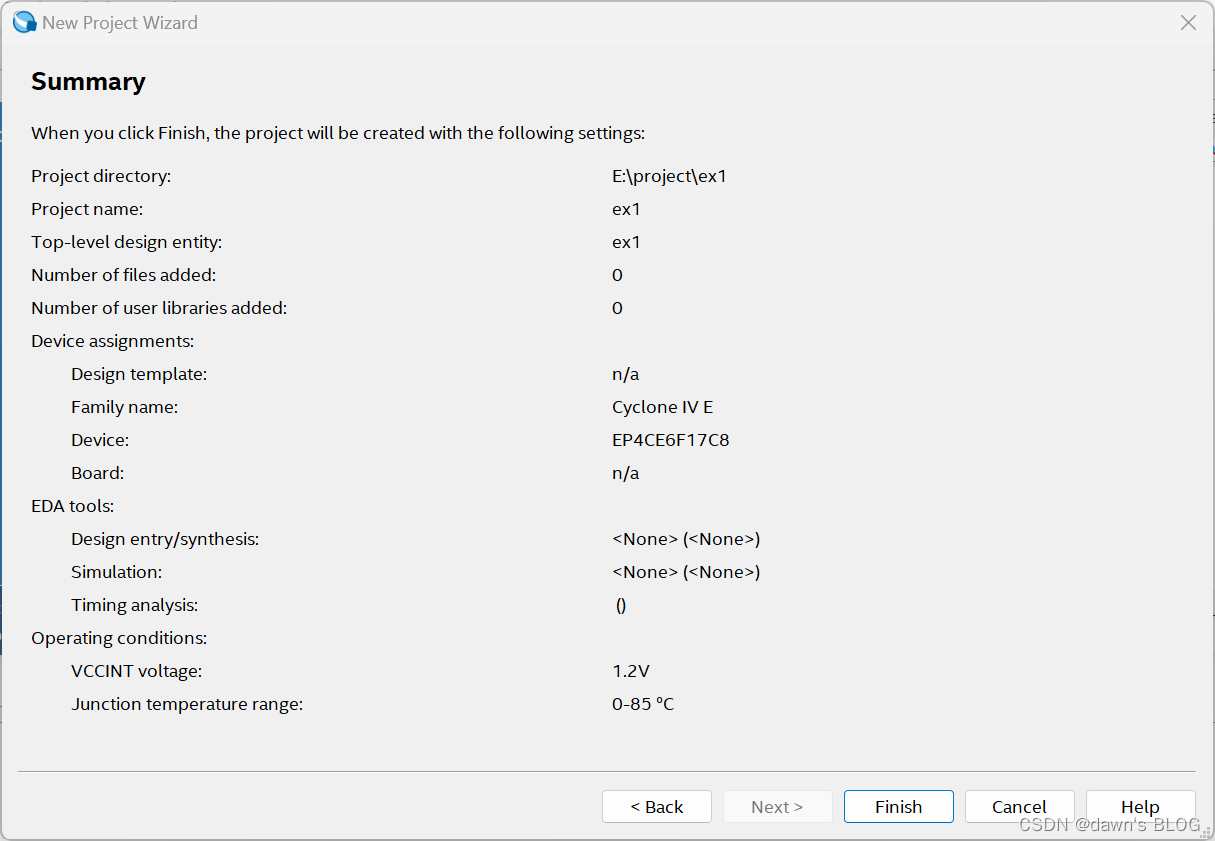

5、保持默认设置,点击Next。出现Summary界面,点击Finish,完成工程建立。

完成后进入下图所示界面。

二、输入设计

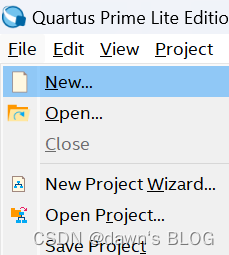

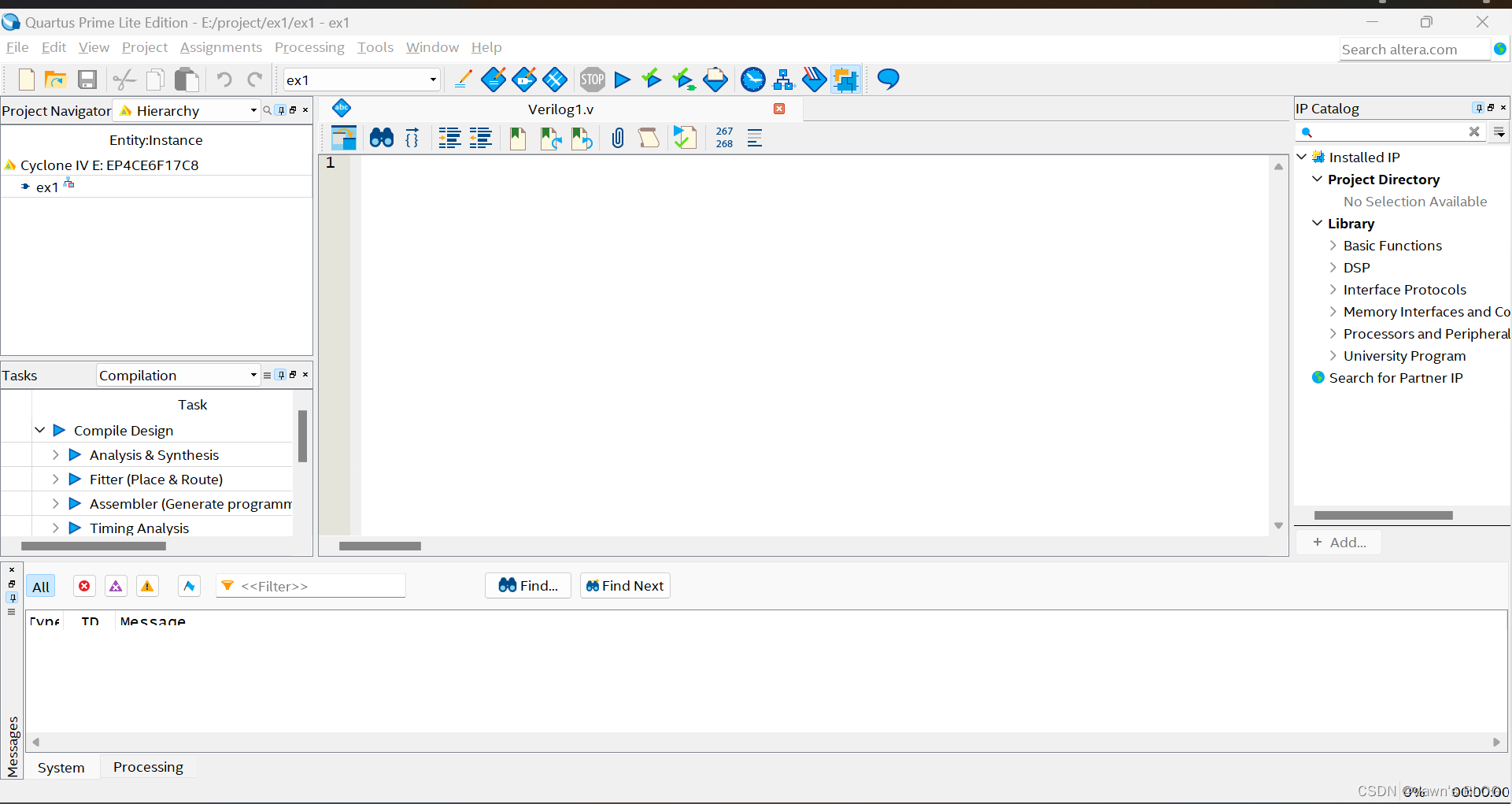

1、我们新建一个设计文件。选择File>New,打开下图所示窗口。选择 Verilog HDL File 后单击 OK。

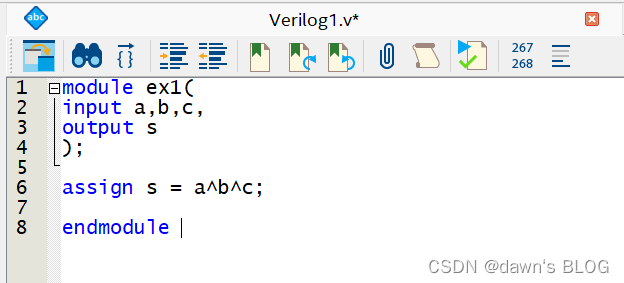

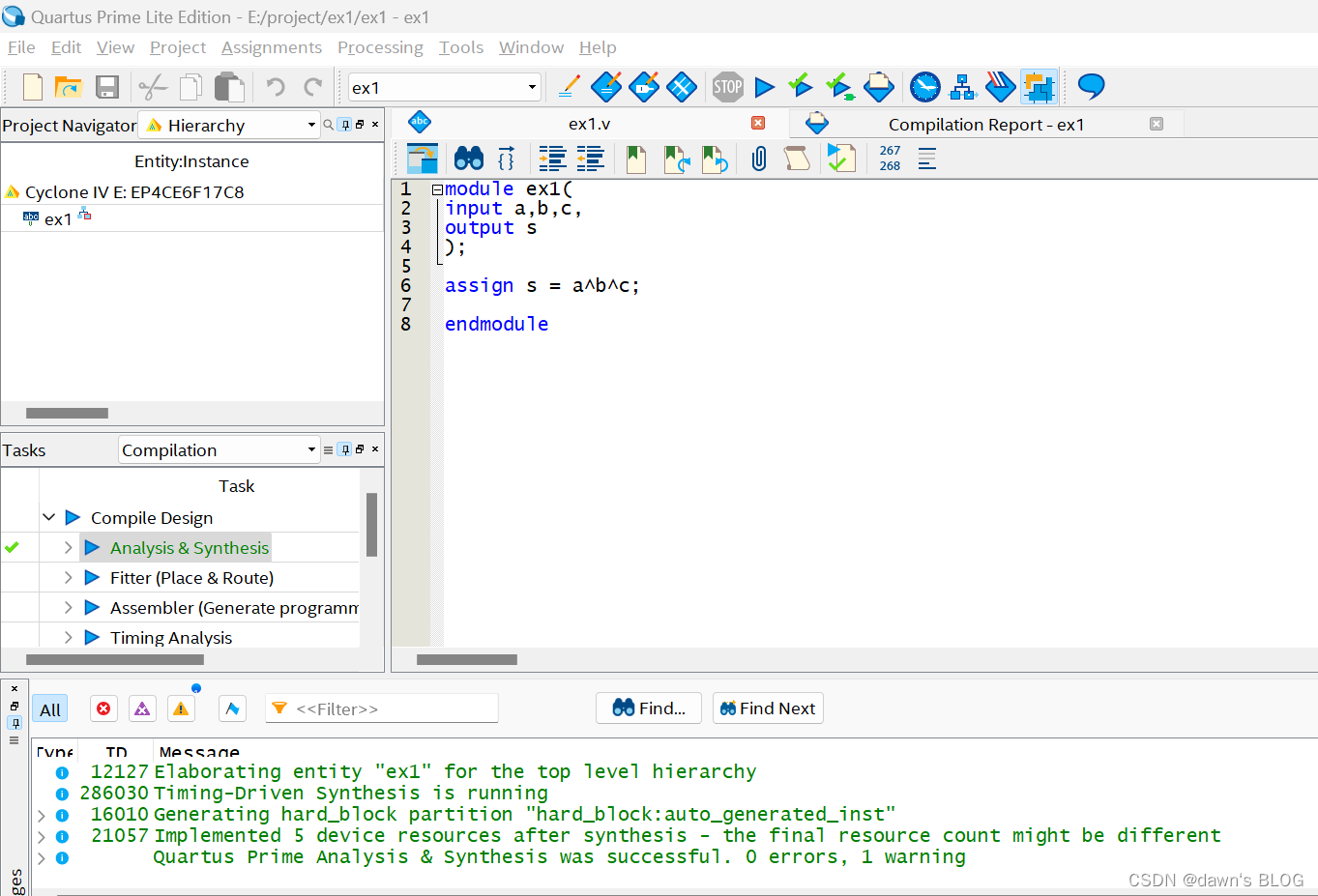

2、在中间代码编辑界面输入代码。

注意:这里module后的模块名称需要和工程名相同。这里为ex1。

- module ex1(

- input a,b,c,

- output s

- );

-

- assign s = a^b^c;

-

- endmodule

2、使用Ctrl+S,点击保存,保存文件。

注意:这里文件名需要和module后的模块名称相同。这里为ex1。

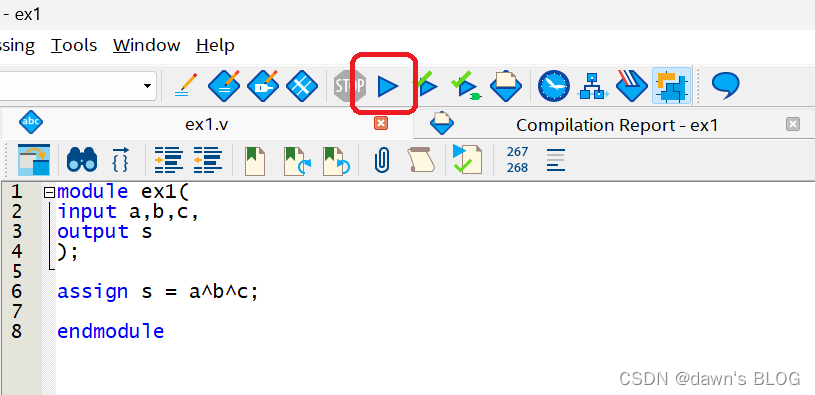

3、编译。选择Processing>Start Compilation 运行编译器,或者单击下图编译按钮,或者在Tasks下双击编译按钮。

4、编译完成后,没有报错,如下图所示。

三、功能仿真

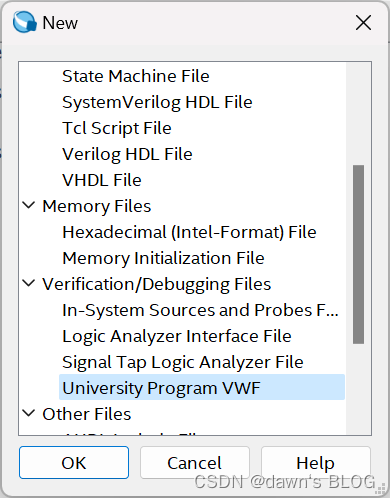

1、新建波形测试文件。选择File>New,打开下图所示窗口。选择University Program VWF 后单击 OK。

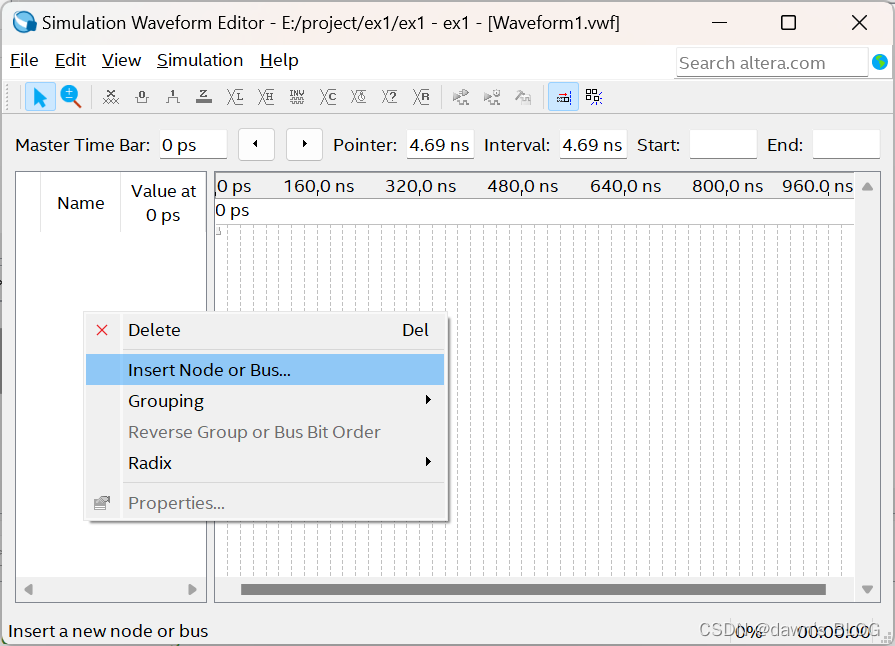

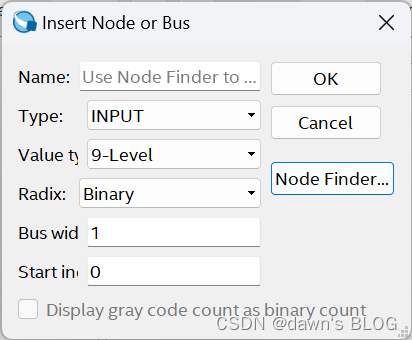

2、在下图界面左边空白处,单击右键,点击Insert Node or Bus;在弹出的窗口单击Node Finder。

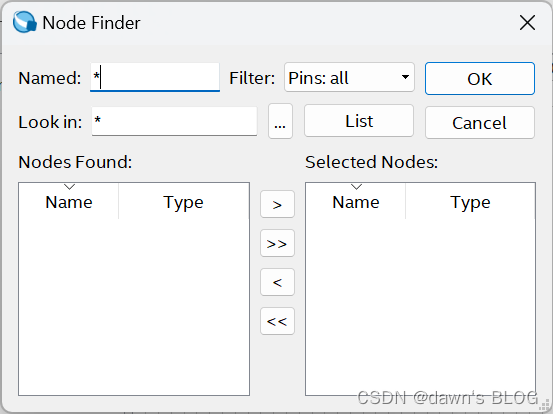

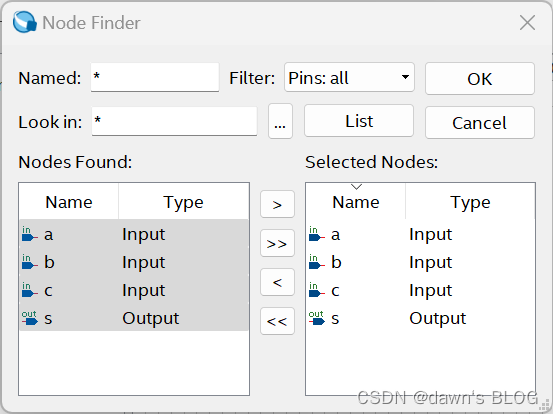

3、在Node Finder窗口选择List,列出了ex1的所有输入输出信号。点击>>图标,将所有信号添加到右侧,点击OK。再点击OK。回到vwf文件编辑界面。

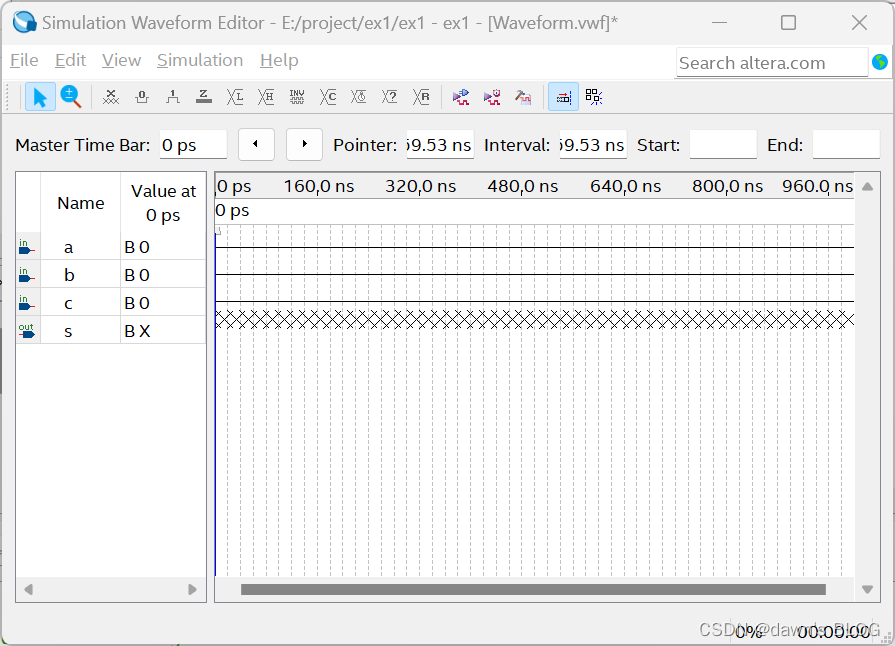

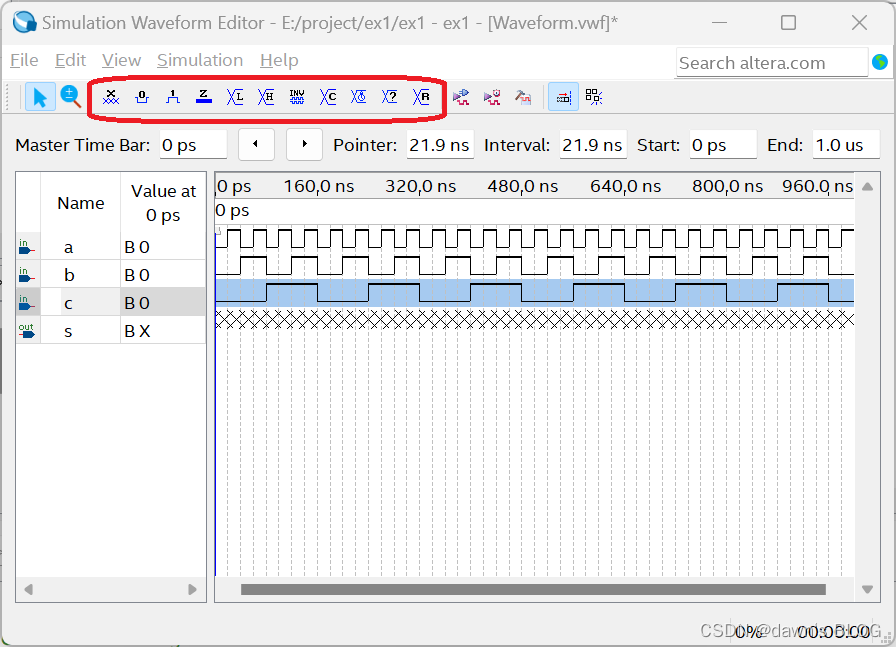

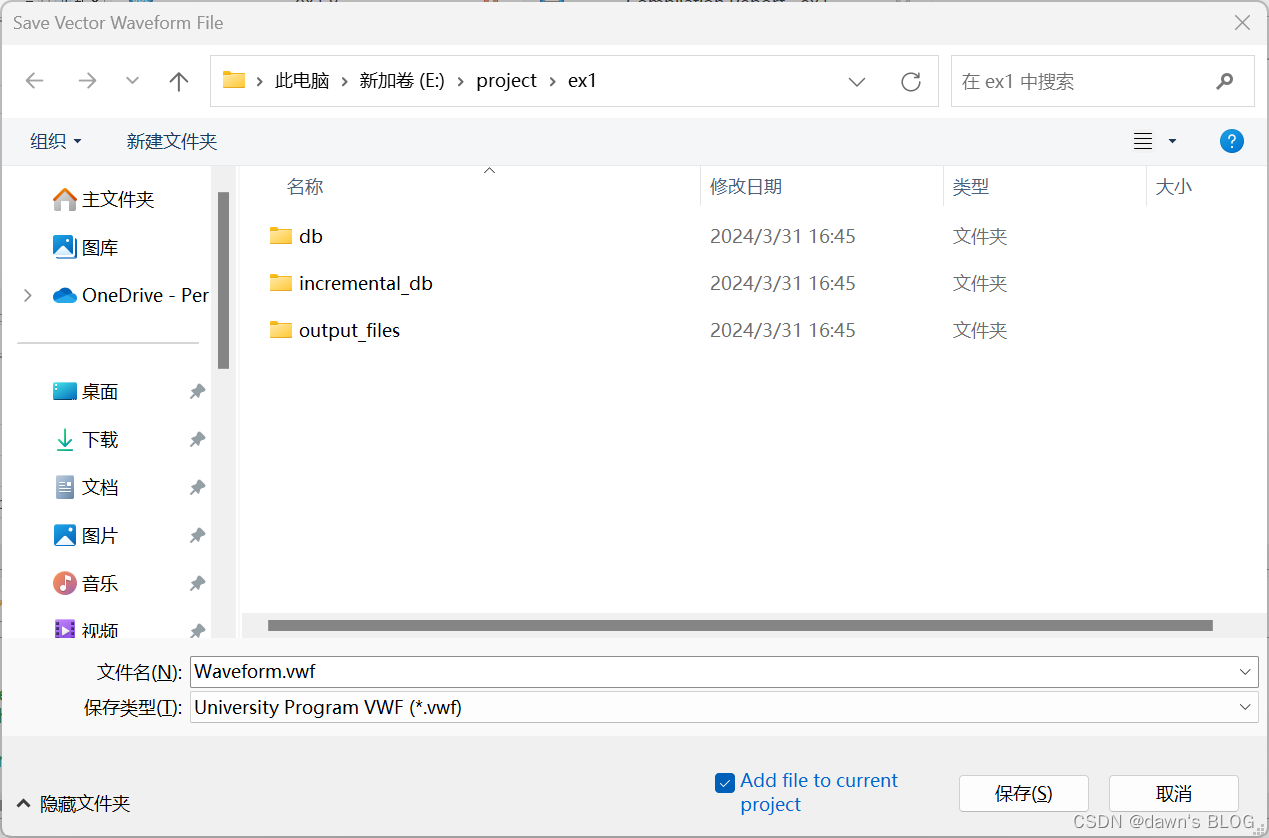

4、通过工具栏设置所有输入信号的波形。设置好后,使用Ctrl+S保存,不要更改文件名。

注意:不要更改.vwf的文件名!!!!

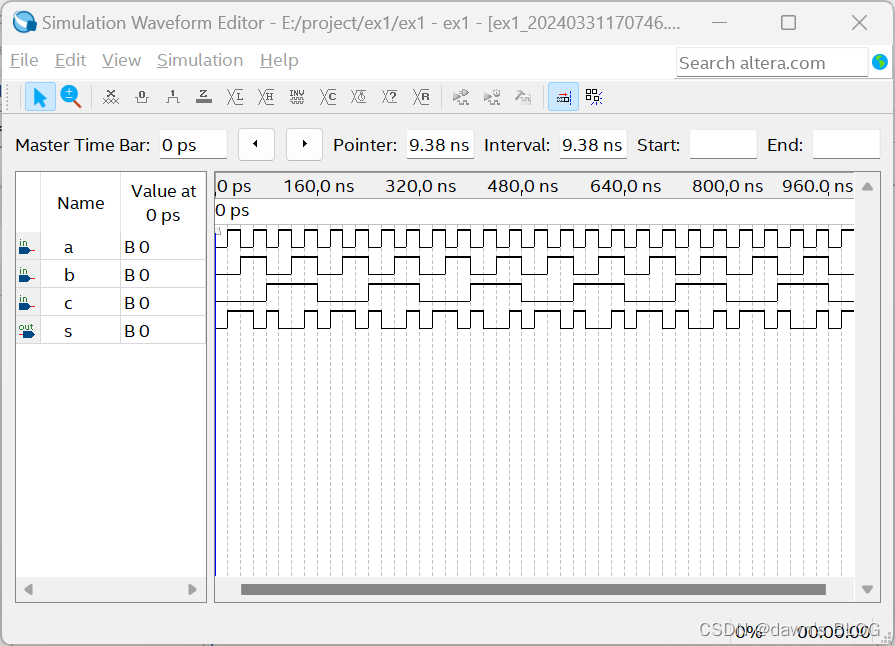

5、点击Simulation >> Run Functional Simulation,进行功能仿真。完成后,弹出仿真波形。对比波形,和设计逻辑 s = a^b^c相同。完成仿真。

四、小结

FPGA的开发流程包括了设计、仿真、下载等步骤。对于初学者来说,仿真可以快速验证设计的功能是否正确。

Quartus中建立仿真文件的方法有多种,其目的都是产生测试的激励信号,使用波形输入的方法,最为直观和便于理解。

此外,大部分EDA软件都以 工程 为基本组织结构,以实现对文件的管理和对设计流程的控制。