- 10基础学springboot之对数据库的增删改查_springboot数据库增删改查

- 2Android应用通过JNI调用ioctl操作设备驱动_android touch jni

- 3Leaflet官方教程(三)——Markers With Custom Icons

- 4python批量生成图表_教你用Python自动读取数据生成图表,产生的效益很可观

- 5深入学习java源码之Executors.newFixedThreadPool()与Executors.newCachedThreadPool()

- 6(附源码)spring boot宠物健康管理系统 毕业设计 201738_宠物信息管理系统

- 7Git版本管理工具

- 8macOS跨进程通信: XPC 创建实例_xpc通信

- 9【开发小程序的步骤】开发小程序的步骤是什么?_亲,开发制作小程序 首先需要注册并认证一个小程序,才能部署搭建并发布上线使

- 10shell 知:外部命令_-exec command {} +

深入 AXI4 总线(一)握手机制_axi4协议握手过程

赞

踩

VALID/READY 握手机制

AXI 总线共有 5 个独立的通道,分别为写地址,写数据,写回应,读地址,读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制。

VALID/READY 机制这个赛高啊,这个好啊,ARM 的手册上这么夸:

作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息放到的写总线上,并保持。

接收方置高 READY 信号表示接收方已经做好接收的准备。

所谓的双向流控机制,指的是发送方通过 VALID 信号置起控制发送速度的同时,接收方也可以通过 READY 信号的置起与否控制接收速度,反压发送方的发送速度。

当双方的信息同时为高,时钟上升沿到达后,一次数据传输完成,在 1 到 n 次时钟上升沿后,双方传完了要传的信息后,两信号同时拉低。

VALID/READY 的三种情况

VALID/READY 信号按照到达的先后顺序可以分为 3 种情况:

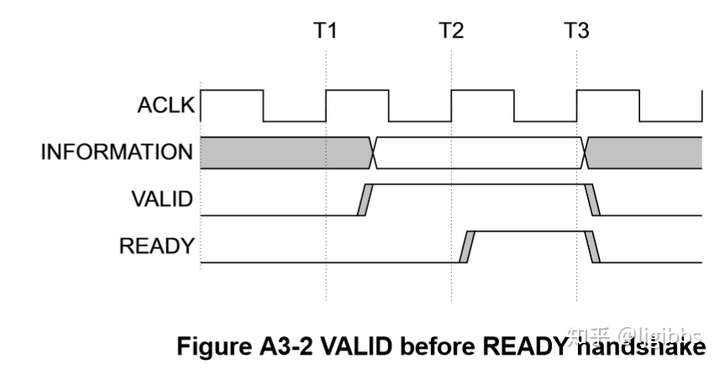

1.VALID 信号先到达

发送方 VALID 信号早早就到了,这时还不到 T2 时刻,并带来了新鲜的数据(数据通道),地址或者控制信息(地址通道)。

但过了 T2 也没见到接收方的 READY 信号。原来是接收方还忙着,可能上一次的数据还没存完,还堵在数据通路上,忙过了 T2 才来。

好吧,那也行,T3 时刻传输完成。

在这种情况下,接收方通过 READY 信号控制了传输速度,反压了发送速度。

协议规定:VALID 信号一旦置起就不能拉低,直到此次传输完成。对于接收方编程来说,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能在置起 VALID 信号之前就光等待 READY 信号。

这句阅读理解有点难,原文为:

作者个人从总线接口编程的角度理解,READY 信号可能先到达,如下图的情况。但是发送方编程时,不能依赖 READY 信号先到达的情况。不能将 READY 信号置高作为置高 VALID 的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动的过程。接收方按照协议可以依赖发送方,但如果此时发送方也依赖接收方,就会造成死锁的情况,所以协议在这里规定了 VALID 信号的主动性。

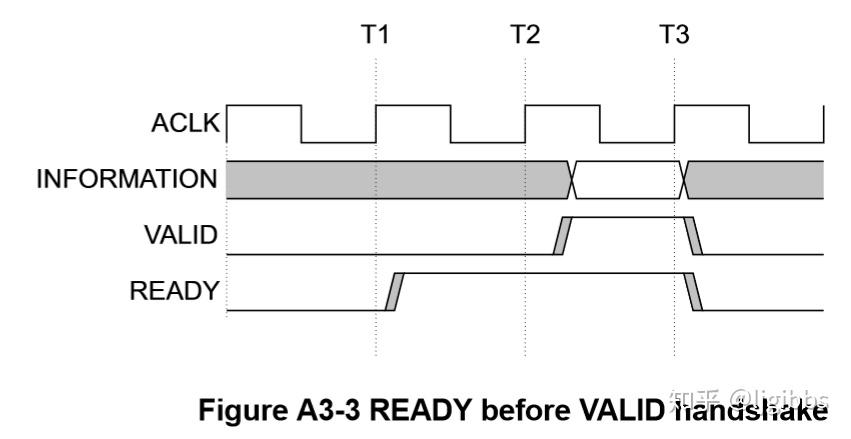

2.READY 信号先到达

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后拉低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

3.同时到达

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地完成了,一个时钟周期里就完成了。