- 1数据结构之单链表详解(C语言手撕)

- 2决策树剪枝python实现_决策树及其python实现

- 3Mac下编写C或C++_mac c++

- 4Android中SharedPreferences的理解_android sharepreference 创建了重复名字

- 5request.getParameter()、request.getInputStream()和request.getReader()

- 6Shell入门之二_for cls, ids in :

- 7girdview分组,统计,排序的解决方案_dev gridveiw 按字段分组后,按其他字段排序

- 8《HarmonyOS开发 – OpenHarmony开发笔记(基于小型系统)》第1章 OpenHarmony与Pegasus物联网开发套件简介_pegasus智能家居开发套件

- 9一站式在线协作开源办公软件ONLYOFFICE,协作更安全更便捷_在线office 开源

- 10临近秋招了,讲讲大家关心的问题_嵌入式秋招要刷leetcode吗

Vivado设计资源优化 ,查看各子模块资源占用的方法大全_vivado 中如何看哪个模块占用的逻辑资源最多

赞

踩

在FPGA开发中,资源占用和时序约束一直是主要问题。为了解决这些问题,Vivado提供了丰富的优化工具和资源占用分析工具,帮助工程师优化FPGA设计,深入了解各个子模块的资源使用情况。

本文将从资源占用的角度,介绍Vivado中如何进行FPGA设计资源优化以及查看各子模块资源占用的方法。通过使用Vivado提供的优化工具,可以平衡FPGA设计中的资源和时序,提高设计质量和性能。同时,还可以通过资源占用分析工具深入了解各个子模块的资源使用情况,便于精确地掌握设计瓶颈,并作出相应的调整。

一、FPGA 设计资源优化

FPGA 设计的资源消耗往往是开发者所面临的一个主要问题,尤其是在使用大型的 IP 核时,资源的消耗可能会引起 FPGA 设计的失败。因此,如何有效地减少资源消耗,优化 FPGA 设计是非常重要的。下面介绍 Vivado 中的资源优化方法。

1、合并相同逻辑

相同逻辑的实例可以在综合阶段或后续阶段合并,从而减少资源使用。Vivado 工具链会自动检测到相同的逻辑,并进行优化。对于复杂的逻辑设计,建议对其进行模块化,可提高综合效率和资源利用率。

2、移除未使用逻辑

在 FPGA 设计中,经常会存在部分逻辑未被使用,这些未使用逻辑将占用 FPGA 资源,添加不必要的成本。因此,移除未使用逻辑是优化 FPGA 设计的重要步骤之一。Vivado 提供了“SYNTH_OPT”综合选项,可在综合阶段移除未使用的逻辑,提高资源利用效率。

3、 选择最优综合策略

Vivado 工具链提供多种综合策略,例如低功耗、快速、面积优化等等。不同的策略会影响资源利用率、性能和功耗。工程师应根据实际需求选择最优的综合策略。

4、优化时序

FPGA 设计中时序是一个非常重要的因素,它直接关系到 FPGA 的性能和资源利用率。Vivado 工具链提供了多种时序分析和优化工具,例如时钟分析器和时序约束器,可用于分析和优化 FPGA 设计的时序,以提高资源利用率和性能。

二、查看各子模块资源占用的方法

在了解了 FPGA 设计资源优化的基本方法后,下面介绍如何查看各子模块的资源占用情况。

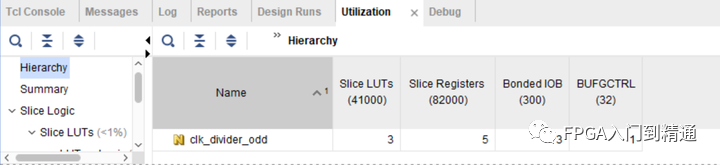

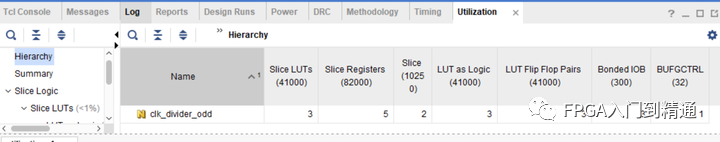

1、综合报告

在 Vivado 中,综合报告可以展示设计的层次结构、每个模块的资源占用和时序分析等信息。要生成综合报告,有以下2种方式

(1)图形界面操作

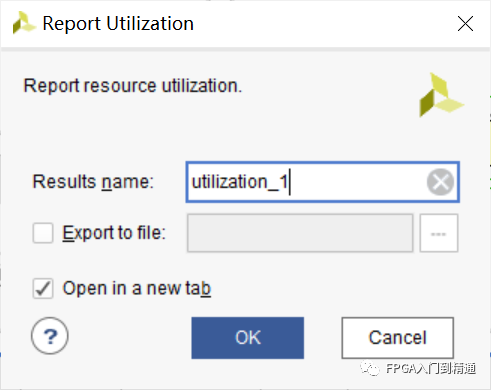

完成综合后,在Vivado IDE左侧的Flow Navigator,“SYNTHESIS”点击Open Synthesized Design,然后点击report_utilization。

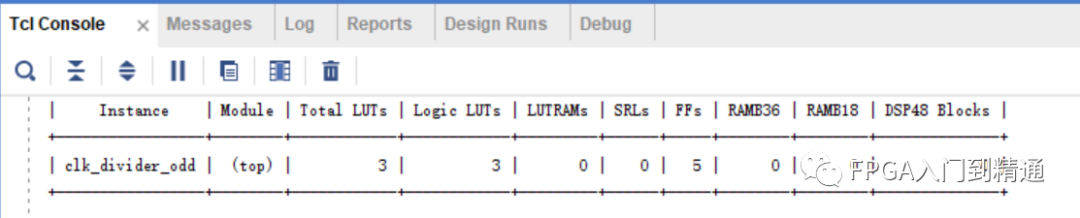

(2)TCL命令操作

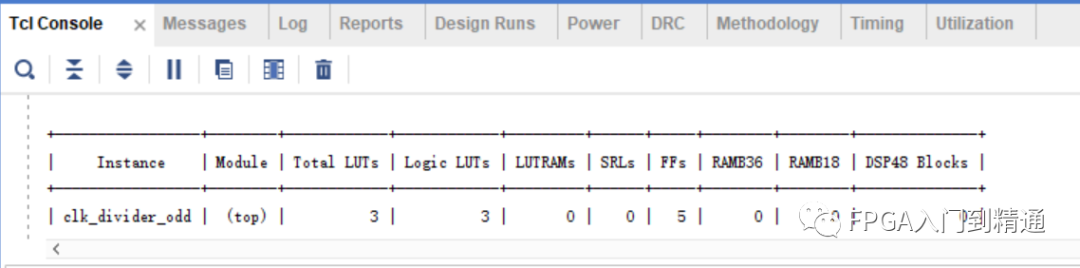

1)综合后,执行Open Synthesized Design,再在 Vivado 的 Tcl Console 中输入以下命令:report_utilization -hierarchical

2)执行上述命令后,Vivado 将生成一个 HTML 格式的综合报告文件。

2、实现报告

在 Vivado 中,实现报告提供了更为详细的资源占用情况分析。生成实现报告的方法,有以下2种方式

(1)图形界面操作

完成Implementation后,在Vivado IDE左侧的Flow Navigator点击Open Implemented Design,然后点击report_utilization。

(2)TCL命令操作

1)综合后,执行Open Implemented Design,在 Vivado 的 Tcl Console 中输入以下命令:report_utilization -hierarchical

2)执行完上述命令后,Vivado 会生成一个文本文件,该文件记录了包括复杂度、功耗、时序等信息的实现报告。

3、IP 核报告

IP 核的资源占用情况也可以通过 Vivado 工具查看,只需按照以下步骤操作:

1)在 Vivado 的 Tcl Console 中输入以下命令:report_ip_status

2)执行完上述命令后,在弹出的对话框中,可以选择查看 IP 核资源使用情况的详细信息。

三、总结

综上所述,Vivado 提供了丰富的工具和资源占用分析工具,可帮助工程师优化 FPGA 设计,并深入了解各个子模块的资源使用情况。因此,精通这些工具和方法对于 FPGA 开发人员来说是非常重要的。通过上述方法,可以更加深入地了解各个子模块的资源占用情况,并进行针对性优化,进而提高 FPGA 设计的性能和资源利用率。

本文将不断定期更新中,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

公众号为“FPGA入门到精通”,免费学习资料大礼包下载,github开源代码:“FPGA知识库”

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。