- 1单通道说话人语音分离——Conv-TasNet(Convolutional Time-domain audio separation Network)

- 2Windows使用远程桌面连接Debian12的xfce4_远程桌面debian12

- 3CorelDRAW2024破解注册码序列号分享_coreldraw 2024 注册机panbaidu

- 4python:一看就会,一写就废的 Flask 框架(一)环境搭建_springboot对比flask

- 5Codeium-个人用户永久免费的AI编程工具,同时具备Chat能力,这才是我想要的_codeium国内能用吗

- 6Pythorch 教程-Neural Network

- 7Java中的List<T>对象与Json格式的字符串的相互转换_java list转json

- 8python 写文件的编码问题_python写文本编码

- 9大数据毕业设计选题 python毕业设计_基于hadoop的公共自行车数据分布式存储和计算,取2023年2月某共享单车在桂林的车辆

- 10【软考系统架构设计师】2019年下系统架构师论文写作历年真题_详细阐述有哪些不同的软件系统架构评估方法,并从评估目标、质量属性和评估活动等

SRIO IP介绍 (二) SRIO IP配置及上板验证

赞

踩

上讲我们介绍了SRIO的一些基础知识,例如SRIO系统架构,HELLO包格式,以及相对应的时序等。了解了这些基础知识后,我们就来学习一下怎么去使用SRIO IP。大家通过第一讲的学习可能会觉得SRIO的内容实在是太多了,但是它使用起来是非常简单的,通过本文的学习,相信大家都能够学会SRIO IP的使用,咱们接着往下看。

1.设计流程步骤

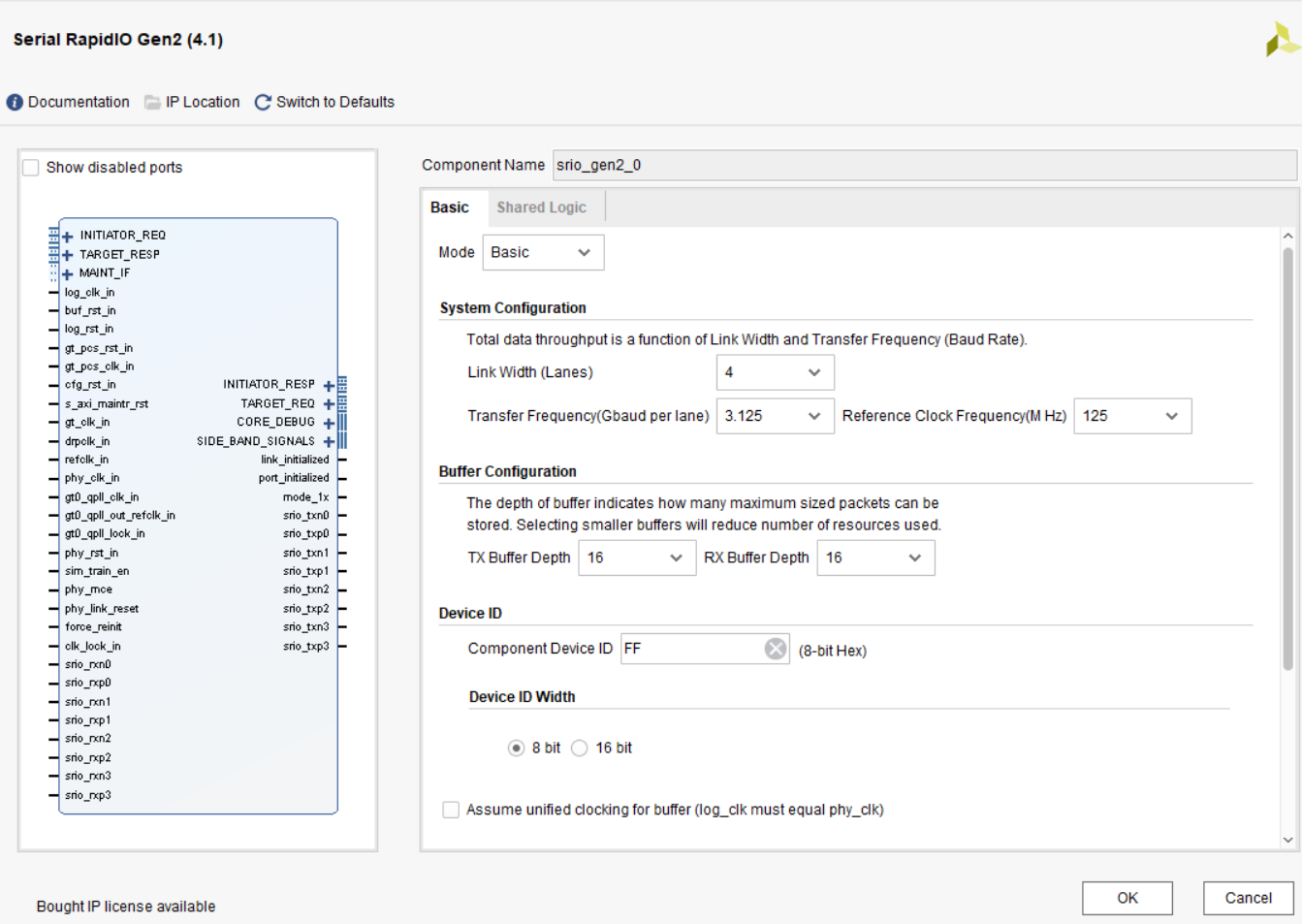

首先我们先从vivado中打开SRIO IP,如图所示:

Mode:可以选择Basic模式和Advanced模式,区别就是高级模式包括所有配置选项,而基本模式在单个页面上仅显示一组简化的常用选项。一般情况下,Basic模式已经能够满足我们的需求了,因此我们就以Basic模式为例,给大家介绍SRIO IP的使用。

Link Width:链路宽度表示每个方向生成的串行通道的数量。Serial RapidIO Gen2内核可以有一个、两个或四个通道。系统的带宽随着通道的数量而增加。在这里需要给大家强调的一点就是,通道数的增加,并不会增加SRIO传输数据的位宽。

这里要注意和Aurora进行区分。那么增加通道的数量会带来什么影响呢,没错,就是速率的影响,它会把SRIO的输出时钟log_clk的频率提高,由于数据位宽一直都是64bit,并且数据的传输就是在log_clk下进行的,那么,通道数增加,也就意味着数据传输的速率变快了。

Transfer Frequency:传输频率表示Serial RapidIO内核的每通道波特率。每个串行收发器以选定的线路速率运行。系统的带宽随着传输频率的增加而增加。那么它与log_clk的关系是什么呢,其实可以简单理解为log_clk=线速率*通道数/80,除以80的原因是SRIO也是采用8/10B编码,所以64bit数据就需要16bit的开销。那如果线速率是3.125Gbps,1通道,log_clk的时钟周期就25.6ns。

最后再补充一句,如果我们查阅官方给的手册会发现,有太多个时钟了,比如phy_clk,gt_clk,gt_pcs_clk等,但是其实我们实际上使用的就只有逻辑时钟,其他那些时钟只需要大概了解一下就行,当然以上说的这些时钟在下一讲介绍官方例程的时候,我们也会提到。

Reference Clock Frequency:参考时钟频率是通过专用收发器参考时钟引脚引入FPGA的时钟速率。参考时钟并不会影响我们的log_clk,在下一讲我们也会对其他的时钟作详细解释。

Buffer Configuration:发送和接收缓冲区的深度可以自定义为8、16或32。此数字表示缓冲区能够存储的数据包数量。选择较小的缓冲器深度节省资源(主要是块RAM和LUT),而最大缓冲器深度产生最大吞吐量。

Component Device ID:组件设备ID确定基本设备ID CSR的重置值。可以类比理解为收发数据需要知道对方的ID号,自己的ID就是源ID,对方的ID就是目的ID。

Device ID Width: 核心的设备ID宽度应与链路伙伴的设备ID宽度匹配。否则,交易可能会因标头移位而被误解。大多数系统使用8位设备ID,但SRIO Gen2端点也通过此选项提供大型系统支持。

Flow Control:这些选项指示变送器使用的流量控制类型。

Shared Logic:我们直接包含在例程里面就可以了。

到这里之后我们的IP就算配置完成了,接下来就带大家一起学习一下怎么使用它进行数据的传输

2.收发测试

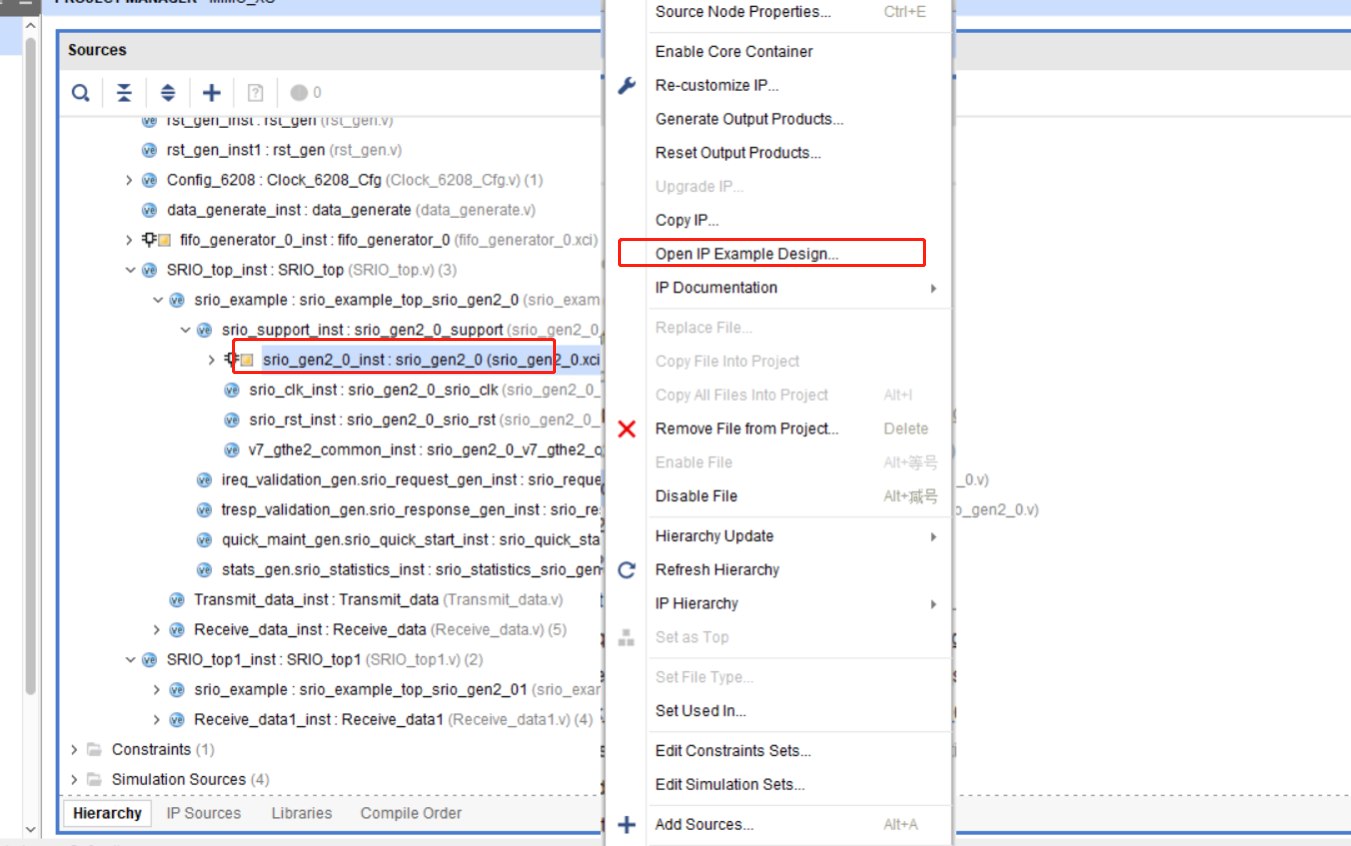

首先右键单击 SRIO IP,选择open IP Example Design

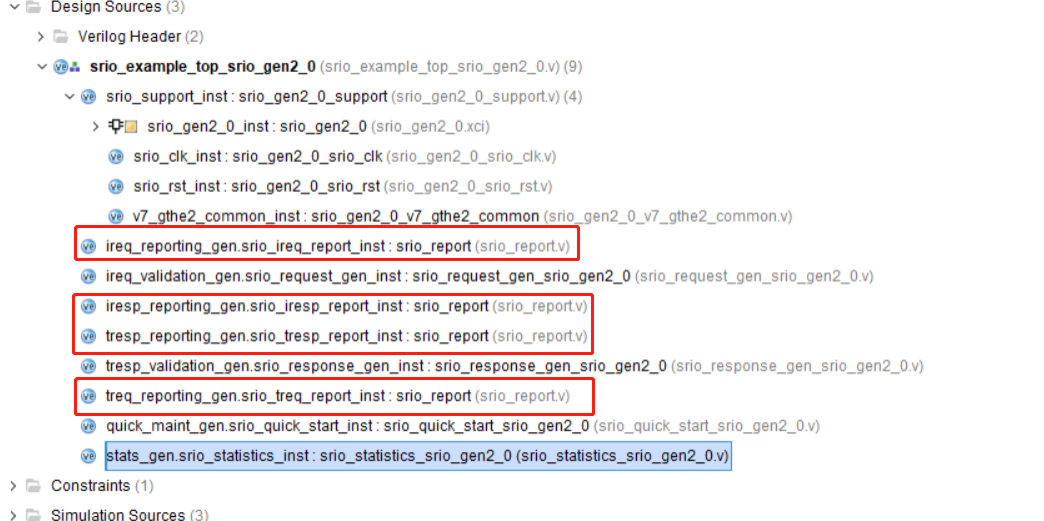

之后大家会看到有很多子文件,如下图所示:

用红色圈出来的有4个子文件,这几个文件可以直接删除,并且在Example_top模块也删除,本节内容就用最简单的方法,教会大家怎么使用SRIO IP进行数据的收发,更为详细的解释,会在下一讲说明。

然后大家其实可以发现,这些子文件其实全都都在Example_top模块下的。那我们要收发数据其实也很简单。首先自己定义一个发送和接收模块,其次,再定义一个顶层top模块,top模块作用就是把Example_top、Transmit、Receive模块连接到一起。

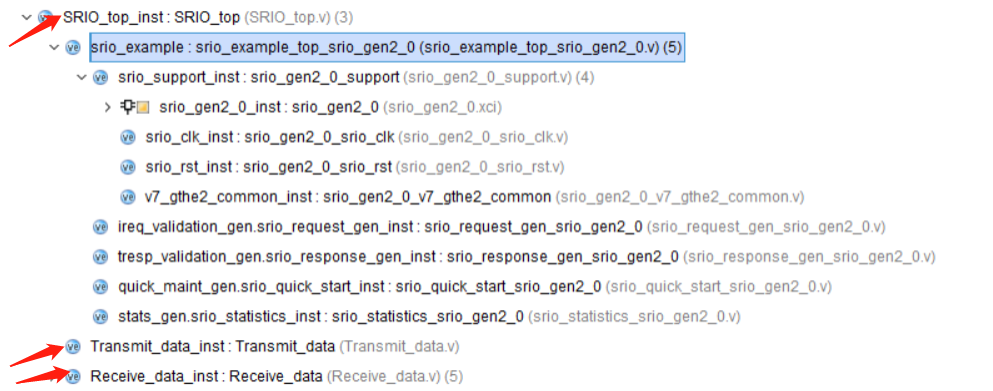

如下图所示:

我们定义了发送模块、接收模块、顶层模块,并且把IP核的子文件和自定义的文件连接起来。接下来,给大家介绍一下对应端口的连接,首先就是srio_example模块,也就是子文件的顶层,我们看一下它的端口信号:

- `timescale 1ps/1ps

- (* DowngradeIPIdentifiedWarnings = "yes" *)

-

-

- module srio_example_top_srio_gen2_0 #(

- parameter SIM_VERBOSE = 1, // If set, generates unsynthesizable reporting

- parameter VALIDATION_FEATURES = 1, // If set, uses internal instruction sequences for hw and sim test

- parameter QUICK_STARTUP = 1, // If set, quick-launch configuration access is contained here

- parameter STATISTICS_GATHERING = 1, // If set, I/O can be rerouted to the maint port [0,1]

- parameter C_LINK_WIDTH = 4

- )

- // port declarations ----------------

- (

- // Clocks and Resets

- input sys_clkp, // MMCM reference clock

- input sys_clkn, // MMCM reference clock

-

- input sys_rst, // Global reset signal

-

- // high-speed IO

- input srio_rxn0, // Serial Receive Data

- input srio_rxp0, // Serial Receive Data

-

- input srio_rxn1, // Serial Receive Data

- input srio_rxp1, // Serial Receive Data

-

- input srio_rxn2, // Serial Receive Data

- input srio_rxp2, // Serial Receive Data

- input srio_rxn3, // Serial Receive Data

- input srio_rxp3, // Serial Receive Data

-

- output srio_txn0, // Serial Transmit Data

- output srio_txp0, // Serial Transmit Data

-

- output srio_txn1, // Serial Transmit Data

- output srio_txp1, // Serial Transmit Data

-

- output srio_txn2, // Serial Transmit Data

- output srio_txp2, // Serial Transmit Data

- output srio_txn3, // Serial Transmit Data

- output srio_txp3, // Serial Transmit Data

-

- input sim_train_en, // Set this only when simulating to reduce the size of counters

- output [7:0] led0

-

- );

1. Parameter定义的5个参数咱们是不用管的,在IP核配置完成之后,这里的参数就会定下来,其实这也就是官方例程的魅力所在,基本上都是参数化来写的程序。

2. 接下来,又定义了4个通道的接收,4通道的发送,当然这里是因为我的IP配置的是4通道,并且高速数据的传输大都采用差分信号线。

3. 然后就到了 input sim_train_en, output [7:0] led0;这两个信号在实际使用的时候用不到,我们直接在对应地方删除就好,或者就是wire一下,不要放到端口信号那里。

4.我们需要再加几个信号,就能完成端口的例化了,当然也非常简单,我们要自己收发数据,就需要自己产生发送、接收有效信号等。总共需要加14个端口信号,6个是发送数据相关的,6个是接收信号相关的,还有两个是链路初始化相关的,SRIO进行通信,首先就需要把链路建立起来以后,才能做一些数据的收发,如下所示:

- `timescale 1ps/1ps

- (* DowngradeIPIdentifiedWarnings = "yes" *)

-

-

- module srio_example_top_srio_gen2_0 #(

- parameter SIM_VERBOSE = 0, // If set, generates unsynthesizable reporting

- parameter VALIDATION_FEATURES = 1, // If set, uses internal instruction sequences for hw and sim test

- parameter QUICK_STARTUP = 1, // If set, quick-launch configuration access is contained here

- parameter STATISTICS_GATHERING = 1, // If set, I/O can be rerouted to the maint port [0,1]

- parameter C_LINK_WIDTH = 4

- )

- // port declarations ----------------

- (

- // Clocks and Resets

- input sys_clkp, // MMCM reference clock

- input sys_clkn, // MMCM reference clock

-

- input sys_rst, // Global reset signal

-

- output log_clk,

- // high-speed IO

- input srio_rxn0, // Serial Receive Data

- input srio_rxp0, // Serial Receive Data

-

- input srio_rxn1, // Serial Receive Data

- input srio_rxp1, // Serial Receive Data

-

- input srio_rxn2, // Serial Receive Data

- input srio_rxp2, // Serial Receive Data

- input srio_rxn3, // Serial Receive Data

- input srio_rxp3, // Serial Receive Data

-

- output srio_txn0, // Serial Transmit Data

- output srio_txp0, // Serial Transmit Data

-

- output srio_txn1, // Serial Transmit Data

- output srio_txp1, // Serial Transmit Data

-

- output srio_txn2, // Serial Transmit Data

- output srio_txp2, // Serial Transmit Data

- output srio_txn3, // Serial Transmit Data

- output srio_txp3, // Serial Transmit Data

- /*********************************************/

- input val_ireq_tvalid,

- output val_ireq_tready,

- input val_ireq_tlast ,

- input [63:0] val_ireq_tdata , //待发送给DSP的数据

- input [7:0] val_ireq_tkeep ,

- input [31:0] val_ireq_tuser ,

-

- output val_treq_tvalid,

- input val_treq_tready,

- output val_treq_tlast,

- output [63:0] val_treq_tdata, //从DSP接收来的数据

- output [7:0] val_treq_tkeep,

- output [31:0] val_treq_tuser,

-

- output port_initialized,

- output link_initialized

- /*********************************************/

-

- );

可以看到,以上程序也给了一些注释,本程序是为了FPGA与DSP进行数据交互的而设计的,如果两块FPGA之间进行数据的传输同样可以采用SRIO。

对于FPGA给DSP发送的数据来讲,那信号名称就是ireq,总共6个信号,是从 srio_request_gen_srio_gen2_0模块引出来的,简单来说就是把srio_request_gen_srio_gen2_0模块的这6个信号,连接到咱们自己产生的发送模块里面。当然这6个信号是符合AXI协议的,简而言之,就是vld和rdy信号握手,此时数据有效。

类似的,对于FPGA来说,DSP给FPGA发送的数据就是treq,总共6个信号,连接到咱们自己产生的接收模块里面。同样也符合AXI协议,这6个信号是从 srio_response_gen_srio_gen2_0模块引出来的。其实大家应该也发现了,request就是请求,对应数据发送,response是应答,对应数据接收。

最后,对于port_initialized表示端口已初始化。此信号反映物理层配置中端口n错误和状态CSR中端口未初始化位的值。而link_initialized表示链接已初始化。具体地,已经发送了至少15个状态控制符号,并且已经接收了8个无差错的状态控制符号。这两个信号是从support模块引出来的,实际上我们使用的时候,会把这两个信号相与,作为初始化成功的信号。

以上就是对Example_top模块的端口说明,接下来给出顶层的例化部分程序,发送和接收部分是根据自己的逻辑,用状态机实现的,程序比较长,就不在这里给出了。顶层的例化部分程序如下:

- //********************************************SRIO*******************************************

- (*mark_debug = "true"*)wire ireq_tvalid;

- (*mark_debug = "true"*)wire ireq_tready;

- (*mark_debug = "true"*)wire ireq_tlast;

- (*mark_debug = "true"*)wire [63:0] ireq_tdata;

- (*mark_debug = "true"*)wire [7:0] ireq_tkeep;

- (*mark_debug = "true"*)wire [31:0] ireq_tuser;

- (*mark_debug = "true"*)wire treq_tvalid;

- (*mark_debug = "true"*)wire treq_tready;

- (*mark_debug = "true"*)wire treq_tlast;

- (*mark_debug = "true"*)wire [63:0] treq_tdata;

- (*mark_debug = "true"*)wire [7:0] treq_tkeep;

- (*mark_debug = "true"*)wire [31:0] treq_tuser;

- wire port_initialized;

- wire link_initialized;

-

- srio_example_top_srio_gen2_0 #(

- .SIM_VERBOSE (0), // If set, generates unsynthesizable reporting

- .VALIDATION_FEATURES (1), // If set, uses internal instruction sequences for hw and sim test

- .QUICK_STARTUP (1), // If set, quick-launch configuration access is contained here

- .STATISTICS_GATHERING (1), // If set, I/O can be rerouted to the maint port [0,1]

- .C_LINK_WIDTH (4)

- )

- srio_example(

- //Clocks and Resets

- .sys_clkp (srio_clkp ),

- .sys_clkn (srio_clkn ),

- .sys_rst (rst ),

- .log_clk (log_clk_out ),

- //high-speed IO

- .srio_rxn0 (srio_rxn0 ),

- .srio_rxp0 (srio_rxp0 ),

- .srio_rxn1 (srio_rxn1 ),

- .srio_rxp1 (srio_rxp1 ),

- .srio_rxn2 (srio_rxn2 ),

- .srio_rxp2 (srio_rxp2 ),

- .srio_rxn3 (srio_rxn3 ),

- .srio_rxp3 (srio_rxp3 ),

-

- .srio_txn0 (srio_txn0 ),

- .srio_txp0 (srio_txp0 ),

- .srio_txn1 (srio_txn1 ),

- .srio_txp1 (srio_txp1 ),

- .srio_txn2 (srio_txn2 ),

- .srio_txp2 (srio_txp2 ),

- .srio_txn3 (srio_txn3 ),

- .srio_txp3 (srio_txp3 ),

-

- //User_interface

- .val_ireq_tvalid (ireq_tvalid ),

- .val_ireq_tready (ireq_tready ),

- .val_ireq_tlast (ireq_tlast ),

- .val_ireq_tdata (ireq_tdata ), //ĺé?çťDSPçć°ć?

- .val_ireq_tkeep (ireq_tkeep ),

- .val_ireq_tuser (ireq_tuser ),

-

- .val_treq_tvalid (treq_tvalid ),

- .val_treq_tready (treq_tready ),

- .val_treq_tlast (treq_tlast ),

- .val_treq_tdata (treq_tdata ), //äťDSPćĽćśćĽçć°ćŽ

- .val_treq_tkeep (treq_tkeep ),

- .val_treq_tuser (treq_tuser ),

-

- .port_initialized (port_initialized ),

- .link_initialized (link_initialized )

- );

-

- //******************************************SRIOĺć°*****************************************

- wire SRIO_initialized;

- assign SRIO_initialized = port_initialized & link_initialized;

-

- Transmit_data Transmit_data_inst(

- .log_clk (log_clk_out ),

- .rst (rst ),

-

- .trans_begin (1'b1 ),

- .SRIO_initialized (SRIO_initialized ),

- .time_delay_error_3r (time_delay_error_3r ),

- .phase_delay_error_3r (phase_delay_error_3r ),

- .velocity_error_3r (velocity_error_3r ),

- .angle_error_3r (angle_error_3r ),

- .yuanCPI_num_3r (yuanCPI_num_3r ),

- .zhongCPI_num_3r (zhongCPI_num_3r ),

- .jinCPI_num_3r (jinCPI_num_3r ),

-

- .yuanCPI_PRT_num_3r (yuanCPI_PRT_num_3r ),

- .zhongCPI_PRT_num_3r (zhongCPI_PRT_num_3r ),

- .jinCPI_PRT_num_3r (jinCPI_PRT_num_3r ),

- .yuan_event_num_before_fifo_rst (yuan_event_num_before_fifo_rst),

- .yuan_event_num_all_cpi (yuan_event_num_all_cpi),

- .zhong_event_num_before_fifo_rst (zhong_event_num_before_fifo_rst),

- .zhong_event_num_all_cpi (zhong_event_num_all_cpi),

- .jin_event_num_before_fifo_rst (jin_event_num_before_fifo_rst),

- .jin_event_num_all_cpi (jin_event_num_all_cpi),

- .ref_unit_num_3r (ref_unit_num_3r ),

- .protect_unit_num_3r (protect_unit_num_3r ),

- .detect_factor_3r (detect_factor_3r ),

- .distance_win_num_3r (distance_win_num_3r ),

- .doppler_win_num_3r (doppler_win_num_3r ),

- .master_sla_dyt_3r (master_sla_dyt_3r ),

- //ä¸ĺ¤é¨FIFOćĽĺŁ

- .pakage_data_in (pakage_data_in ),

- .package_fifo_pfull (package_fifo_pfull ),

- .rd_package_fifo (rd_package_fifo ),

-

- .event_num_before_db (event_num_before_db ),

-

- .ireq_tvalid (ireq_tvalid ),

- .ireq_tready (ireq_tready ),

- .ireq_tlast (ireq_tlast ),

- .ireq_tdata (ireq_tdata ),

- .ireq_tkeep (ireq_tkeep ),

- .ireq_tuser (ireq_tuser )

- );

-

- //******************************************SRIOćść°*****************************************

- Receive_data Receive_data_inst(

- .log_clk (log_clk_out ),

- .read_clk (log_clk_out ),

- .rst (rst ),

- // .restart (restart_2r ),

-

- .treq_tvalid (treq_tvalid ),

- .treq_tready (treq_tready ),

- .treq_tlast (treq_tlast ),

- .treq_tdata (treq_tdata ),

- .treq_tkeep (treq_tkeep ),

- .treq_tuser (treq_tuser ),

-

- .srio_rxdata_out (srio_rxdata_out ),

- .jiaodu_data (jiaodu_data ),

- .jiaodu_vld (jiaodu_vld ),

- .srio_rxdata_valid (srio_rxdata_valid )

- );

这样一来,我们就把自己的顶层,发送模块,接收模块,以及Example_top模块连接到一起了,然后根据自己需要传输的数据来编写发送和接收模块的代码即可,当然,如果还是有一些问题也欢迎讨论,大家一起交流学习。

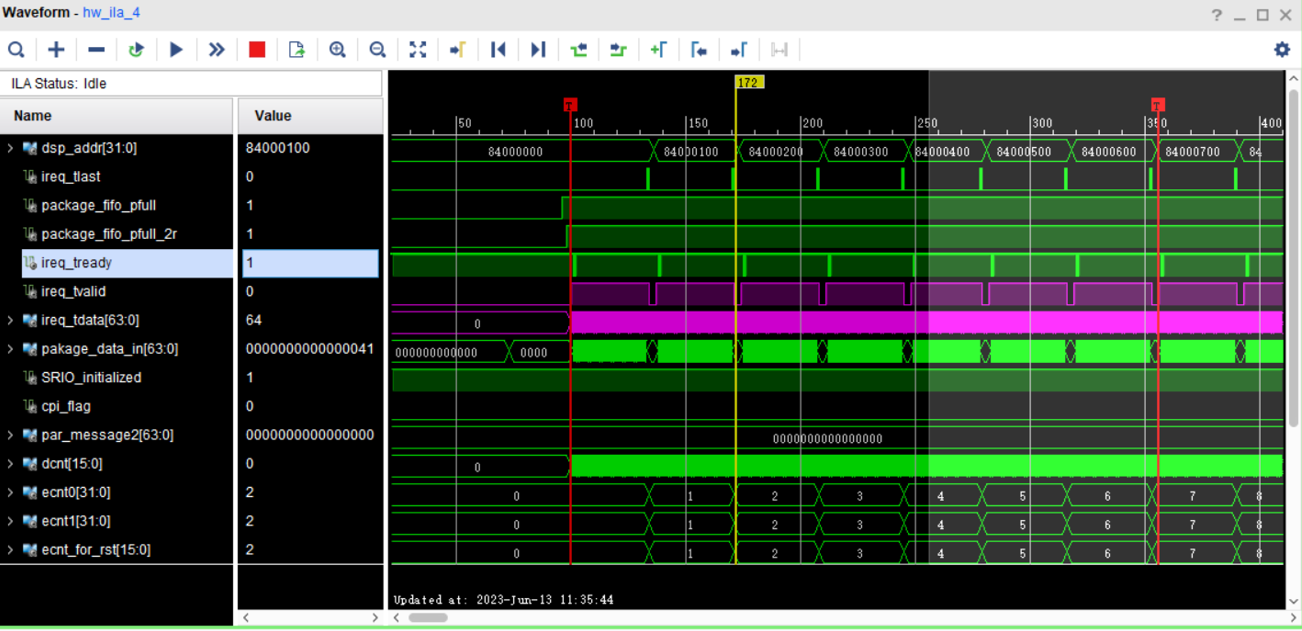

上板验证:SRIO IP配置的是4x,3.125Gbps,通过之前的介绍,我们知道log_clk_out的时钟周期是6.4ns,在这里也可以和大家分享一个小技巧,如果大家不确定自己算的时钟频率是否正确,那可以直接打开官方的例程,直接Run simulation即可,只是需要等待时间长一点,这样就能看到当前配置下的时钟频率具体是多少了。

本次程序采用的是递增数来进行测试,从一块FPGA的光口,发到另外一块FPGA的光口,一包数据是256字节,正好是一包最大的数据传输量,对应32个64bit。总共发了500包,由于ila深度不够,我这里只给出开头部分的截图,下面给出测试结果:

SRIO数据发送

SRIO数据接收