- 1【mysql本地服务器搭建】_搭建本地mysql

- 2【源码分享】机器视觉驱动的1-10数字手势智能识别系统_智能手势识别系统

- 3思岚机器人移动底盘传感器位置坐标及底盘配置工具的使用说明

- 4SpringCloud(微服务)详细解说_springcloud的讲义

- 5招聘申请登记需求工具包 (8份工具)

- 6Vivado2021.2与Modelsim20.4关联成功(Qesta/Matlab类似)_vivado2022关联modelsim

- 7flask中数据表(历史版本&升级,降级指定具体版本)_flask-wtf降版本

- 83060显卡下CUDA+CUDNN+Paddle安装的血泪史_3060 cuda

- 9【安路FPGA】从流水灯入门安路开发环境_做单片机的学安路fpga

- 10CDH安装hive报错:Failed to Create Hive Metastore Database Tables.

【verilog】多功能数字钟的设计_多功能数字钟 verilog

赞

踩

实验目的

- 掌握数字钟的工作原理。

- 掌握计数器级联构成更大模值计数器的方法。

- 能用verilog描述简单的时序逻辑电路。

实验原理

多功能数字钟应该具有的基本功能有:显示时-分-秒、整点报时、小时和分钟可调等。首先要知道钟表的工作机理,整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,但是需要注意的是,小时的范围是从0~23时。

在实验中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD码)显示个位,对于小时因为它的范围是从0~23,所以可以用一个2位的二进制码显示十位,用4位二进制码(BCD码)显示个位。

实验中由于七段数码管是动态扫描的方式显示,虽然时钟需要的是1Hz时钟信号,但是扫描却需要一个频率比较高的时钟信号。因此,可以输入一个高频的时钟信号(系统板上的10KHz时钟信号或者核心板上的50M时钟信号),并通过分频得到准确的1Hz时钟信号。

对于整点报时功能,根据系统的硬件结构自由发挥来设计。可以设计为当进行整点的倒计时5秒时,让LED来闪烁进行整点报时的提示。也可以使用led点阵来显示整点报时。或者让数码管闪烁来进行整点报时。

实验内容

本实验的任务就是设计一个多功能数字钟,要求显示格式为“小时-分钟-秒钟”,整点报时,报时时间为5秒,即从整点前5秒钟开始进行报时提示,LED、LED点阵或者数码管开始闪烁,过整点后,停止闪烁。时钟选择系统板时钟模块的10KHz或者核心板的50MHz时钟信号。要得到1Hz时钟信号,必须对系统时钟进行104次或者5*107次分频。调整时间的的按键用按键模块的S1和S2,S1调节小时,每按下一次,小时增加一个小时,S2调整分钟,每按下一次,分钟增加一分钟。另外用S12按键作为系统时钟复位,复位后全部显示00-00-00。

实验箱中用到的数字时钟模块、按键开关、LED、数码管与FPGA的接口电路,以及数字时钟源、按键开关、LED、数码管与FPGA的管脚连接可参考数字逻辑EDA实验箱《CVT-SOPC-IV用户手册》。

设计思路

把电路分成时间计数器模块、数码管显示模块和状态机控制器模块。状态机控制器模块根据按键输入和时间计数器是否差5秒整点,从正常计时状态转换到调整时间状态或者整点报时状态,并发出对应的控制信号,完成调整时间计数器计数值或者整点报时的功能。数码管显示模块用于显示当前时间或者调整时间,可使用实验三中设计完成的模块。时间计数器由秒、分、时三个计数器级联构成,对1Hz的时钟进行计数,分别产生秒、分、时的计数值。

实验过程

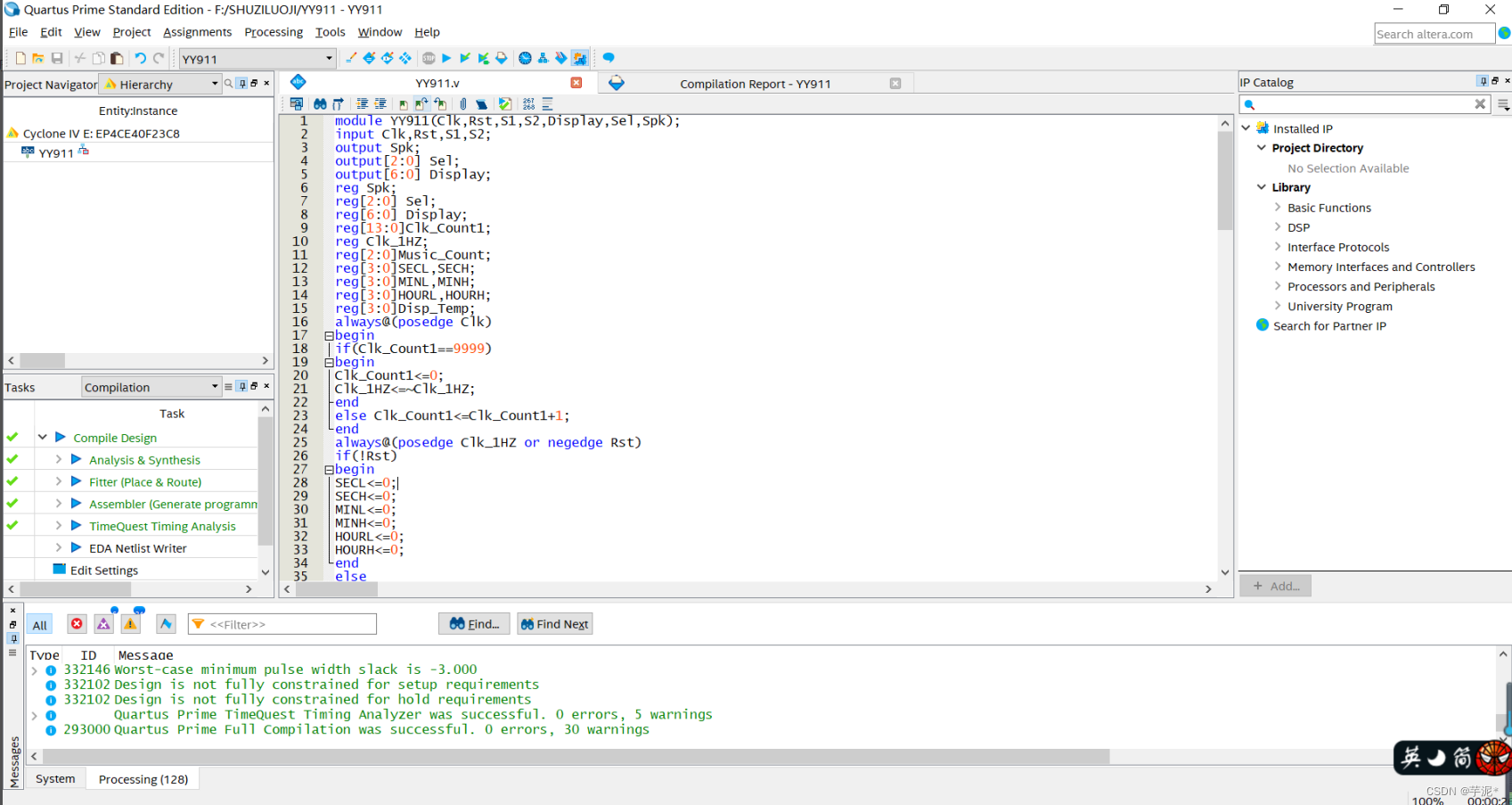

- 打开QUARTUSII软件,新建一个工程。

- 建完工程之后,再新建一个verilog File,打开verilog编辑器对话框。

- 按照实验原理和自己的想法,在verilog编辑窗口编写verilog程序,用户可参照光盘中提供的示例程序。

- 编写完verilog程序后,保存起来。方法同实验一。

- 对自己编写的verilog程序进行编译并仿真,对程序的错误进行修改,直到完全通过编译和仿真。

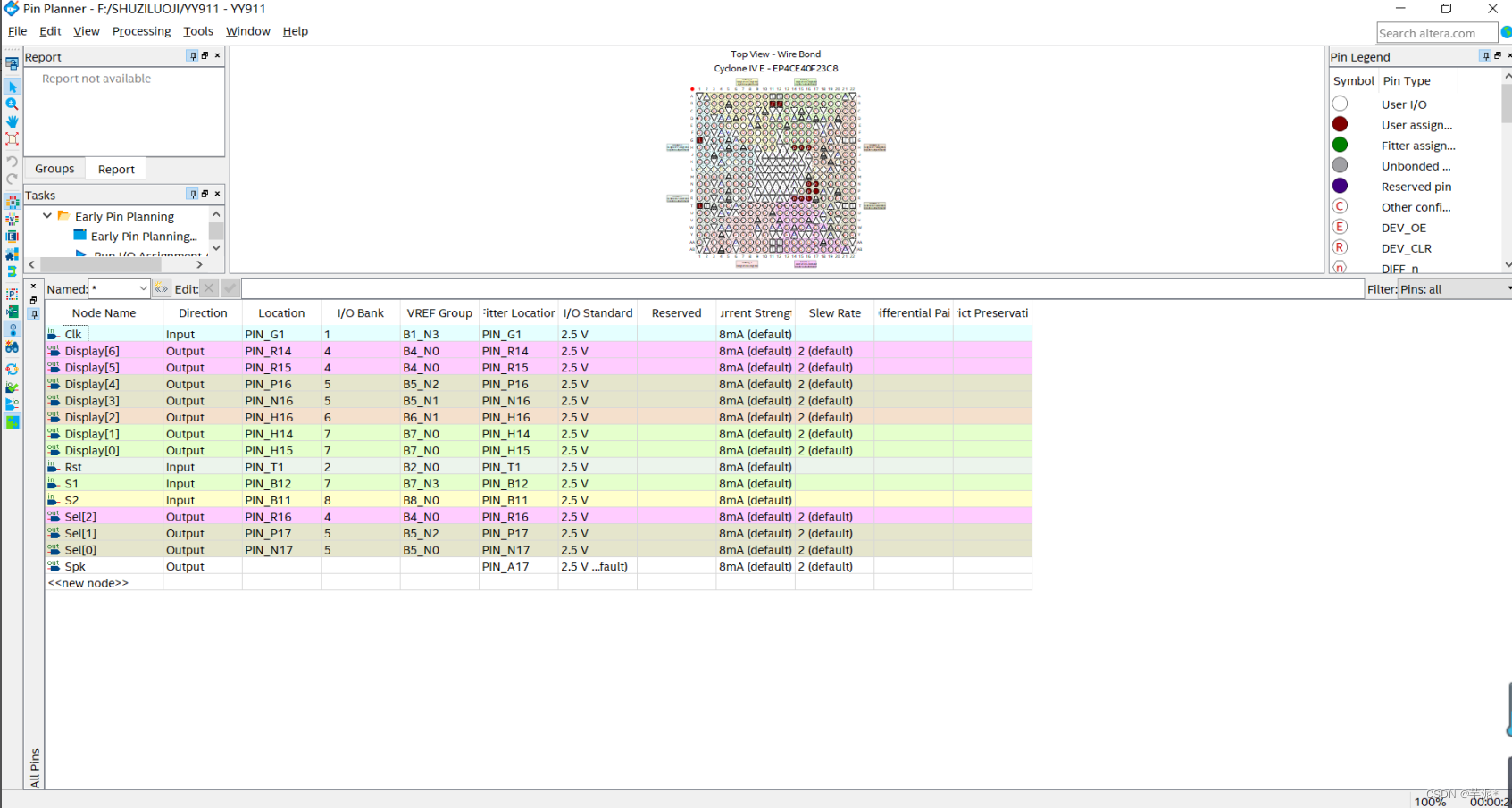

- 编译仿真无误后,依照按键开关、数码管、LED灯与FPGA的管脚连接表或参照附录进行管脚分配。表4-1是示例程序的管脚分配表。分配完成后,再进行全编译一次,以使管脚分配生效。

-

用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。观察实验结果是否与自己的编程思想一致。

管脚分配

| 端口名 | 使用模块信号 | 对应FPGA管脚 | 说 明 |

| CLK | 系统板时钟或 核心板时钟 | Pin_K7或Pin_G1 | 时钟为10KHZ 或50MHz |

| S1 | 按键开关S1 | Pin_B12 | 调整小时 |

| S2 | 按键开关S2 | Pin_B11 | 调整分钟 |

| RESET | 按键开关S12 | Pin_T1 | 复位 |

| LED0 | LED灯模块LED1 | Pin_V10 | 整点倒计时 |

| LED1 | LED灯模块LED2 | Pin_W8 | |

| LED2 | LED灯模块LED3 | Pin_W10 | |

| LED3 | LED灯模块LED4 | Pin_Y10 | |

| DISPLAY0 | 数码管A段 | Pin_H15 | 时间显示 |

| DISPLAY 1 | 数码管B段 | Pin_H14 | |

| DISPLAY 2 | 数码管C段 | Pin_H16 | |

| DISPLAY 3 | 数码管D段 | Pin_N16 | |

| DISPLAY 4 | 数码管E段 | Pin_P16 | |

| DISPLAY 5 | 数码管F段 | Pin_R15 | |

| DISPLAY 6 | 数码管G段 | Pin_R14 | |

| DISPLAY7 | 数码管DP段 | Pin_T13 | |

| SEG-SEL0 | 位选DEL0 | Pin_N17 | |

| SEG-SEL1 | 位选DEL1 | Pin_P17 | |

| SEG-SEL2 | 位选DEL2 | Pin_R16 |

Verilog代码

- module YY911(Clk,Rst,S1,S2,Display,Sel,Spk);

- input Clk,Rst,S1,S2;

- output Spk;

- output[2:0] Sel;

- output[6:0] Display;

- reg Spk;

- reg[2:0] Sel;

- reg[6:0] Display;

- reg[13:0]Clk_Count1;

- reg Clk_1HZ;

- reg[2:0]Music_Count;

- reg[3:0]SECL,SECH;

- reg[3:0]MINL,MINH;

- reg[3:0]HOURL,HOURH;

- reg[3:0]Disp_Temp;

- always@(posedge Clk)

- begin

- if(Clk_Count1==9999)

- begin

- Clk_Count1<=0;

- Clk_1HZ<=~Clk_1HZ;

- end

- else

- Clk_Count1<=Clk_Count1+1;

- end

-

- always@(posedge Clk_1HZ or negedge Rst)

- if(!Rst)

- begin

- SECL<=0;

- SECH<=0;

- MINL<=0;

- MINH<=0;

- HOURL<=0;

- HOURH<=0;

- end

- else

- begin

- if(!S1)

- begin

- if(HOURL==9)

- begin

- HOURL<=0;

- HOURH<=HOURH+1;

- end

- else

- begin

- if(HOURH==2&&HOURL==3)

- begin

- HOURL<=0;

- HOURH<=0;

- end

- else

- HOURL<=HOURL+1;

- end

- end

- else if(!S2)

- begin

- if(MINL==9)

- begin

- MINL<=0;

- if(MINH==5)MINH<=0;

- else MINH<=MINH+1;

- end

- else MINL<=MINL+1;

- end

- else if(SECL==9)

- begin

- SECL<=0;

- if(SECH==5)

- begin

- SECH<=0;

- if(MINL==9)

- begin

- MINL<=0;

- if(MINH==5)

- begin

- MINH<=0;

- if(HOURL==9)

- begin

- HOURL<=0;

- HOURH<=HOURH+1;

- end

- else if(HOURH==2&&HOURL==3)

- begin

- HOURL<=0;

- HOURH<=0;

- end

- else HOURL<=HOURL+1;

- end

- else MINH<=MINH+1;

- end

- else MINL<=MINL+1;

- end

- else SECH<=SECH+1;

- end

- else SECL<=SECL+1;

- end

-

- always@(posedge Clk)

- begin

- Music_Count<=Music_Count+1;

- Sel<=Sel+1;

- if(MINH==5&&MINL==9&&SECH==5)

- begin

- if((SECL%2)==0)

- Spk<=Music_Count[2];

- else Spk<=0;

- end

- else if(MINH==0&&MINL==0&&SECH==0&&SECL==0)

- Spk<=Music_Count[1];

- else Spk<=0;

- end

-

- always@(Sel)

- begin

- case(Sel)

- 3'b000:Disp_Temp=HOURH;

- 3'b001:Disp_Temp=HOURH;

- 3'b010:Disp_Temp=4'b1010;

- 3'b011:Disp_Temp=MINH;

- 3'b100:Disp_Temp=MINL;

- 3'b101:Disp_Temp=4'b1010;

- 3'b110:Disp_Temp=SECH;

- 3'b111:Disp_Temp=SECL;

- endcase

- end

-

- always@(Disp_Temp)

- begin

- case(Disp_Temp)

- 4'b0000:Display=7'b0111111;

- 4'b0001:Display=7'b0000110;

- 4'b0010:Display=7'b1011011;

- 4'b0011:Display=7'b1001111;

- 4'b0100:Display=7'b1100110;

- 4'b0101:Display=7'b1101101;

- 4'b0110:Display=7'b0111101;

- 4'b0111:Display=7'b0000111;

- 4'b1000:Display=7'b1111111;

- 4'b1001:Display=7'b1101111;

- 4'b1010:Display=7'b1000000;

- default:Display=7'b0000000;

- endcase

- end

- endmodule

仿真结果

源码获取

实验总结

在做本次实验的过程中,我们了解了数码管的工作原理,掌握了计数器级联构成更大模值计数器的方法。虽然能够实现基本的功能,但是一开始的编译一直不能成功,后来请教同学,终于把正确的Verilog代码改了出来,这个过程是艰辛的,也是充满成就感的,在以后的学习过程中我们更应该注重平时的练习,巩固知识,这样才能将这种硬件课程学习的更好。实验太难,一个人太难完成,得依靠团队的力量来完成。