热门标签

热门文章

- 1Sunny-Ngrok实现内网穿透(免费域名)flask实现

- 2探索学术世界:学术页面(Academic Pages)深度解析

- 3第3章 开源大模型框架概览3.2 PyTorch与Hugging Face3.2.3 PyTorch在大模型中的应用_huggingface和pytorch的区别

- 4linux python安装opencv-python失败的解决办法 ERROR: Could not build wheels for opencv-python which use PEP 517_linux pip install opencv-python没反应

- 5聚类方法:DBSCAN算法研究(1)--DBSCAN原理、流程、参数设置、优缺点以及算法_dbscan聚类算法

- 6线上线下包搭建小程序/公众号/H5 支持二开!

- 7生活中常见的分辨率_常见分辨率

- 8java 千帆大模型 流式返回_大模型的流式输出 java怎么做

- 9shell脚本部署apache_666mpm

- 10Linux(Centos 7)环境下安装wget,并且更换阿里云镜像_centos7 离线安装wget

当前位置: article > 正文

山东大学计算机组成与设计实验六 二进制补码加法器实验_山东大学二进制补码加法器实验

作者:菜鸟追梦旅行 | 2024-05-19 01:31:59

赞

踩

山东大学二进制补码加法器实验

山东大学计算机组成与设计实验六 二进制补码加法器实验,

山东大学计算机组成与设计实验,

山东大学计算机组成与设计实验报告,

计算机组成原理实验报告,

山东大学计算机组成原理实验报告

实验6 二进制补码加法器实验

一、实验目的:

根据补码加法器的模型,理解数据流及其时序关系。

掌握加法器实现补码加、减运算的基本原理。

二、实验方案:

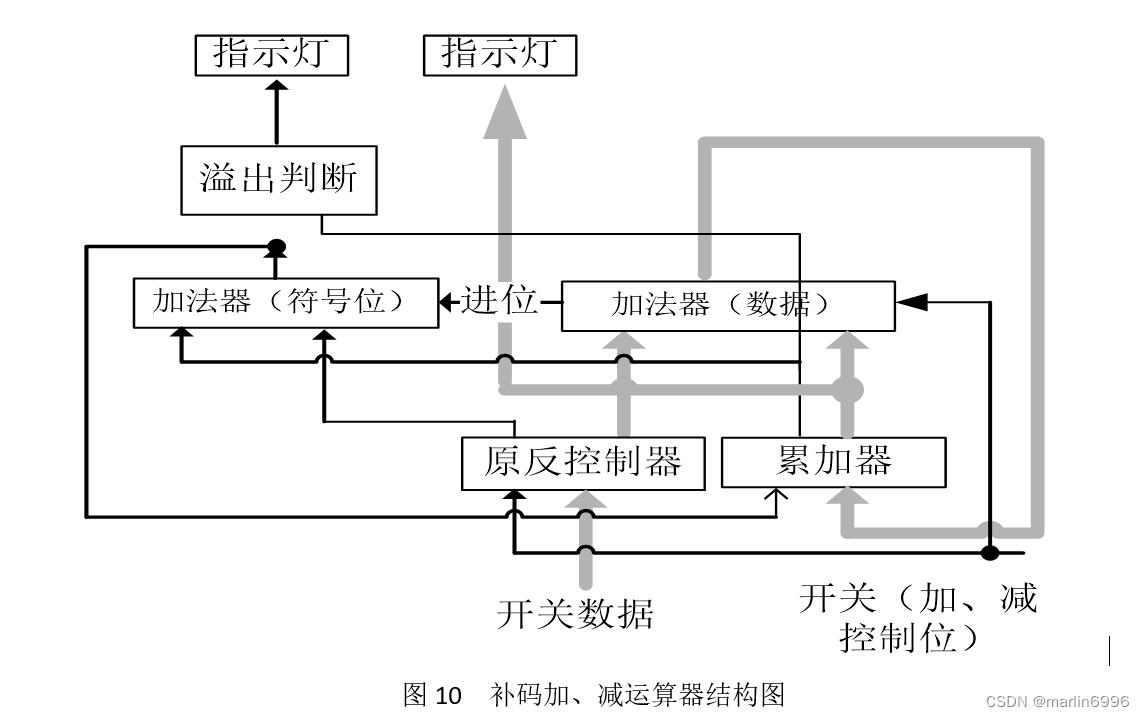

本实验运算器模型,可分为数据运算以及符号位的产生两部分。

- 1

三、实验要求:

◆ 数据宽度为4位,设计出实验线路图。

◆ 设计试验步骤。

◆ 使用开关进行数据加载,完成补码加、减运算。

◆ 符号位运算采用双符号位,累加器应有清零控制。

◆ 通过指示灯观察运算结果,记录实验现象,写出实验报告。

四、参考器件:

累加器选用一片74LS273;加法器用两片74 LS283;原、反码控制器用一片74LS86.

溢出判断用一片74LS86。

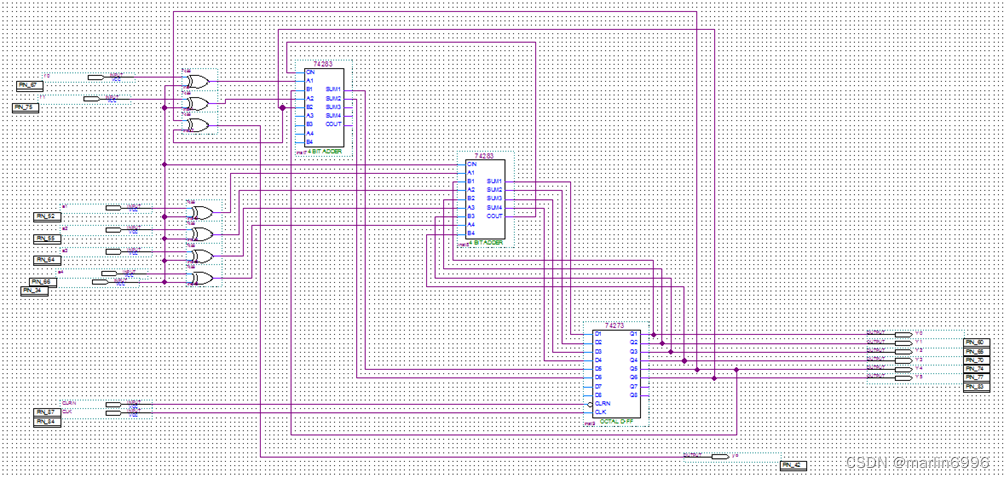

(1)原理图:

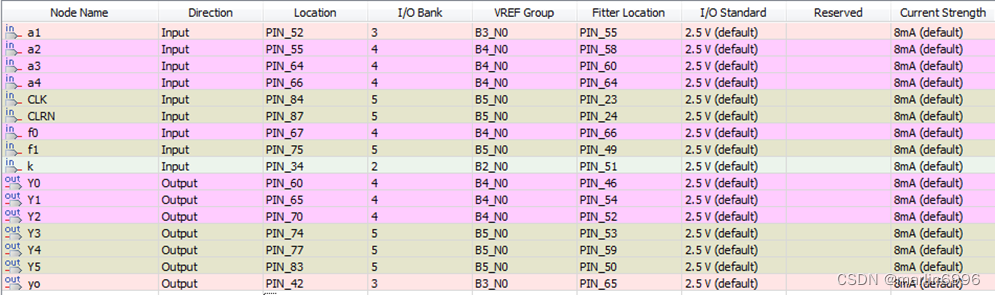

(2)管脚锁定:

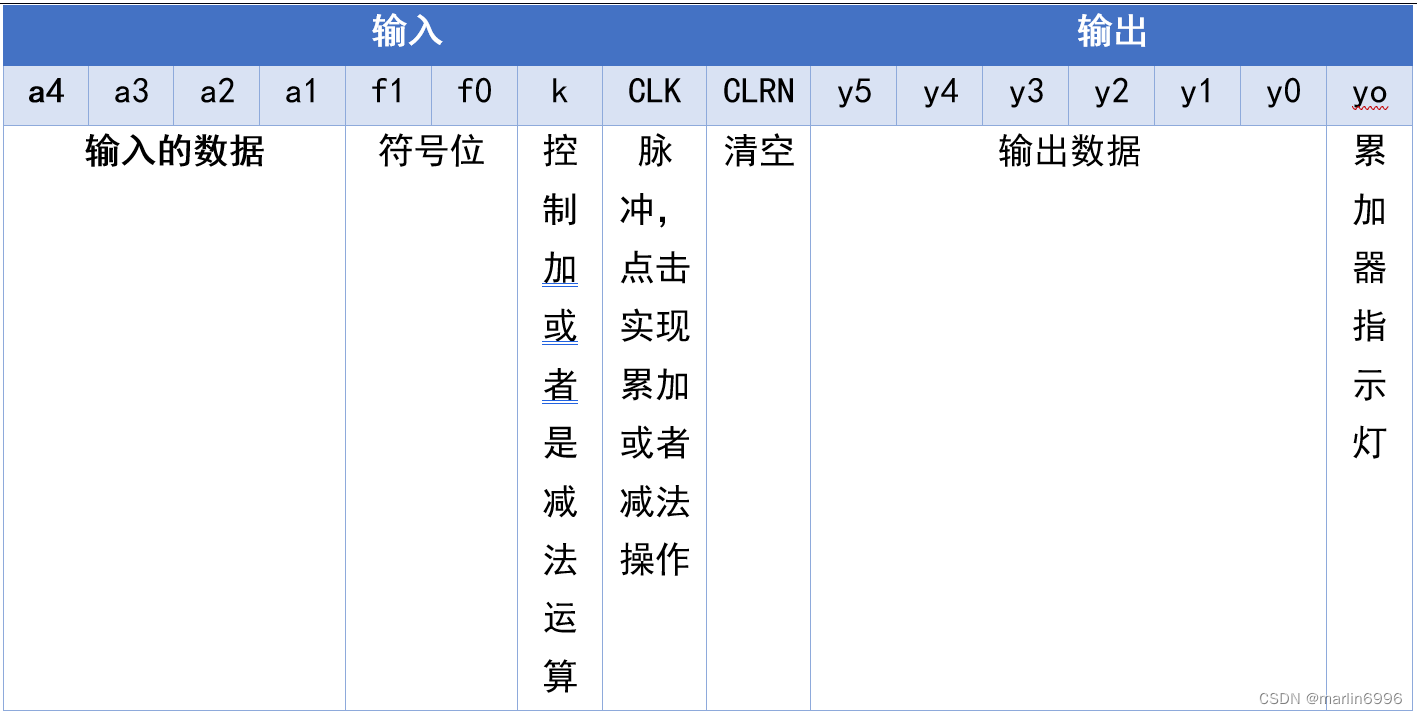

选择实验台工作模式5,键1~4输入四位数据,键5、键6输入的是符号位,键7是控制加减(低电平减,高电平加),键8是(clock)产生时钟脉冲,即进行对累加器进行加/减操作。红色拨码开关是控制清除(重置)。输出是输出六位数据,高两位为符号位。

实验结果:

加法:

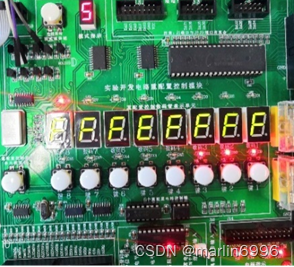

1)输入数字7(下方),并存入累加器

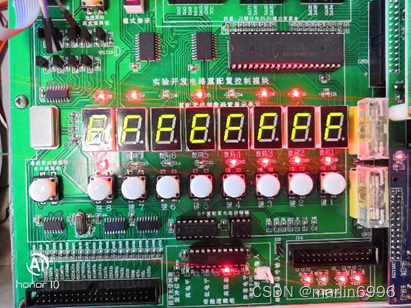

2)输入数字15(下方),与前面的数字求和结果为上方数据

减法:

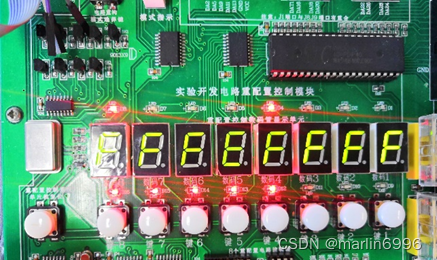

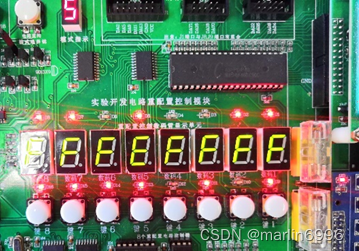

输入-8(原码)和-5(原码)做减法,输出-3(原码)(内为补码操作)

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/590785

推荐阅读

相关标签