- 1复杂任务也不怕!上海AI Lab提出增强型LLM框架—ControlLLM,大模型可操控多模态工具

- 2Advanced RAG 05:探讨基于文本内在语义信息的数据分块方法_semanticchunker

- 3Nginx限制上传(下载)大小限制_nginx文件上传下载大小限制配置

- 4模型训练中,不调用gpu比调用gpu更快的情况_使用gpu和cpu进行训练神经网络时间对比

- 5ShowMeBug x 红杉 | 创业公司怎么做好技术招聘?

- 6WEB/UI自动化实战--从入门到实战,保姆级教程Step1--环境部署_webui自动化环境搭建

- 7Android TextView加中划线/下划线_textview中划线

- 8springcloud-config.git: Auth fail_springcloud 使用github 作为配置中心,报错 auth fail

- 9【Rust】——使用消息在线程之间传递数据

- 10Effective Java 78条军规_a value class is simply a class that represents a

IC开发——verdi基本用法_verdi的exclude

赞

踩

1. 基础知识

1.1. verdi

VCS和Verdi这两个工具,这两个工具目前都属于synopsys公司。VCS主要负责编译运行Testbench和RTL,并负责生成相应的波形文件。而verdi主要负责加载波形文件,查看信号的波形及其对应的代码来进行调试验证。Verdi最开始是由novas公司设计的,在2008年,被台湾的EDA厂家springsoft(源笙)收购了。在2012年,synopsys收购了spring soft公司,所以此时Verdi才正式属于synopsys。

Verdi®自动调试平台是一种用于调试数字电路设计的高级解决方案,可用于提高复杂的片上系统(SoC),ASIC和FPGA设计效率。传统的调试工具仅依靠结构信息和发挥工程师的个人能力从结构中推断出设计行为。 Verdi平台提供强大的技术,帮助工程师理解复杂和不熟悉的设计行为,自动化困难和繁琐的调试过程,统一各种复杂的设计环境,并推断设计的动态行为。

除了源代码浏览器的标准功能,原理图,波形,状态机图和波形比较(用于比较FSDB格式的仿真结果),Verdi平台还包括使用时间流视图自动跟踪信号活动的高级功能,基于断言的调试,功耗感知调试以及事务和消息数据的调试和分析。所有这些都可以在图形用户界面中使用,该平台使用支持多窗口对接的Qt平台,并且可以轻松定制。

Verdi平台使工程师能够在传统解决方案的一小部分时间内定位,理解和解决错误。这可以最大限度地提高昂贵工程师资源的效率,显着降低成本,并大大加快将硅片推向市场的过程。

1.2. FSDB文件

fsdb文件是verdi使用一种专用的数据格式,类似于VCD,但是它是只提出了仿真过程中信号的有用信息,除去了VCD中信息冗余,就像对 VCD数据进行了一次huffman编码。因此fsdb数据量小,而且会提高仿真速度。我们知道VCD文件使用verilog内置的系统函数来实现 的,fsdb是通过verilog的PLI接口来实现的。$fsdbDumpfile,$fsdbDumpvars等 另外,在VCS仿真器中还有一种VCD+的数据格式VPD,详细情况参照VCS的使用。 注意:WIF:波形中间格式;WLF:波形日志文件。由于在ModelSim下只能打开WLF文件 使用ModelSim行命令vcd2wlf 将VCD文件转化为WLF文件。

2. 分析引擎

- 结构分析:分析设计结构以显示组件的连接方式

- 行为分析:分析设计和仿真结果,以显示设计的行为

- 断言评估:从之前的仿真中搜索有关设计操作的详细信息

- 事务/消息分析:分析FSDB文件中的事务和消息(日志)数据,并在nWave和电子表格视图中可视化

- 功耗状态评估:根据UPF中的功耗意图描述以及FSDB文件中相关信号的值评估功耗状态

3. 可视化

Verdi平台以时间流视图的形式提供无与伦比的时间可视化功能。这一革命性的工具从设计数据和仿真结果中提取并显示多周期时间行为。

此外,Verdi平台还包括最先进的结构可视化和分析工具:nTrace用于源代码,nWave用于波形,nSchema用于原理图/逻辑图,nState用于有限状态机(FSM)。这些工具专注于以RTL中的信号关系,原理图/逻辑图中的物理连接,FSM气泡图中的状态和转换以及波形中的值变化的形式分析设计结构。

Verdi平台中的Property Tools窗口为断言提供集中支持,并允许从断言失败到相关设计活动的快速遍历。而事务/消息分析器可以在保存到FSDB文件的事务或日志信息的更高抽象级别上启用调试和分析。 Power Manager窗口提供电源意图的可视化,并支持与其他Verdi平台窗口的交叉探测。

4. 波形

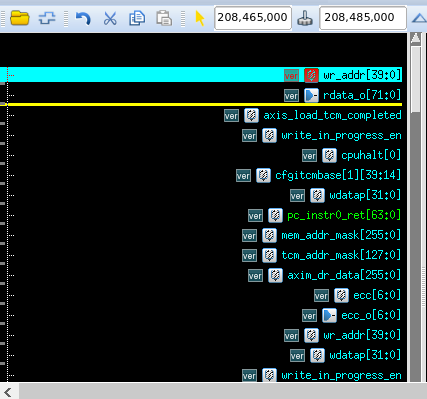

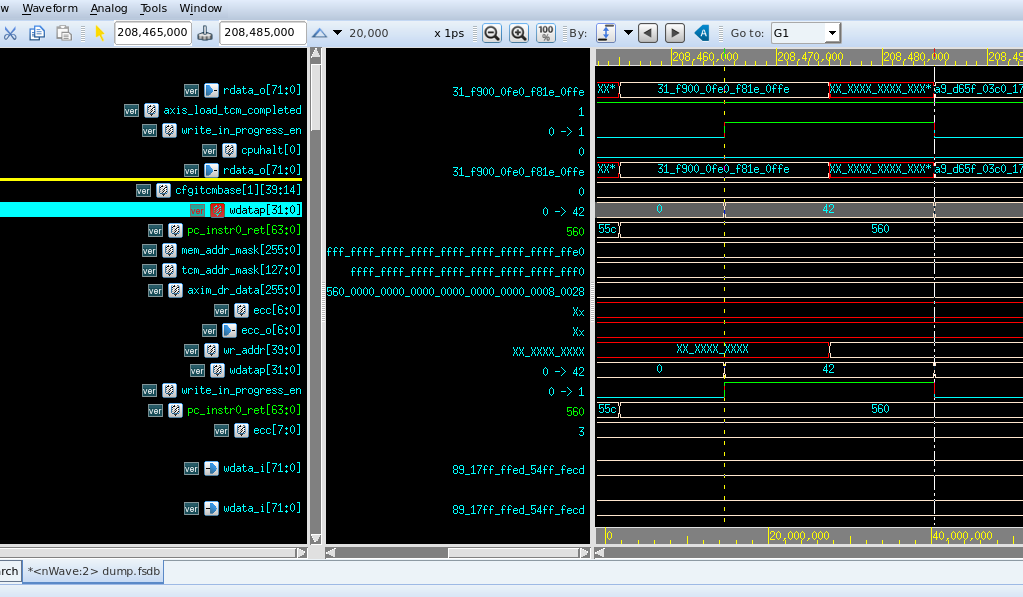

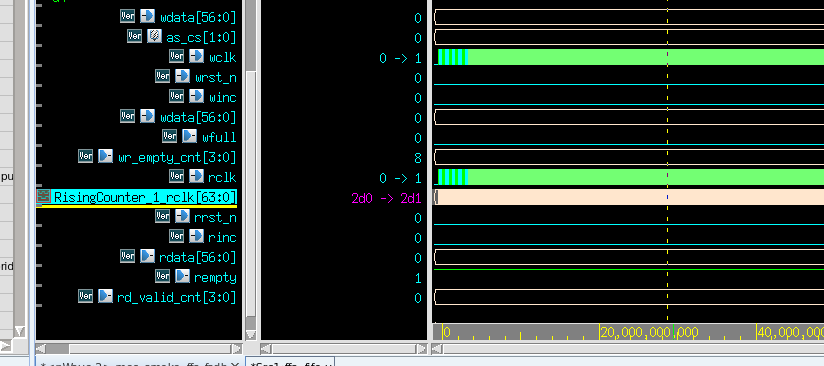

- 信号窗口:如果需要拖动信号改变显示顺序,需要点击鼠标中键即滚轮选中需要拖动的信号,如下图所示,而黄色光标表示信号拖动后所处位置;改变黄色光标的位置也需要通过点击鼠标中键来完成,配合剪切、复制和粘贴信号等操作。还可以分组信号,添加空白等来排列信号。信号可以显示完成路径或短路径,可以通过View菜单中的hierarchical name来切换,也可以通过快捷键H。

- 波形窗口:在波形窗口中最主要的是光标和标记的操作,可以由三个键的组合操作就能完成所有工作。

- 通过鼠标左键控制光标的位置;

- 通过鼠标中键控制标记的位置;

- 通过鼠标右键放大光标和标记间区域的波形至整个波形窗口。

在移动光标和标记时,要注意一个选项Waveform->Snap Cursor To Transitions,在使能该选项时,光标和标记始终处于信号波形变化边沿,如1-bit信号的上升沿或者下降沿;在不使能该选项时,光标和标记可以在信号波形任意位置。

nWave 的波形窗口中默认有一个Cursor (黄色)和一个Marker (白色),左键是Cursor,中键是Marker,在波形窗口中右键是放大Cursor 和Marker 之间波形的快捷键。默认情况下Cursor 和Marker 都是停留在信号的Transition 处,你可以通过点击Wave->Snap Cursor To Transitions 关闭或者启动这个功能。

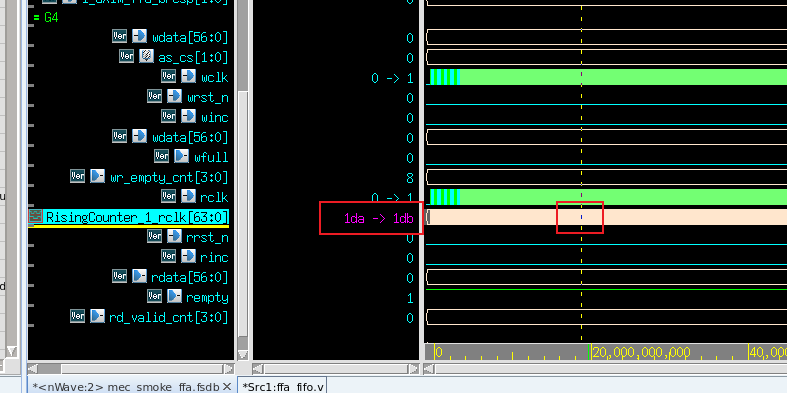

通过Cursor 和Maker 来计算Delta 时间是很难估算出两个信号(或者是信号的边沿)之间的周期数的,你可以选中信号的驱动时钟,通过添加网格线的方法来实现周期数的计算。View-> Grid on Rising Edge,这样子网格线就会出现在每个周期中,View->Grid Count 来显示从Cursor 到每个网格线的网格个数。

- 常用快捷键

-

- g:加载信号 Get signals

- x:标注信号的值(在源代码中)Active Annotation

- L :返回至上一个视图 Reload Design

- Ctrl+e: Active Trace

- Ctrl+w: Add Signal to Wave

- H: hierarchical Name

- Z: Zoom In

- z: Zoom Out

- f: Zoom All

- l: Last View

5. 调试

5.1. 载入设计文件及波形

- UI启动:启动verdi,载入设计文件(.f文件),然后new waveform来打开波形窗口。在波形窗口打开波形文件(fsdb文件),然后通过Git Signal窗口或者代码窗口添加需要观察的信号。添加好需要观察的信号之后,可以保存相关信号为.rc文件,下次启动波形文件时,可以直接载入信号文件。当波形有更新时,可以通过Reload来重新加载(也可以快捷方式Shift+L)。

- 命令行启动:

tb.f即为设计文件列表文件;USER_DEFINE添加用户自定义参数进行仿真调试(vcs编译中可能有类似的参数),xxx.fsdb即为波形文件;&表示在控制台后台执行,即不随控制台关闭而关闭;-nologo即不显示启动界面。

verdi -f tb.f -sv +define+USER_DEFINE -ssf XXX.fsdb -nologo &两次回归的simv.vdb一起看覆盖率

- verdi -cov -covdir XXX/simv.vdb -covdir YYY/simv.vdb &

- verdi -cov -covdir XXX/simv.vdb -elfile yyy.el

el文件可以通过verdi gui界面选定exclude的覆盖项保存

verdi -f filelist.f -dbdir ./simv.daidr -ssf xxx.fsdb -top -sv -nologo5.2. 创建总线分析

创建自己想要的总线信号,如在16bit 的总线中,你只想看到其中的偶数位的总线,或者你想把几条信号合并成一条总线信号,都可以在debussy 中轻松实现。选中要操作的信号或者总线,Signal->Create Bus.

5.3. 载入文件列表文件

如果你所有的design都在一个文件里,比如说verilog文件(扩展名为.v),那么你直接把这个文件加载进去就可以。如果你的design是分布在多个文件里的,那么你可以一次把所有的design都选择上,然后加载。那还有一种方法就是在一个扩展名为.f的文件里把所有的design文件(包括某些IP的库)列出来(可以是绝对路径,也可以是相对路径),然后加载这个.f文件。在上面的操作中,我们实际上就是加载一个包含了所有design文件的run.f文件。

5.4. 查找信号

在代码窗口选中信号,可以用鼠标中键将信号拖到查找框

![]()

,然后进行下一个、上一个的查找。也可以使用快捷键,Ctrl+F选择要查找的信号,Enter、Shift+Enter下一个、上一个查找。

5.5. 查找驱动源

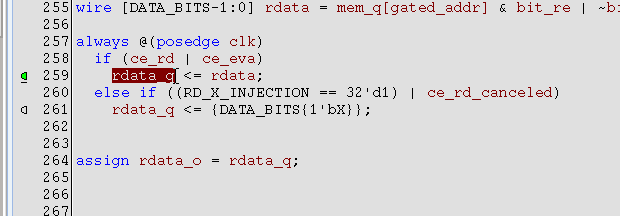

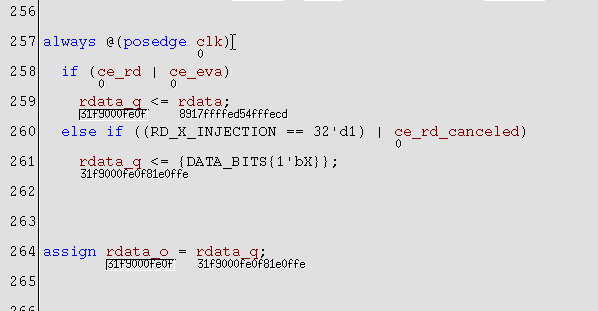

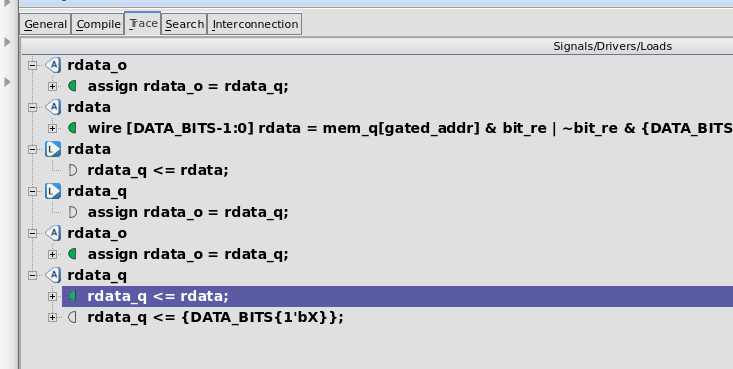

在波形窗口中我们可以通过双击信号的波形来追溯信号的驱动源,从而定位错误出现的位置。在源代码窗口中可以通过双击信号的名字来追溯该信号的驱动源。在源代码窗口中也可以通过右键菜单来实现这个功能。在窗口中选择Trace->Reset Traced Signals’s Color 可以取消追溯过程中带来的信号高亮度的问题。一般情况下我们是从信号的波形图中某一时刻的波形异常处双击该波形,追溯到源代码窗口中的对应赋值语句,从而找到该时刻的驱动源。

Driver即表示当前信号由哪些信号驱动,即由哪些信号赋值;Load即表示当前信号给哪些信号赋值了。在代码窗口选择信号,双击信号即会跳转到赋值语句,如果多处赋值,也会标记,并在Trace窗口显示所有关联信号。

可以通过鼠标右键菜单中的Active Annotation来标记当前信号的值,快捷键x。

可以通过双击找到驱动来源,也可以在工具栏选择D按钮执行相同的功能,L按钮则是找到当前信号给哪些信号赋值了。

5.6. 添加信号

在nTrace(代码)窗口,选中需要观察波形的信号,用鼠标中键拖到nWave窗口,即可以完成信号的添加。也可以选中多个信号用鼠标中键添加相关信号。也可以选中信号,使用鼠标右键菜单Add to waveform,也可以使用快捷键。

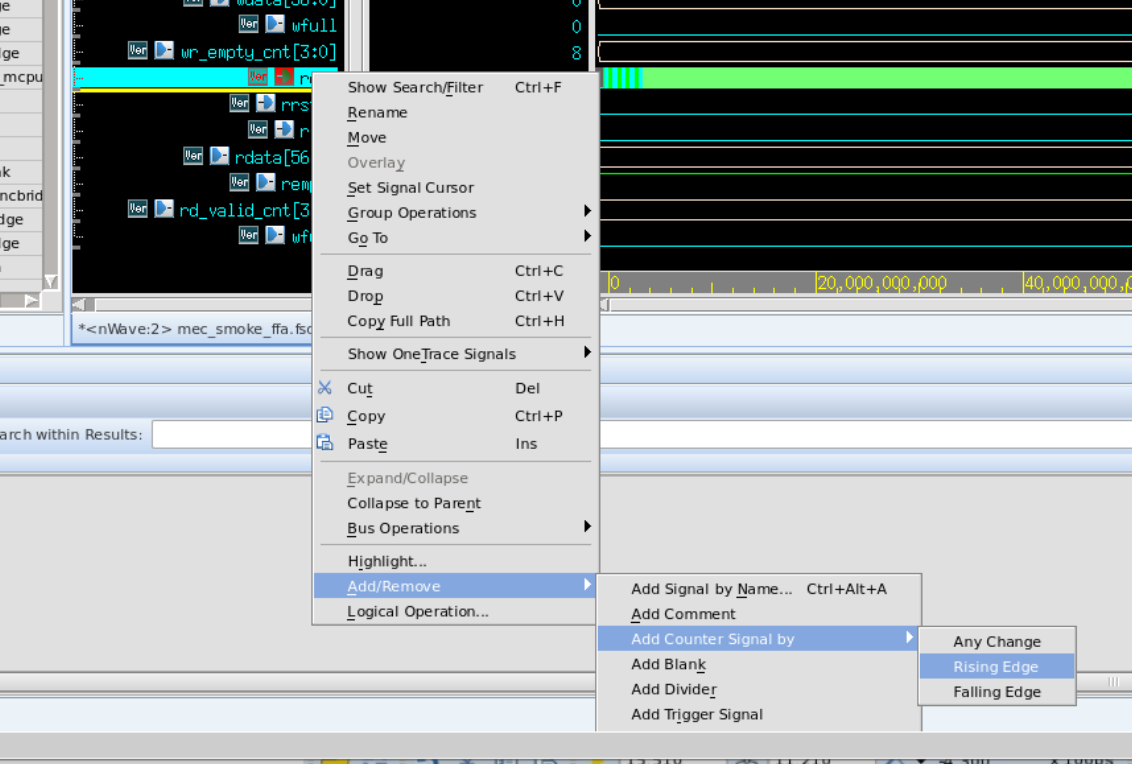

5.7. 统计跳变数量

- 添加跳变信号

2. 光标标记起始位置

3. 光标标记结束位置

4. 计算有效跳变量

有效跳变数=结束光标跳变量-开始光标跳变量

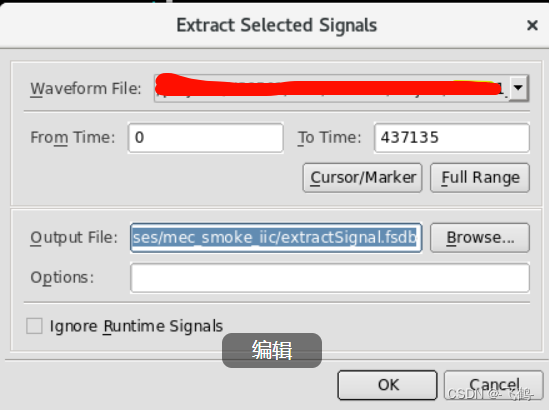

5.8. 提取部分波形文件

波形窗口选择File->Extract Selected Sigals.

通过光标和标记选择起始/结束时间范围的波形进行保存。

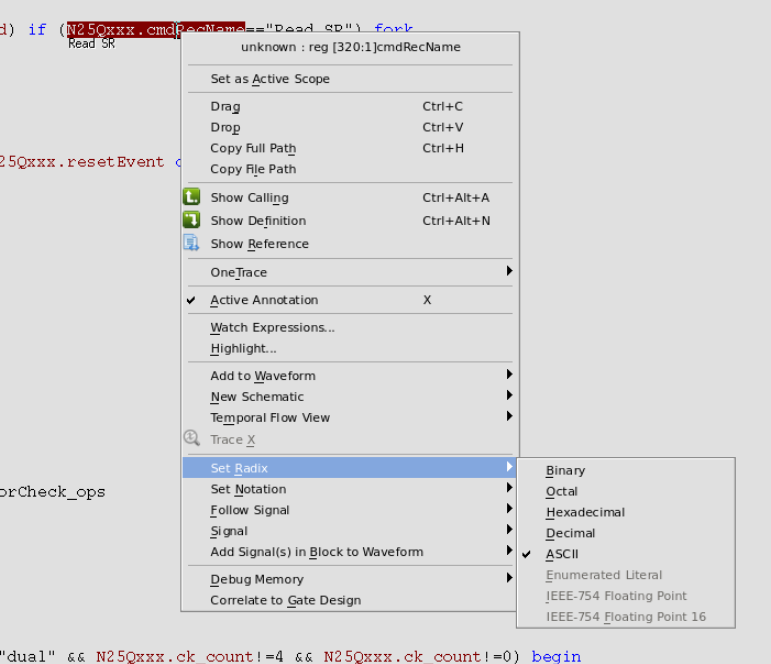

5.9. 设置信号的显式形式

在波形窗口或代码窗口,右键选择相应的信号,在菜单选择 Set Radix,然后选择不同的显示形式。如显示字符串内容ASCII。