- 1清华大学提出IFT对齐算法,打破SFT与RLHF局限性

- 2python按字母顺序排列_在python中检查字符串是否按字母顺序排列

- 3Java基础学习之JVM篇:jstack、jstat和jmap工具使用_jmap、jstack、jstat组合使用定位jvm问题

- 4Git客户端下载、安装

- 5判断一串字符串按字母顺序排列的个数_字符排列判断

- 6Java毕业设计 基于SpringBoot vue智能家居系统

- 7win10_Git基于WSL(Linux子系统)统计代码行数命令_windows查项目行数

- 8安卓在AndroidStudio中集成百度云推送(改良版)_android studio 连接百度智能云

- 9【OCR】OCR前置工作——透视矫正,使用YOLOv8-pose分支在卡证文档图片上进行yolo关键点检测_透视变换应用到yolo检测中

- 10git忽略已提交文件_git 忽略提交out

用Quartus II Timequest Timing Analyzer进行时序分析 :实例讲解 (四)_quatrus clk to output time

赞

踩

设定输入/输出延迟(input/output delay)。首先看输入延迟。

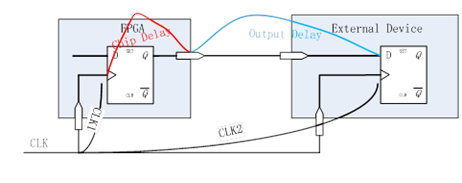

下面图示的系统是我们在做数字电路设计时经常会遇到的。External Device可能是其他的集成电路芯片,也有可能是其他的FPGA,为了与我们所要讨论的FPGA分开,称之为External Device。External Device中的寄存器D1的输出送给FPGA中的寄存器D2。D1和D2属于同一个时钟域(CLK)。为了简化讨论,我们假设CLK source到两个寄存器之间的延时是相等的,也就是说延时CLK1等于延时CLK2。这个时候,D1的CLK端到D2的D端形成了一个完整的timing path。

但是,在我们对FPGA做时序分析的时候,软件只知道FPGA内部的时序信息,对External Device的情况并不清楚。所以我们必须要添加额外的约束来反映FPGA外部的时序信息。一般情况下,我们用input delay来表示输入信号相对于CLK的延迟。即上图我们用红线表示出来的部分。为了便于讨论,我们把FPGA内部蓝色走线的部分称为chip delay。如果我们能给出input delay的大小,那么软件就可以计算出chip delay的大小,从而保证该条timing path符合设计要求。

一般情况下,External Device的spec会给出input delay的大小。我们在做FPGA时序分析的时候,只需要用命令将input delay加入到约束中就可以了。

下面是input delay的语法,详细的介绍可参照Quartus II的帮助系统。

| Syntax | set_input_delay [-h | -help] [-long_help] [-add_delay] -clock <name> [-clock_fall] [-fall] [-max] [-min] [-reference_pin <name>] [-rise] [-source_latency_included] <delay> <targets> |

由于在DAC7512控制器里,并没有需要设定input delay的信号,所以下面给出几个一般的input delay的例子,它们与DAC7512控制器的设计没有关系。

set_input_delay -clock clk 1.5 [all_inputs]

set_input_delay -clock clk -clock_fall 1.5 [get_ports myin*]

在上面的讨论中,我们假定CLK到D1和D2的延时是相等的,但在某些情况下,CLK的延时可能会有差别,那么在定义input delay的时候,就需要考虑CLK延时的差值。具体的计算方式请大家考虑一下,也可以参照TimeQuest文档中的相关部分,这里不再做叙述。

然后看输出延迟。

下图是一个output dleay的例子,和上面讲的input delay相似。在做数字电路设计时也经常会遇到这样的情况。同样的,External Device可能是其他的集成电路芯片,也有可能是其他的FPGA,为了与我们所要讨论的FPGA分开,称之为External Device。图中FPGA的寄存器D1的输出送给External Device的寄存器D2。D1和D2属于同一个时钟域(CLK)。为了简化讨论,我们假设CLK source到两个寄存器之间的延时是相等的,也就是说延时CLK1等于延时CLK2。这个时候,D1的CLK端到D2的D端形成了一个完整的timing path。

同样的,在对FPGA做时序分析的时候,软件只知道FPGA内部的时序信息,对External Device的情况并不清楚。所以我们必须要添加额外的约束来反映FPGA外部的时序信息。一般情况下,我们用output delay来表示输出信号在FPGA外部走线相对于CLK的延迟。即上图我们用蓝线表示出来的部分。为了便于讨论,我们把FPGA内部红色走线的部分称为chip delay。如果我们能给出output delay的大小,那么软件就可以计算出chip delay,从而保证该条timing path符合设计要求。

一般情况下,External Device的spec会给出所需要的output delay的大小。我们在做FPGA时序分析的时候,只需要用命令将output delay加入到约束中就可以了。

下面是output delay的语法,详细的介绍可参照Quartus II的帮助系统。

| Syntax | set_output_delay [-h | -help] [-long_help] [-add_delay] -clock <name> [-clock_fall] [-fall] [-max] [-min] [-reference_pin <name>] [-rise] [-source_latency_included] <delay> <targets> |

也给出两个一般性的例子:

set_output_delay -clock clk 0.5 [all_outputs]

set_output_delay -clock clk -clock_fall 0.5 [get_ports myout*]

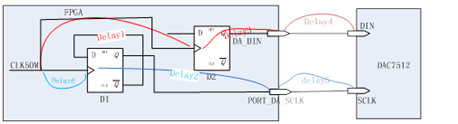

现在我们讨论DAC7512控制器输出信号的output delay,以DA_DIN信号为例。DAC7512控制器的DA_DIN和DA_SCLK与DAC7512的DIN和SCLK按照下面的方式连接。

可以看到D1和D2的时钟是CLK50M。CLK50M到D1和D2的延时分别是Delay1和Delay6。根据FPGA的特性,可以认为Delay1和Delay6是相等的。Delay4和Delay5是两根信号线在PCB上的延时,可以认为二者是相等的。FPGA设计要满足的是D1到DA_SCLK port的延时(Delay2)和D2到DA_DIN port的延时(Delay3)能满足DAC7512 datasheet上对DIN input delay的要求(对于FPGA来讲,就是DA_DIN的output delay)。

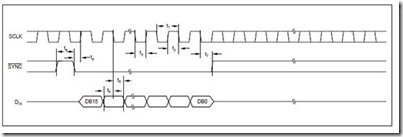

DAC7512的datasheet给出了DAC7512的管脚上DIN和SCLK的时序要求。如下面两张图所示。可以看到以PORT_DA_SCLK为基准,DA_DIN的output delay最大值为(20-4.5),最小值为5。

对我们来讲,Delay2是一个比较难确定的值,但实际上我们可以通过定义以DA_SCLK为源的PORT_DA_SCLK时钟来让软件给我们计算出来Delay2的值。通过下面的命令,创建PORT_DA_SCLK时钟。

create_generated_clock -name PORT_DA_SCLK -divide_by 1 -source [get_registers {DAC7512:DAC7512|DA_SCLK}] [get_ports DA_SCLK]

这样我们就可以用set_output_delay命令定义DA_DIN的output delay。

set_output_delay -clock PORT_DA_SCLK -clock_fall -max 14.5 [get_ports DA_DIN]

set_output_delay -clock PORT_DA_SCLK -clock_fall -min 5 [get_ports DA_DIN]