- 1关于GP2Y1010AU0F SHARP传感器使用_pm2.5粉尘传感器(gp2y1010au0f)与stm32

- 2Hadoop 3.x|第四天|HDFS的Shell操作_从本地剪切到hdfs中

- 3Open-webui GPU版本的安装(ollama,llama3本地部署,docker部署)_国内nvidia gpu 的 open webui镜像下载

- 4情感计算 - 情感模型_分布式情感模型

- 5线程数越多越好吗_为什么说线程太多,cpu切换线程会浪费很多时间?

- 62024年HarmonyOS鸿蒙最全开发者联盟账号注册流程_硬核联盟开发者注册(1),阿里的面试问题_harmony next 开发者账号

- 7小乌龟合并代码、解决冲突

- 8Python实现本地视频/音频播放器_python 视频播放器

- 9关于gitee一次性上传超过100M的建议_gitee最大100m怎么改

- 10windows11删除微软账户,使用本地账户登录_win11本地账号还存在邮箱

数字芯片retention cell

赞

踩

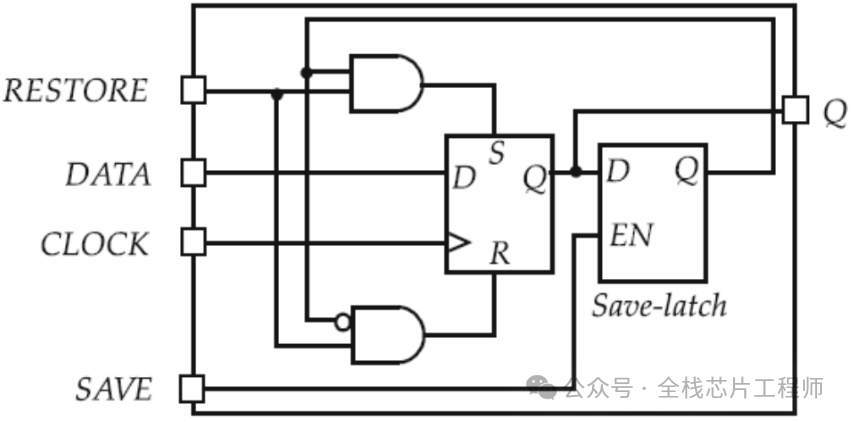

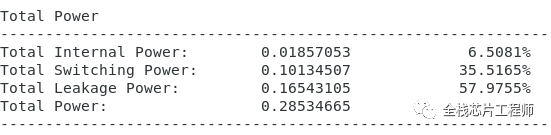

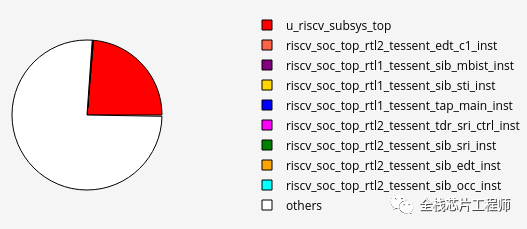

低功耗设计一直是芯片设计的重中之重,景芯SoC训练营采用的低功耗技术有:

1、Clk gating,关掉不工作模块的时钟信号;

2、Power gating,关掉不工作模块的电源;

由于省去了leakage power,Power gating相比较于Clk gating更省电,比如景芯SoC芯片在需要休眠时候,可以关掉CPU、总线等高速模块的电源来降低功耗。

但是CPU、总线等模块重新启动,需要先重新上电,等到电源稳定后,还要再恢复时钟信号,这个过程延时太大将会非常影响客户体验,尤其自动驾驶、工控领域是不能容忍的。

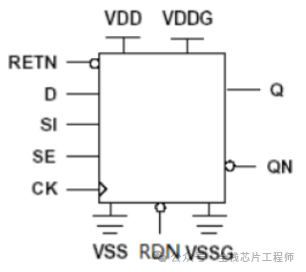

重新上电唤醒太慢怎么办?我们可以用retention cell来保存CPU堆栈等关键寄存器数据不掉电,既满足了上电唤醒速度快的需求,也满足了掉电省功耗的要求。注意,景芯SoC休眠掉电时,将关键数据保存在SRAM,SRAM采用双电源设计,这样设计不仅节省了面积,还降低了设计复杂度。retention cell的电源如下图所示,有VDD/VSS、VDDS/VSSG两组电源。

1)双电源设计

Retention cell能够在Primary电源VDD关闭的情况下保持内部状态,但其实并不是完全断电,还有backup VDDG电源。

2)RETN控制信号

请问,RETN的供电谁来决定?RETN可否断电?

答:RETN是由BUF驱动,且BUF由VDDG VSSG供电,VDD VSS掉电后,RETN需要保持有效,具体由PMU模块设计,景芯SoC提供了PMU设计。注意,景芯SoC是将RETN信号放在power shut power domain的,这样可以尽量避免always on buffer的使用,为何要减少always on buffer的使用,景芯SoC训练营讲过很多了不在赘述。

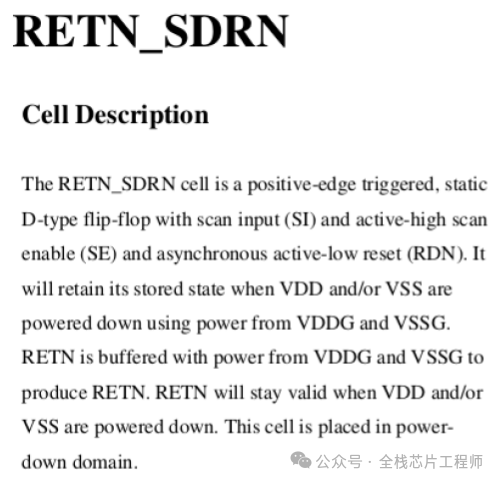

3)Retention cell的主从寄存器

1、主寄存器

Retention flip-flop有一个和普通flip-flop一样的触发器,用以完成正常寄存器功能。

2、从寄存器

Retention cell相比普通寄存器多了一个save-latch,这个save-latch就是从寄存器,其可以在关电的时候保存状态,在重新上电的时候恢复普通flip-flop的状态。

注意,Save-latch一般是一个hvt cell, 以节省静态功耗,且Save-latch是由备用电源VDDG VSSG供电。

正常情况下,Retention flip-flop和普通的flip-flop功能一样,但是会在SAVE信号有效时候将flip-flop输出锁存在Save-latch中,当电源关掉时,由于Save-latch是由backup电源供电,Save-latch能锁存SAVE保存的信号;当RESTORE信号拉成1时,Save-latch会把输出送给前面的flip-flop,就快速恢复下电时的状态,类似网页浏览器关闭了下次直接自动打开,非常丝滑。

请问,Retention cell能大量使用吗?大量使用有什么影响?有好的解决方案吗?景芯SoC的设计方案是否可以消除Retention cell的缺点?欢迎大家在全栈芯片工程师知识星球讨论。

芯片全流程培训

芯片培训即将涨价,报名联系小编微信:13541390811

-

景芯SoC前、中、后端低功耗全流程实战培训(价格不到同行1/6)

-

景芯SoC前端视频+文档+实战+一对一终身辅导实战培训

-

景芯SoC中端视频+文档+实战+一对一终身辅导实战培训

-

景芯SoC后前视频+文档+实战+一对一终身辅导实战培训

-

12nm 2.5GHz A72 低功耗DVFS实战培训(价格不到同行1/3)

-

12nm 2.5GHz A72 DFT实战培训(价格不到同行1/3)

-

RISC-V MCU 40nm全芯片PR实战培训

-

DDR4/3项目实战培训

-

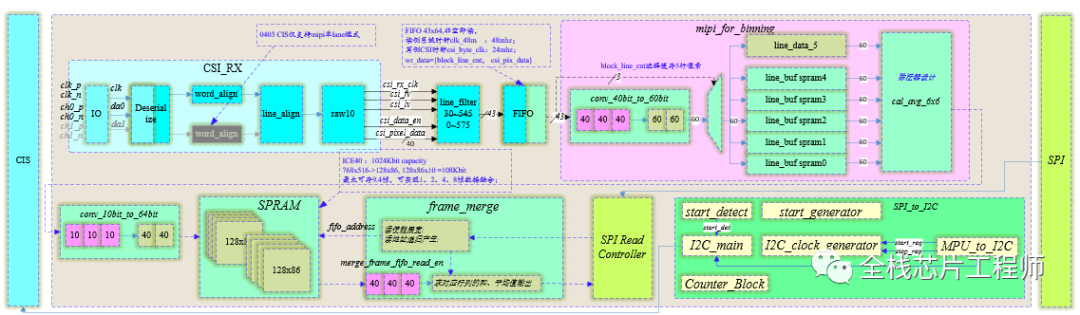

MIPI CSI2 + ISP图像处理 + HDMI实战培训(即景芯SoC前端)

-

MIPI CSI2 + ISP图像处理 + H.265 + USB + MAC实战培训(研发中)

-

进阶Codec H.265/H.264实战培训(研发中)

芯片Design Service设计服务介绍:

-

提供SoC、MCU、ISP、CIS等芯片设计、验证、DFT设计服务

-

提供DDR/PCIE/MIPI/CAN/USB/ETH/QSPI/UART/I2C等IP设计

-

提供7nm、12nm、28nm、40nm、55nm、65nm、90nm等后端设计

-

提供高校、企业定制化芯片设计服务、设计培训业务

另外,小编知识星球分享芯片设计、验证、DFT、后端全流程知识以及大量技术文档,欢迎大家加入讨论学习,共同进步!

景芯SoC芯片全流程设计训练营的宗旨:

【让每个学员都能设计一款SoC/MCU芯片】

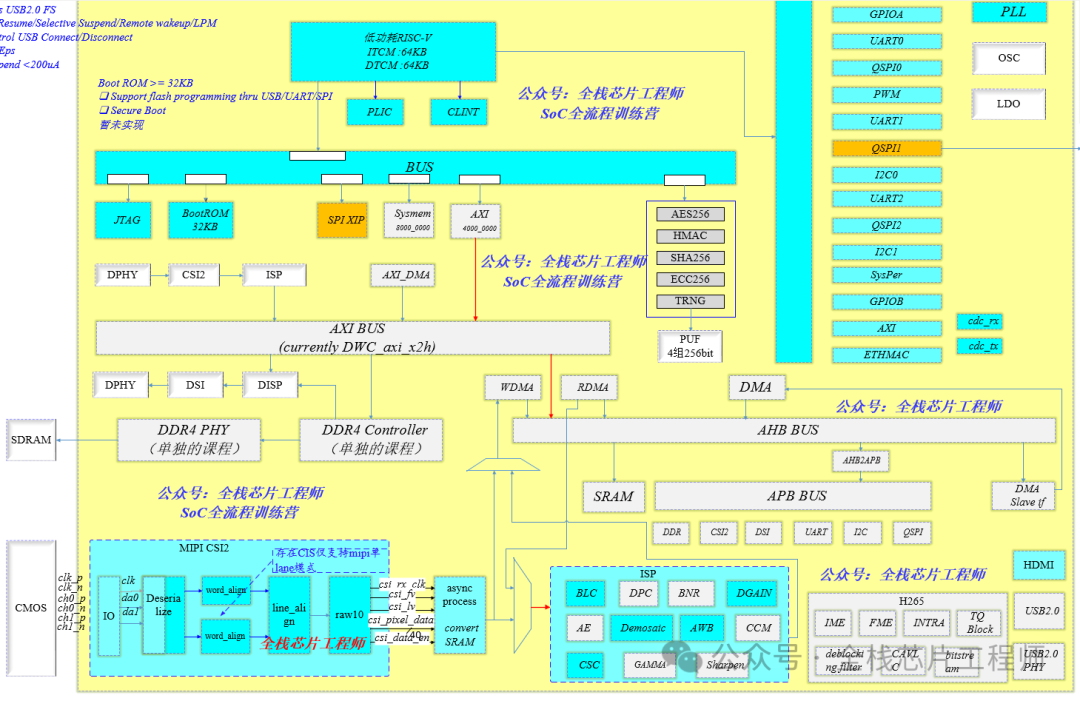

【全网唯一】景芯SoC是一款用于【芯片全流程设计培训】的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。

(一)SoC前端课程,您将学会

-

高速接口的Verilog设计实现

-

从图像算法到RTL设计实现

-

MIPI、ISP的Verilog实现与仿真

-

Lint、CDC检查及UVM验证

-

后仿真

仅前端一门课程内容就抵得上其他培训机构的5-6门课程。

(二)SoC中端课程,您将学会

-

DFT设计(芯片级)

-

Synthesis逻辑综合(芯片级)

-

低功耗UPF设计、CLP技术

-

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程。

(三)SoC后端课程,您将学会

-

低功耗设计

-

布局布线(低功耗FF flow)

-

StarRC/QRC

-

STA/Tempus

-

功耗分析

-

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程。

加入知识星球,加入芯片设计知识宝库!

SoC培训营的知识星球

今天先介绍到这里,然后SoC课程提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。请联系号主报名!联系微信:135-4139-0811

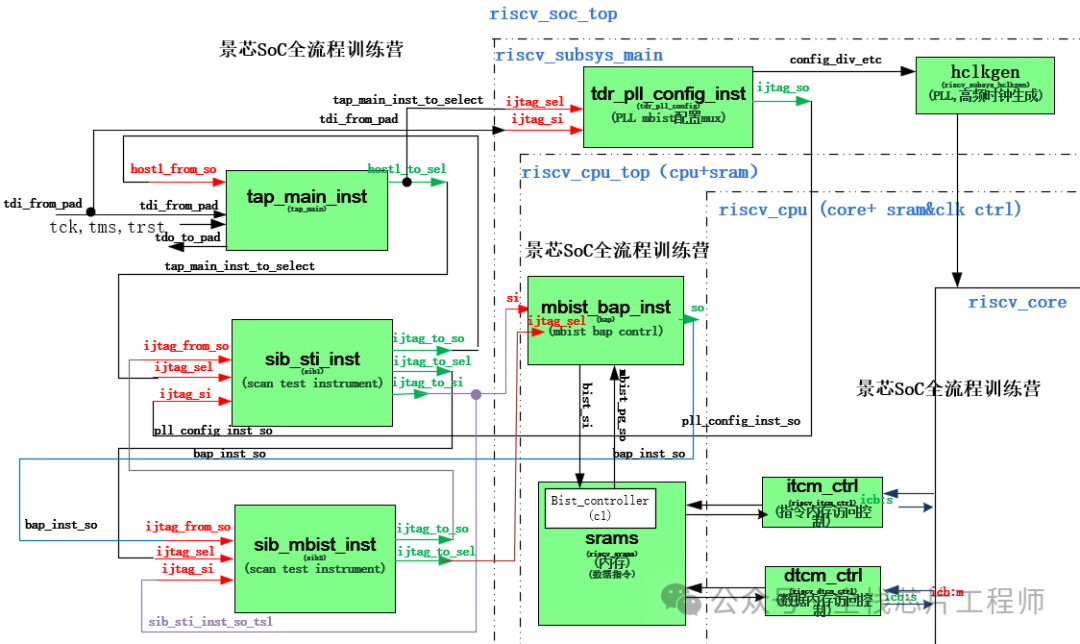

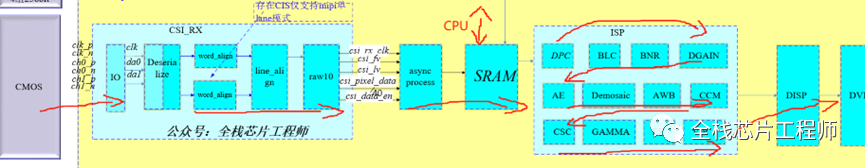

景芯SoC训练营图像处理的数据通路:

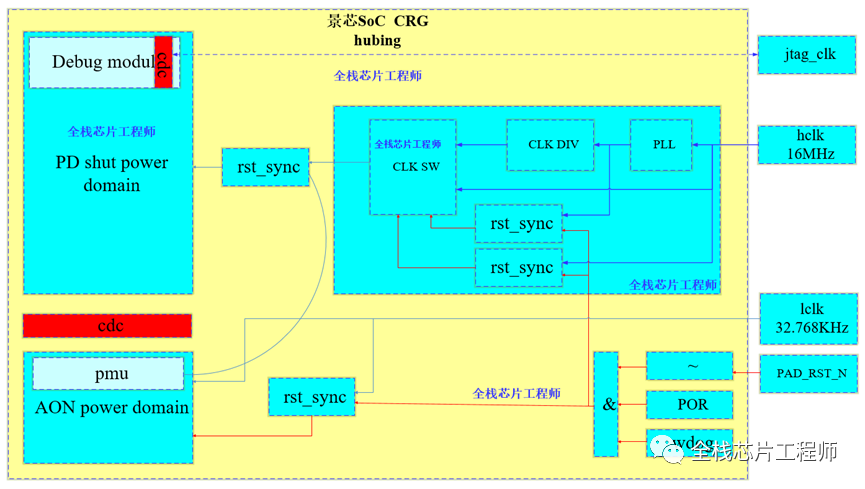

景芯SoC的CRG设计:

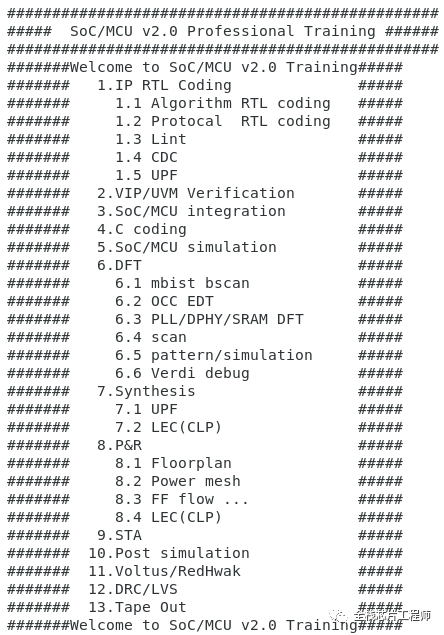

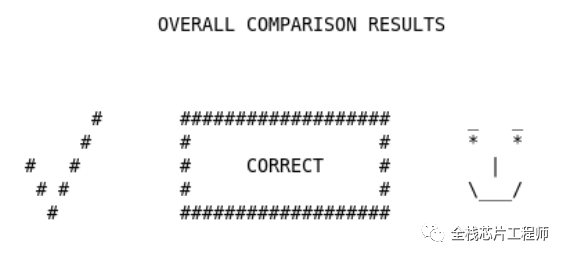

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、STA分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。升级后的芯片设计工程V2.0 flow如下:

SoC一键式执行flow

MIPI DPHY+CSI2解码

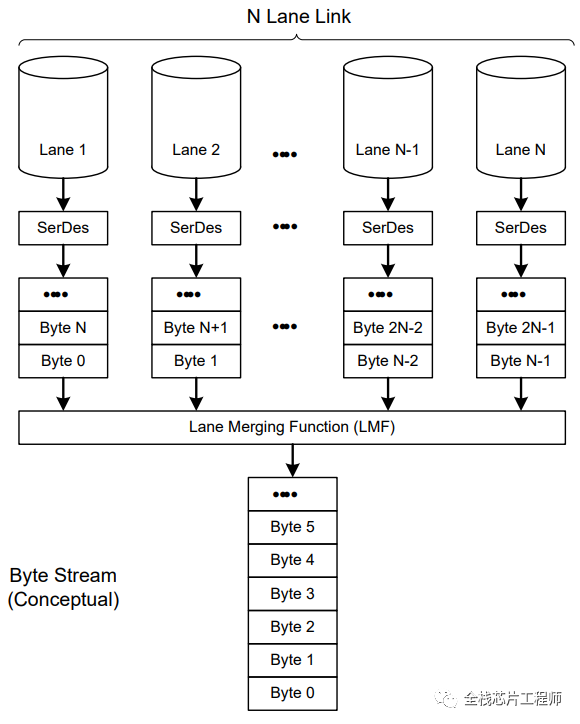

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

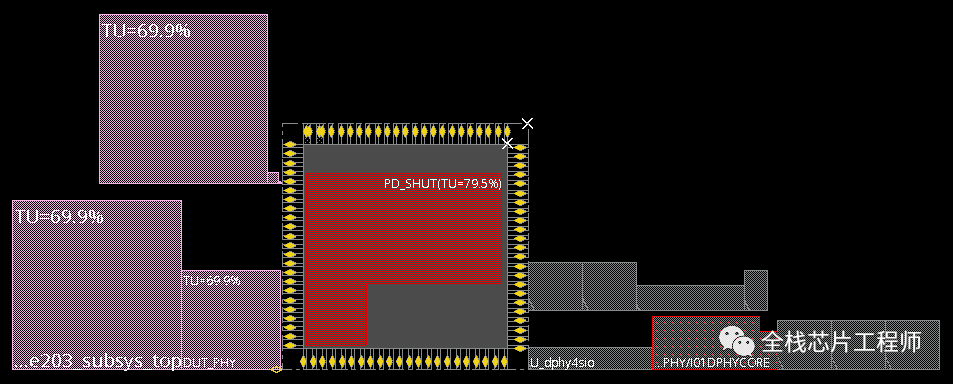

UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

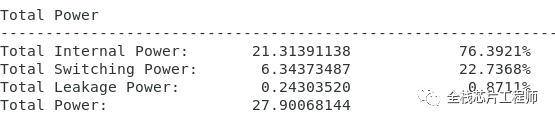

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

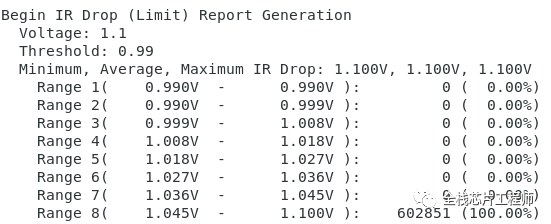

电压降检查:

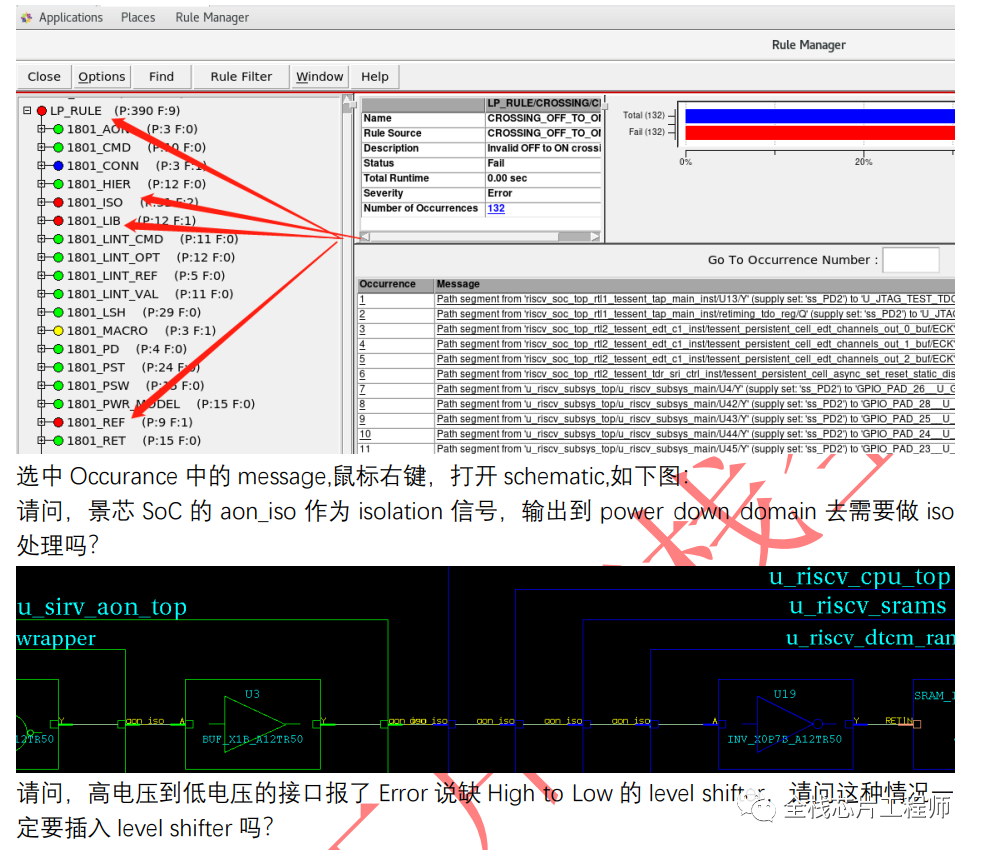

低功耗检查:

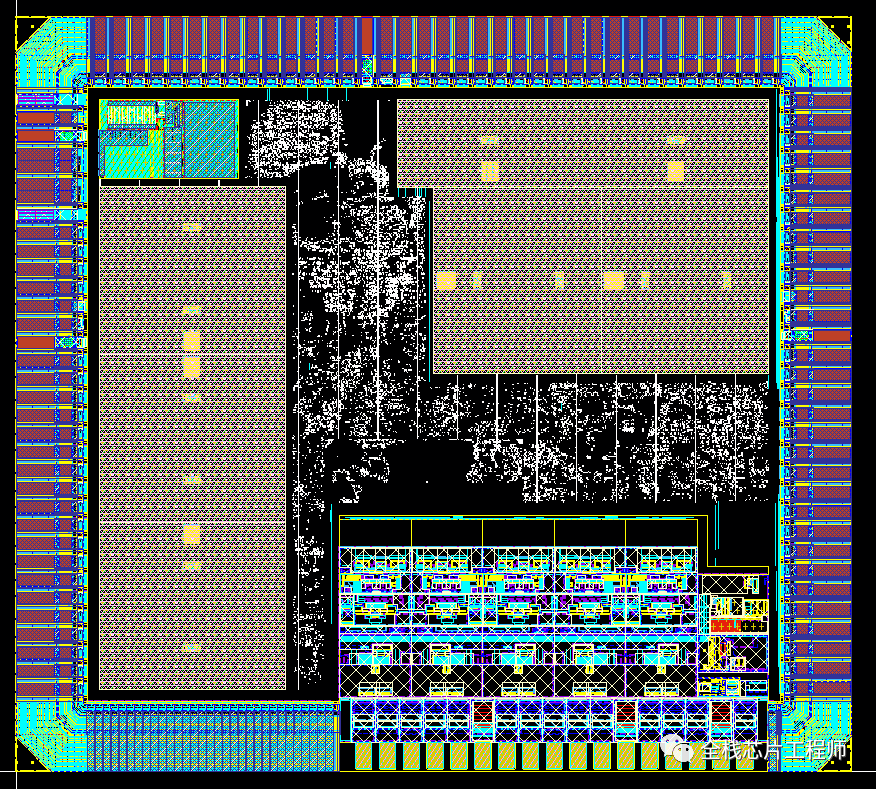

芯片的版图设计V1.0

芯片的版图设计V2.0

低功耗设计的DRC/LVS,芯片顶层的LVS实践价值极高,具有挑战性!业界独一无二的经验分享。

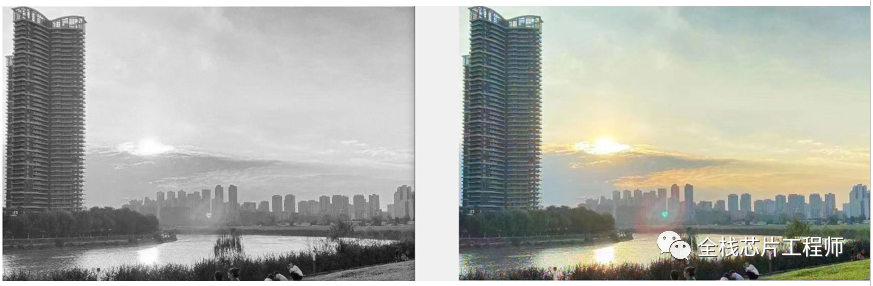

ISP图像处理

-

dpc - 坏点校正

-

blc - 黑电平校正

-

bnr - 拜耳降噪

-

dgain - 数字增益

-

-

demosaic - 去马赛克

-

wb - 白平衡增益

-

ccm - 色彩校正矩阵

-

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

-

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

-

ee - 边缘增强

-

stat_ae - 自动曝光统计

-

stat_awb - 自动白平衡统计

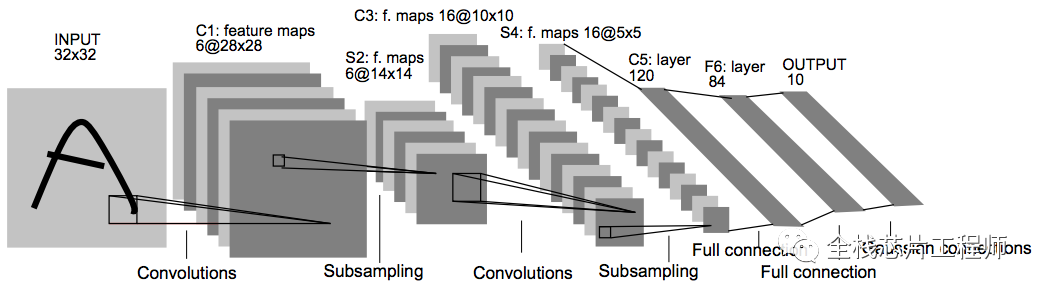

CNN图像识别

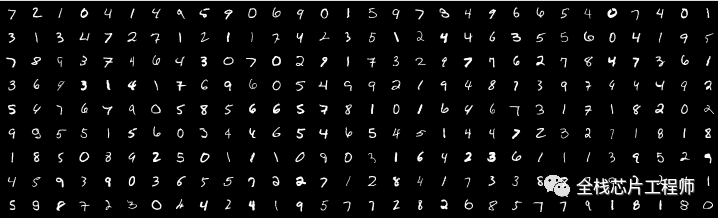

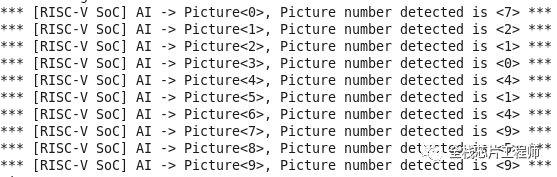

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

景芯微SoC团队业务

景芯微SoC团队业务介绍:

-

提供全网最全流程的实际芯片项目培训

-

提供SoC、MCU、ISP、CIS等芯片设计服务

-

提供芯片设计、验证、DFT设计服务

-

提供后端设计服务,工艺包括7nm、12nm、28nm、40nm、55nm、65nm、90nm、110nm、180nm等,提供投片渠道

-

提供高校、企业定制化芯片设计培训及就业推荐与就业指导