- 1C#中GDI+图形图像技术(Graphics类、Pen类、Brush类)

- 2自定义view的三种方式

- 3深入解析分布式数据库的 SQL 引擎优化_sql引擎

- 4【2024华为OD机试C卷】387、密码输入检测 | 机试真题+思路参考+代码解析(C语言、C++、Java、Py、JS) (最新抽中C卷)(本题100%)_密码输入检测华为od真题

- 5flink启动后web访问问题_flink启动后web页面打不开

- 6【k8s】K8S中的IP地址(Node IP、Pod IP、Cluster IP、External IP、Internal-IP)

- 7docker配置redis主从复制

- 8解决动画函数点击按钮后可能出现的Bug---动画越来越快的问题(方案)_animejs 点击按钮动画加快

- 9Python 微信群聊自动回复_python微信群聊自动回复

- 10(仿牛客社区项目)Java开发笔记8.4:项目总结及常见面试题_仿牛客论坛项目面试题

深圳大学——基于basys3开发板的秒表设计及应用_basys3开发板与鼠标连接

赞

踩

目录

摘要:本次秒表设计软件部分使用Xilinx公司的软件编译器Vivado完成,实现有清零、暂停和向下计数功能,并增加一个按键用于轮流切换两个七段数码管分别显示百分之一秒,秒,分钟,通过七段数码管显示秒表功能。硬件部分将功能输入接到BASYS3开发板推拉管的引脚,利用推拉管改变信号状态实现对各功能输入值的控制。其中,分频器模块使用偶分频原理得到100Hz输出;计数器模块分百分之一秒、秒、分钟,三者逻辑一致,将数据高低位分开计数并存储便于后续数码管显示;数显模块设置一个变量选择点亮的数码管同时也通过片选信号选择数据再通过译码电路翻译后送入开发板引脚。

关键词:偶分频、高低位分开计数、串行连接、片选信号。

正文:此次期末大设计实现秒表具有向上计数和向下计数功能,并设置复位、暂停、模式选择显示四种控制,将程序导入basys3开发板,通过开发板验证最后功能。由于设计此秒表功能较多,比较复杂,为使代码逻辑清晰,方便修改。故设计分模块进行并仿真验证,结果符合预期后再将模块整合。我的实验完成可分为以下几个步骤进行:

1.秒表总体框架分析和设计(大致思路设计)

2.程序编写与验证

2.1分频器设计 (偶分频原理)

2.2 秒表计数模块(此模块进行testbench仿真验证正误)

2.2.1 秒钟与分钟计数块 (利用if条件判断,高低位分开计数)

2.2.2百分之一秒计数块

2.3 数码管显示代码编写(此模块需验证与完善同时进行)

2.3.1 数码管扫描原理

2.3.2 数码管扫描模块算法思路

2.3.3 增加模式选择

2.4 导板约束文件编写 (此部分较易,按照教程即可)

3.导板验证功能并修改完善代码 (根据导板情况分析原因修改)

一、总体分析和设计

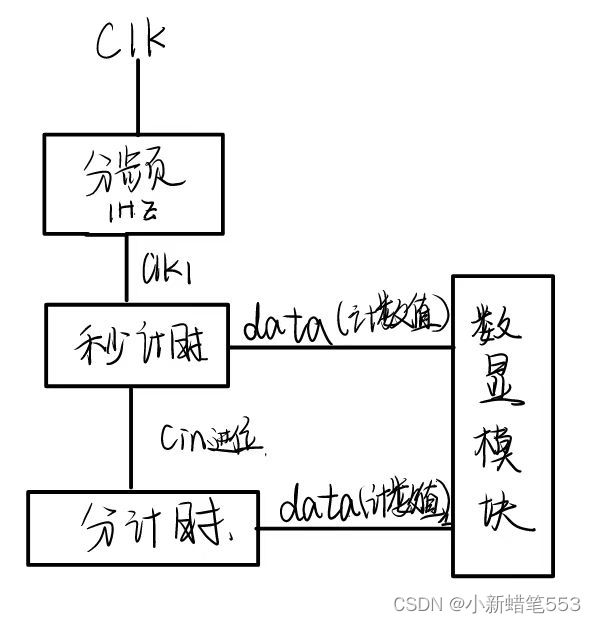

由于basys3开发板上自带晶振是提供100Mhz的时钟脉冲,故本次实验需要用到分频器,而秒表实现最易想到的是使用串行接法,即一个模块连接一个模块,从上一个模块得到进位作为clk信号。由此为基础画出简易的整个工程算法图:

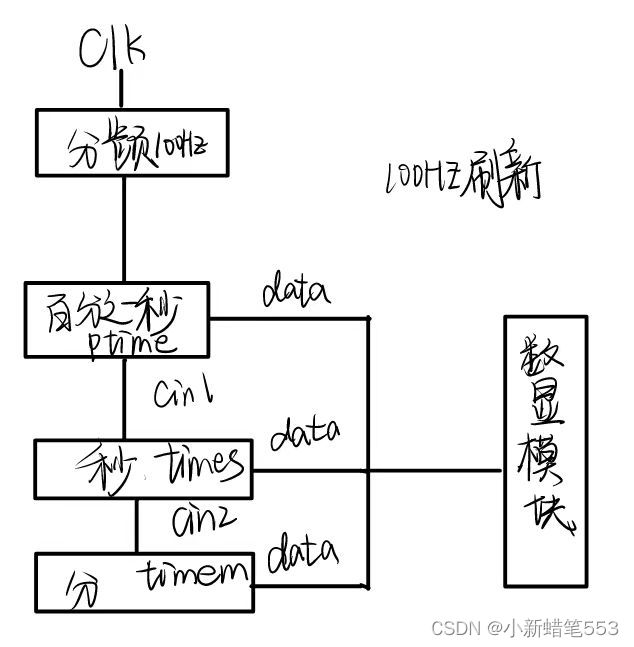

我的思路是首先制作出一个最简易的秒表仅实现计数功能即可,故在最开始的设计中没有引入百分之一秒模块,且最先原定秒计时和分钟计时模块分开编写,但在实验过程中发现三个计时模块原理几乎一致所以仅将一个模块编写出来即可。在改进代码时,通过百度查询得知,只要刷新频率超过50Hz人眼就无法分辨为了节约资源空间,删去了1Hz分频,全部采用100Hz分频。后面的框架图如下:

原理草图

二、实验过程

2.1 工程建立

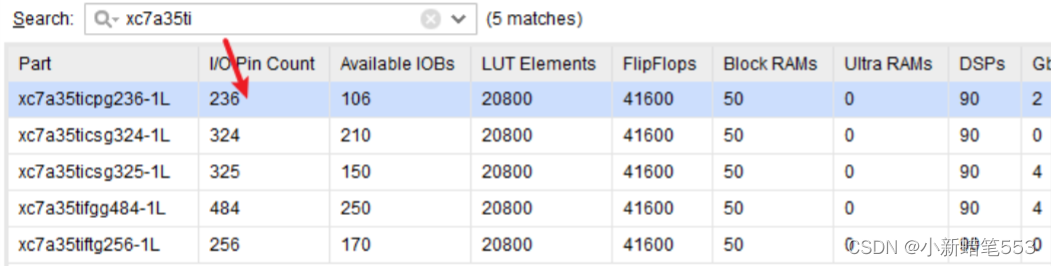

由于本次实验是需要导板验证的,故创建工程时需要选择basys3中的fpga芯片即

2.2 分频器模块

分频器通过接入晶振100Mhz的时钟信号,要将其变成100hz的时钟信号,故必须使用分频器,此项目中分频器的原理比较简单,与偶分频一致,实现占空比一比一的信号。首先计算计数的初值:

clknum=N/2-1

为产生100Hz信号计数值应为499999,即每次计数达到这个数之后便将时钟翻转一次,以clk1为输出。

设计思路图代码如下:

2.3 时钟计数模块

2.3.1 分秒计数(向上计数)

在此模块的设计中,我的算法思路经过了转变和更改。最初的设计思路是想时钟计数和分频器类似,也是将获取到的clk脉冲转化成一个60进制的脉冲,算法思路如下:

在后续编写数码管的代码时,由于七段数码管是共用八根数据线,在编写时要将时钟的个位和十位分别显示在左右两个数码管,于是需要将时钟数据的十位和个位分开,于是想到在计数模块利用c语言思路通过多次if判断将代码更改为高位和低位分开计数,这样在后续数码管代码编写中直接将高低位的四位数据根据片选信号分别传送进去译码即可。注:输出计数数据最初始一定要赋0,否则不使用清零键无法正常计数。

优缺点分析:相较于前种算法来说将高低位分开逻辑更清晰,且避免后续高低位分开传送的麻烦。但此种思路需要判断的条件较多,占用资源较多,第一种方案只需判断计数是否满60,节省资源空间,若编写大工程代码时第二种算法将使项目运行变慢。

分钟的代码逻辑与秒钟的逻辑一致,故只需在顶层代码中将此模块调用两次即可。注:分钟的clk信号接入的是秒钟的进位。

观察波形输出符合设计,故此部分代码正确。

2.3.2 分秒计数(向下计数)

基于分秒向上计数的逻辑,增加一个向下计数的功能,由信号down来控制,通过改变down的高低电平值控制计数模式,当down位高电平时向下计数。此部分与向上计数的代码几乎一致,只需将判断条件更改即可:

由于vivado上无法观察到1s的变化,故在仿真时接入的时钟以10ns翻转一次,仅用于功能检查使用,

通过验证,分秒的计数模块功能基本通过验证,基于整个分秒计数模块,再将百分之一秒的计数模块添加进来。

2.3.3 百分之一计数(向下计数)

此部分的设计逻辑可以直接全盘照搬整个分秒计数模块的代码,稍有不同之处在于分秒计数是 60进制,而百分之一秒是100进制的。

加入此模块后,我将原本的1Hz脉冲的分频部分删去,改成100Hz脉冲接入百分之一秒计时模块,再将百分之一秒进位接入秒钟计时模块,秒钟的进位接入分钟计时模块实现三种模式的串行连接。

在验收完成后重新查看代码时发现在最先设计的分秒计数模块原理中还可以进行改进。第一个方案放弃的原因是没能设法将高位和低位数据分开,从而想到高位和低位分开计数,除此之外还可以采用同时计数,在高位和低位数据分开部分通过将数取整或取余来得到,这样在计数模块中就省去了很多的判断,只需要将计得的数据分开存储再传入到数显模块即可。

2.4 数码管显示模块

2.4.1 数码管扫描原理

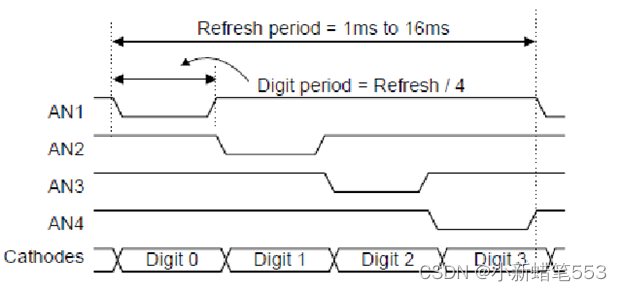

由于数码管是公用八位数据线,也就是说数码管一次只能点亮一个七段数码管,而要是人眼视觉上看到两位数据显示就需要不断的刷新数码管,利用发光二极管的余晖效应使其产生视觉停留达到“同时显示”的效果。经过百度查阅,一般数码管采用30到50Hz的刷新频率即可在人眼产生视觉停留,但为减少分频器的使用,节省空间,在本次实验中数码管刷新频率采用100Hz。

动态刷新原理图

2.4.2 数码管扫描模块算法思路

由于此秒表设计要求只点亮两位七段数码管,故设置一个一位的变量c,每当clk脉冲来到时便加1,由于c的位长只有1,故每次加一仅仅是c由0变为1或1变为0。除此方法外还可以通过每当clk脉冲进来时将c翻转一次亦可。通过判断c为0或1来控制要点亮的数码管及读取输入的数据,来回交替显示数据的高位和低位。:

在译码电路部分由于basys3开发板的数码管是共阳极,故当输入信号为0时有效:

利用always语句不断对读取的数据进行译码

为防止case模块可能会出现错误,故在编写中每个case块都使用default语句对未编写的情况赋一值以免在运行代码过程中产生不必要的麻烦。

2.4.3 添加模式选择

由于实验的高级要求是要通过控制开关实现利用两位七段数码管分别显示百分之一秒、秒和分钟三种模式,于是在上述数码管的代码基础上增加一个两位长的输入用于控制要显示的数据,

其中datas、datam、datap均为要显示的数据输入。

需要完整版代码和报告请私信沟通~