- 1给BERT补充其他特征的编码器实践_bert 自编码器

- 2Cobaltstrike简介及实战_cobalstrike

- 3【数据结构与算法】哈希—— 位图 | 布隆过滤器 | 哈希切割_布隆过滤器 哈希算法

- 4【MySQL】insert和select单表查询详解(包含大量示例,看了必会)_insert select

- 5python控制windows窗口,python 控制桌面程序_pyautoit

- 6QML动画(基本动画)_qml鼠标点击动画

- 7小白如何编写微信小程序的页面结构_小程序页面js的结构设计

- 8深入理解LinkedList_linkedlist 左右哪边是头

- 9使用 FastAPI 实现聊天完成 API 详解_fastapi stream api

- 10sql优化-单表优化_单表慢sql优化

ug476_7Series_Transceivers学习之接收_fpga gtx

赞

踩

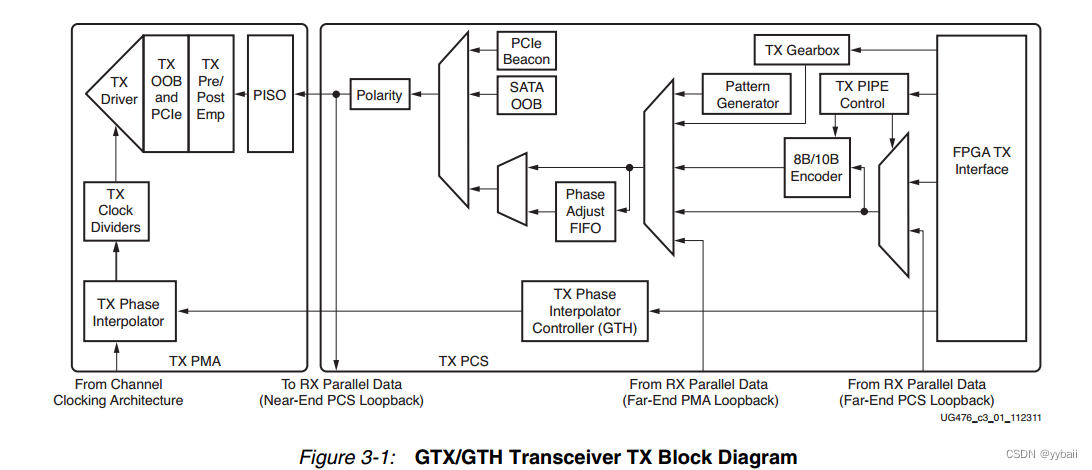

GTX的发送接口

1. FPGA TX接口

①FPGA的TX接口是FPGA到GTX/GTH收发器的TX数据路径的网关;

②设备在TXUSRCLK2上升沿时将数据写入TXDATA,通过GTX收发器传输数据(可配置端口宽度);

③TX的线速率决定并行时钟TXUSRCLK2,TXUSRCLK必须提供给内部PCS;

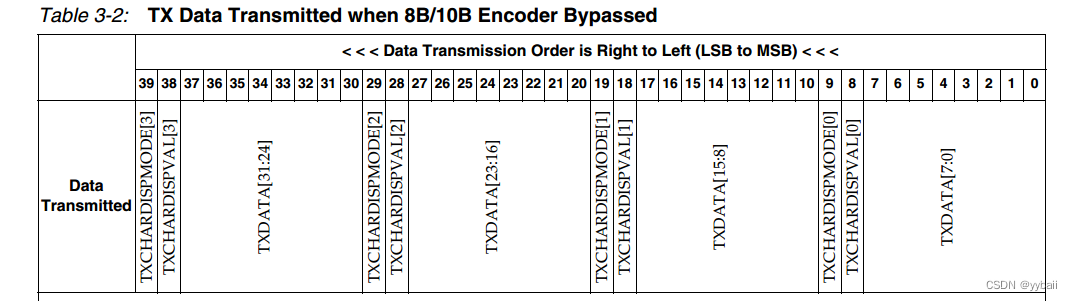

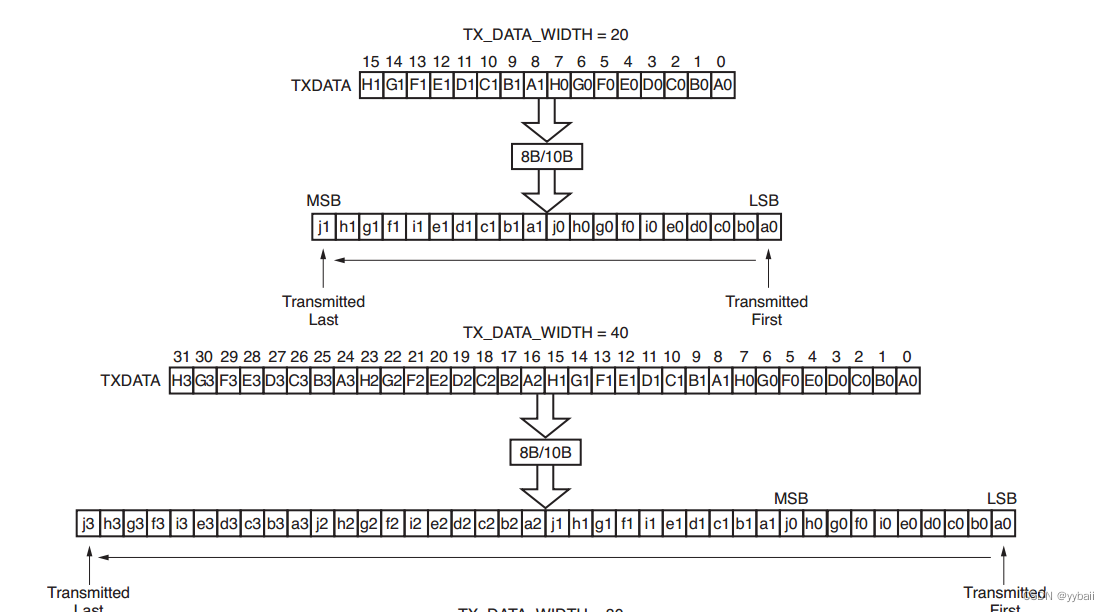

④当开启8B/10B编码器时,TX_DATA_WIDTH属性必须配置为20位、40位或80位,此时FPGA的TX接口只使用TXDATA端口;当不适用8B/10B编码器时,TX_DATA_WIDTH属性可以配置为任何可用的宽度:16,20,32,40,64或80位。;当绕过8B/10B编码器,TX_DATA_WIDTH为20,40或80时,使用txchardismode和txchardisval端口将TXDATA端口从16位扩展到20位,32位扩展到40位,或64位扩展到80位。(具体见表3-1设置)

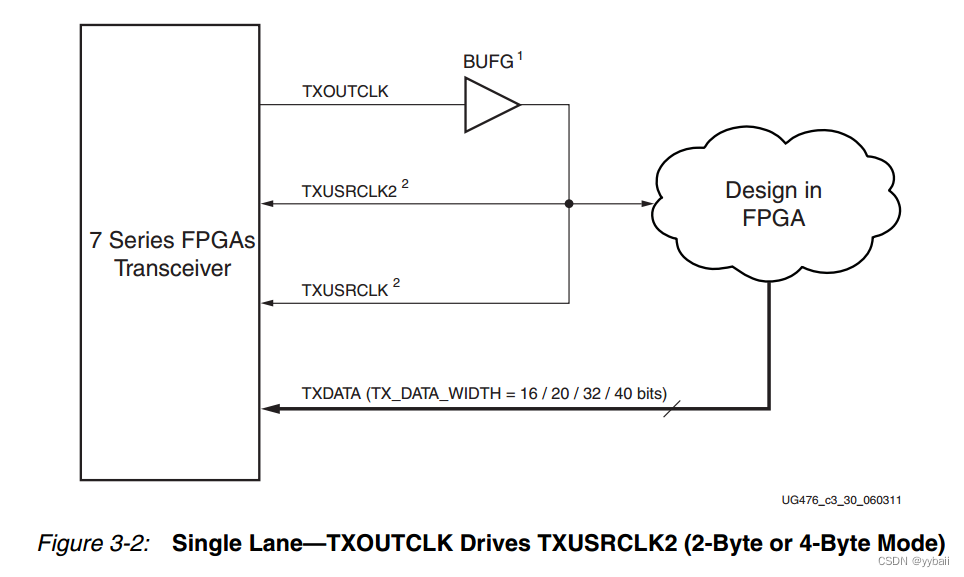

⑤FPGA的TX接口包括两个并行时钟:TXUSRCLK和TXUSRCLK2;

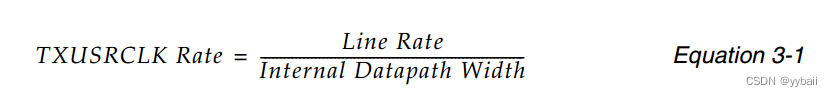

TXUSRCLK是TX中PCS逻辑的内部时钟,计算公式如下:

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

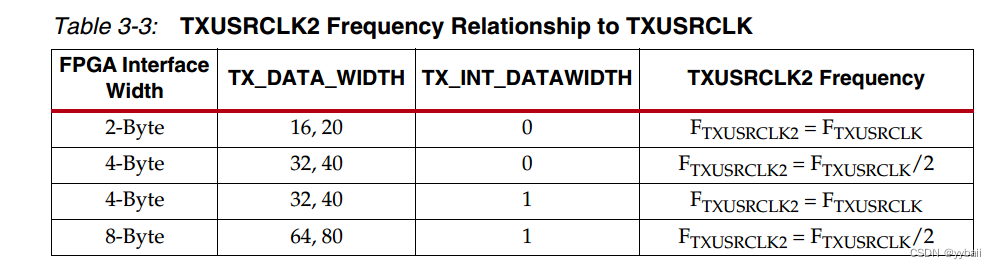

TXUSRCLK2是GTX收发器TX端信号的主同步时钟

两个时钟的对应关系:

MMCM(Mixed-Mode Clock Manager):是Xilinx FPGA 中的一种时钟管理模块。MMCM 的主要作用是对输入的时钟信号进行管理和处理,包括时钟频率的分频、倍频、相位调整等功能,以满足不同部分电路对时钟的要求。

注:

CMT:Clock Management Tile ,简称CMT,是xilinx FPGA中的时钟管理器。DCM/PLL/MMCM都包含在CMT中。

DCM是比较早的FPGA中使用的,比如Sparten-3和Virtex-4,后面的器件不再使用了。在Virtex-4中,CMT包括一个PLL和两个DCM。DCM的核心是DLL,即Delay Locked Loop,它是一个数字模块,可以产生不同相位的时钟、分频、倍频、相位动态调整等,但精度有限。

PLL(Phase-Locked Loop,锁相环)是一种电路和控制系统中常见的反馈系统,用于产生一个输出信号,其相位和频率与一个参考信号相锁定。,时钟倍频、分频、调节相位等都是可以用PLL,而且PLL是一个模拟电路,它产生的频率比DCM更加准备,jitter也更好,但PLL不能动态调整相位。

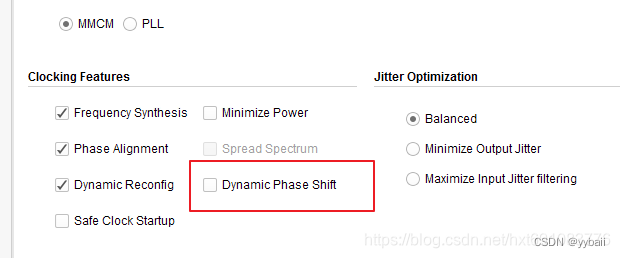

MMCM(Mixed-Mode Clock Manager)是Xilinx FPGA 中的一种时钟管理模块。MMCM 的主要作用是对输入的时钟信号进行管理和处理,包括时钟频率的分频、倍频、相位调整等功能,以满足不同部分电路对时钟的要求。它是在PLL的基础上加上了相位动态调整功能,因为PLL是模块电路,而动态调相是数字电路,所以叫Mixed Mode。7系列和Ultrascale中,MMCM和PLL同时存在。7s FPGA中,最高包含了24个CMT,每个CMT包含一个MMCM和一个PLL。Ultrascale中,一个CMT包含一个MMCM和 两个PLL。

MMCM相对PLL的优势就是相位可动态调整,但PLL占用的面积更小。

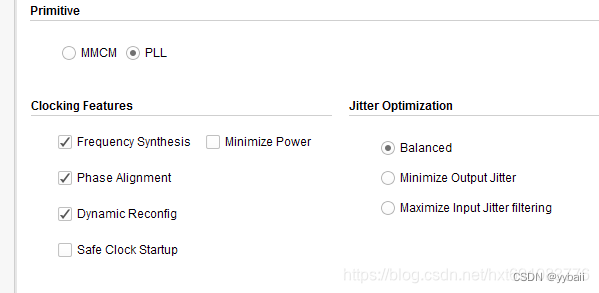

在Vivado中,在使用Clock Wizard时,我们可以选择使用MMCM或者PLL,而且可以它们的区别也仅仅下图的红框部分。

2. TX 8b/10b解码器

① 8b/10b编码器是一种数据编码技术,用于将8位的二进制数据编码成10位的符号。它的目的是在数据传输中提供一种均衡的编码方式,以确保传输过程中的直流分量较小,有利于时钟恢复和减小传输误码率。

- 1

主要见下面两个图:

②8B/10B编码是直流平衡的,这意味着长期传输的1和0的比例应该正好是50%。为了实现这一点,编码器总是计算传输的1的数量和传输的0的数量之间的差异,并在传输的每个字符结束时,使差异+1或-1。这种差异被称为运行差异

③ 相关端口见P118-119

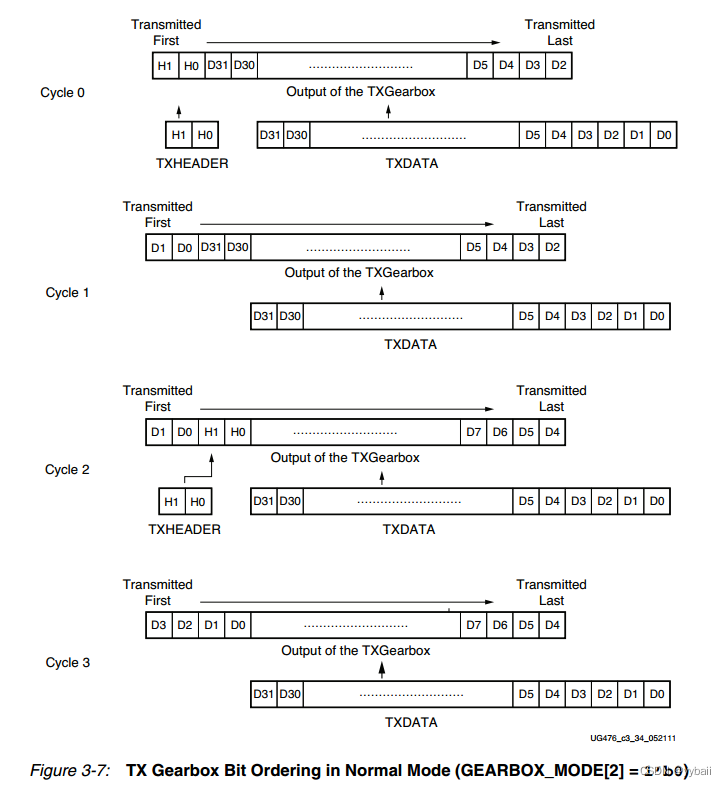

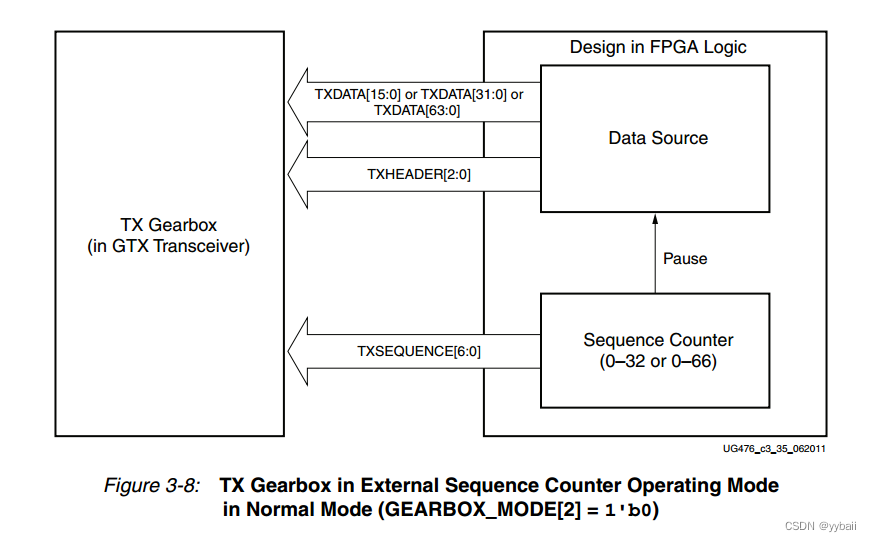

3. TX Gearbox

3.1 TX变速箱支持2字节、4字节和8字节接口

3.2

3.3 TX gearbox两种工作模式:外部序列计数器操作模式必须在用户逻辑中实现。第二种模式使用内部序列计数器。

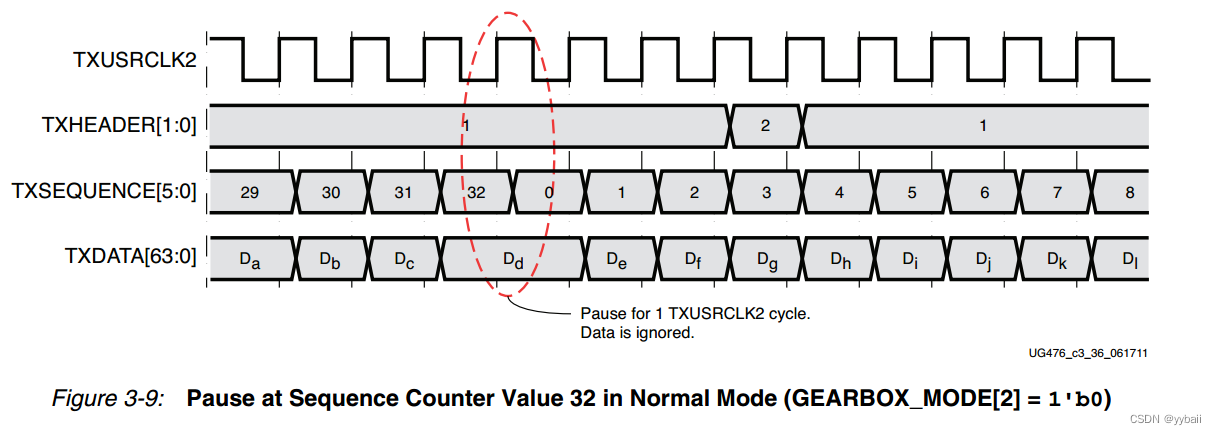

下图为在正常模式(GEARBOX_MODE[2] = 1’b0)下使用8字节结构接口和4字节内部数据路径在外部序列计数器模式下使用64B/66B编码时,计数器值32如何发生暂停。

①应用GTTXRESET并等待重置周期完成。

①应用GTTXRESET并等待重置周期完成。

②复位时,将7’h00应用于TXSEQUENCE,报头信息应用于TXHEADER,初始数据应用于TXDATA。这种状态可以无限期保持,直到数据传输就绪。

③在计数0时,将数据应用到TXDATA,并将报头信息应用到TXHEADER。对于2字节接口(TX_DATA_WIDTH = 16),在计数为0时将第二个2字节驱动到TXDATA。

④ 当数据在TXDATA上驱动时,序列计数器增加到1。

⑤在应用4个字节的数据后,计数器增加到2。在TXDATA上应用数据,在TXHEADER上应用报头信息。

⑥计数21时,停止数据管道。

⑦ 计数22时,在TXDATA上驱动数据。

⑧计数44时,停止数据管道。

⑨在计数45时,将数据放在TXDATA上。

⑩ 计数65时,停止数据管道。

在计数66时,驱动TXDATA上的数据。

3.4 内部序列计数器工作模式

不想看了,这部分没看懂,之后需要再看吧

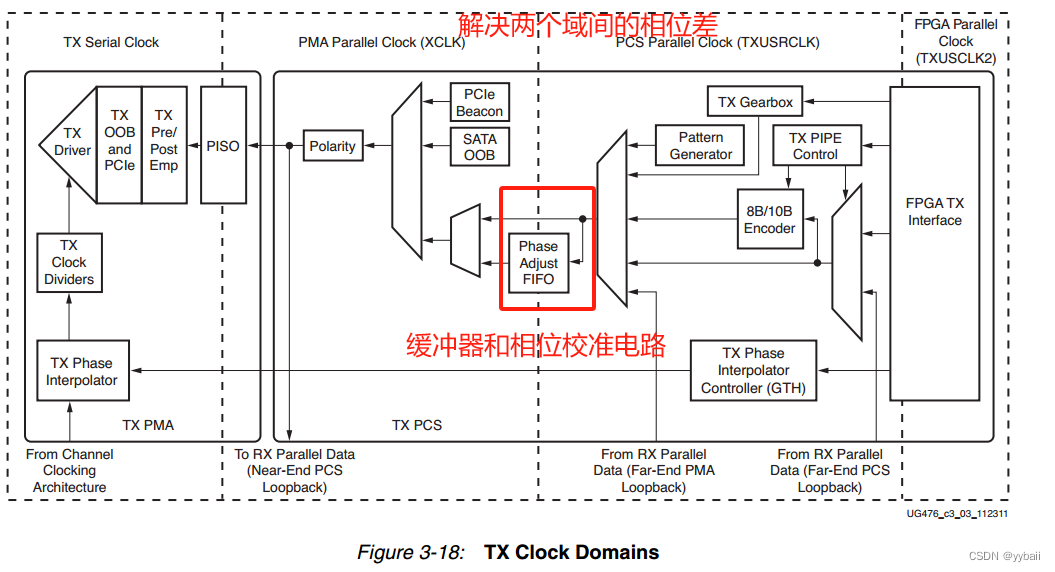

4. TX Buffer

GTX/GTH收发器TX数据路径有两个内部并行时钟域,用于PCS: PMA并行时钟域(XCLK)和TXUSRCLK域。

相关端口:P134-135

5. TX Buffer Bypass

绕过TX缓冲区是7系列GTX/GTH收发器的高级功能。TX相位对准电路用于调整PISO并行时钟域与TX XCLK域之间的相位差,从而将pc机的数据传输到PISO中。它还通过不断调整TXUSRCLK来补偿温度和电压变化来执行TX延迟校准。组合的TX相位和延迟对准可以由GTX收发器自动执行,也可以由用户手动控制。对于GTH收发器,此功能必须由用户手动控制。关于XCLK和TXUSRCLK域,请参见图3-18,第133页;关于缓冲和相位对齐之间的权衡,请参见表3-14,第134页。

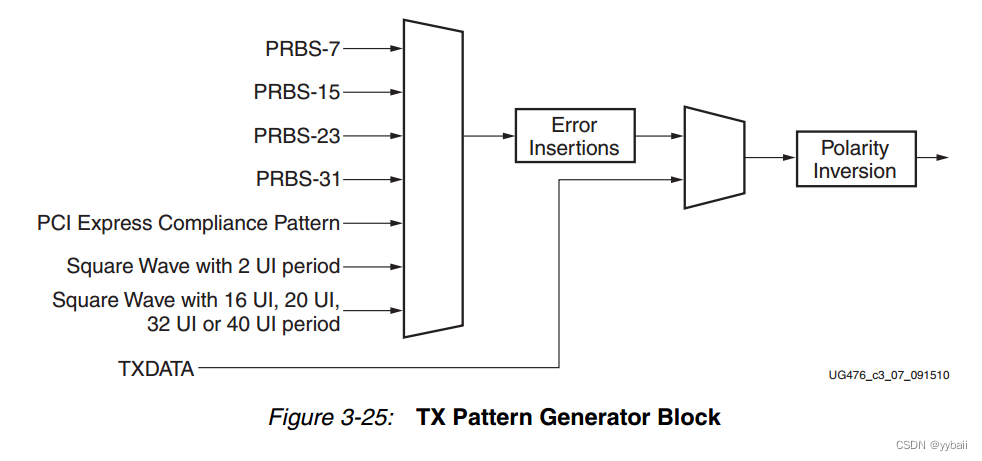

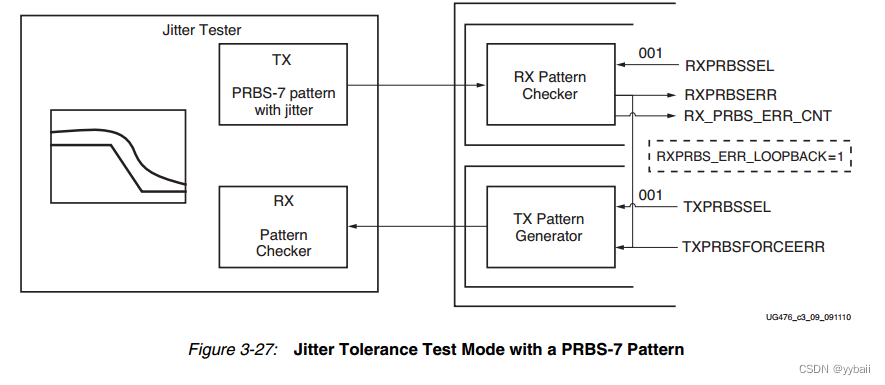

6. TX Pattern Generator

① TX Pattern Generator(发射端模式生成器)通常是指在通信系统中用于生成特定数据模式的模块或设备。这个模块的作用是产生特定的数字数据序列,用于测试和验证接收端的性能、协议实现等。在高速通信接口中,TX Pattern Generator 通常用于产生特定的数据模式,以便在物理层进行测试和调试。

主要功能包括:

模式生成: 生成指定模式的数字数据序列,可以是特定的比特模式、序列模式等。

数据速率设置: 允许用户设置生成的数据模式的传输速率,以适应不同的通信速率。

时钟生成: 在需要时可以生成与数据模式同步的时钟信号。

调试和测试: 用于系统调试、性能评估和验证。通过产生已知的数据模式,可以检查接收端的正确性和可靠性。

TX Pattern Generator 通常与 RX (Receiver) 部分一起使用,RX 部分接收并解析由 TX 产生的模式,以进行性能分析和故障排除。这对于高速通信接口的开发、验证和调试非常重要。在 FPGA 或 ASIC 中,TX Pattern Generator 通常由硬件模块或相应的 IP(知识产权)核实现。

② 伪随机比特序列(PRBS)是一种常用的高速链路信号完整性测试方法。这些序列看起来是随机的,但具有特定的属性,可以用来衡量链路的质量。

相关端口见P147

相关端口见P147

7. TX Polarity Control

①TX Polarity Control(发射端极性控制)是一种用于控制发射端信号极性的功能。在高速通信系统中,为了确保信号的正确传输,发送端和接收端的信号极性需要匹配。TX Polarity Control 允许调整发送端的信号极性,以便与接收端期望的极性匹配。

②

8. TX Fabric Clock Output Control

时钟输出控制

TX时钟分压器控制块有两个主要组成部分:串行时钟分压器控制和并行时钟分压器和选择器控制。

9. TX Phase Interpolator PPM Controller

TX相位插补器百万分率(TXPIPPM)控制器模块提供动态控制TX相位插补器(TXPI)的支持。位于TX PCS中,其输入来自FPGA TX接口,输出到TX PMA。

从锁相环输出时钟的控制是通过一个TX PI实现的,它反过来可以由TX相位插补器PPM控制器模块控制。FPGA逻辑可以通过使用PCS中的TX相位插补器PPM控制器模块来控制TX PMA中的TX PI。

相关端口见P154-155

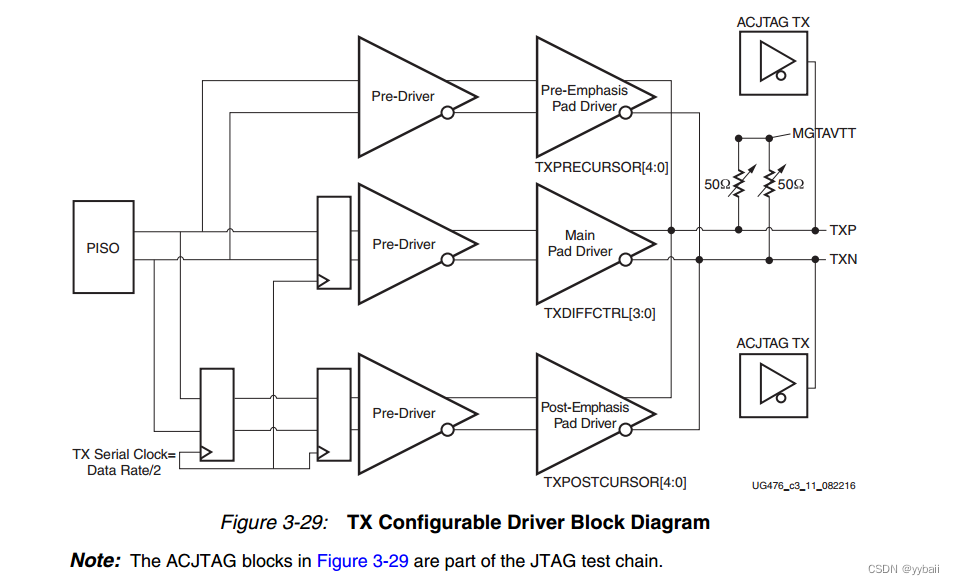

10. TX Configurable Driver

TX/GTH收发器TX驱动是一个高速电流模差分输出缓冲器。为了最大限度地提高信号完整性,它包括以下功能:

•差分电压控制

•前光标和后光标传输预强调

•校准终端电阻

端口见P156-162

11. TX Receiver Detect Support for PCI Express Designs

12. TX Out-of-Band Signaling

每个GTX/GTH收发器都支持生成串行ATA (SATA)、串行附加SCSI (SAS)规范中描述的带外(OOB)序列,以及PCI Express规范中描述的信标