- 1链表的设计_首先定义一个节点类,包含数据域和指针域,然后定义链表类,链表中包含一个头节点,该

- 2迎七一党史知识竞赛答题怎么做

- 3Opencv测量图片中的物体大小_opencv测量物体尺寸

- 4opencv小工具-绘制resnet50热力图和灰度图-伪彩色映射_opencv 热力图

- 5LLM-大模型训练-步骤(二)-预训练/Pre-Training(1):全参数预训练(Full-Param Pre-Training)【对LLaMA等模型进一步全量参数预训练】【中文无监督学习语料】_大模型预训练方法

- 6你应该立即掌握的10个现代C++新特性

- 7sql查询 ,多行数据合并成一行,并且显示合并后某一列的值拼接结果_sql查询结果合并成一条数据

- 8NB-IoT应用开发笔记_nb-iot发送到天翼云

- 9基于STM32单片机的健康检测系统_基于stm32的人体健康状态检测系统

- 10AJAX 数据库

代码逻辑分析_借助Elaborated Design优化RTL代码

赞

踩

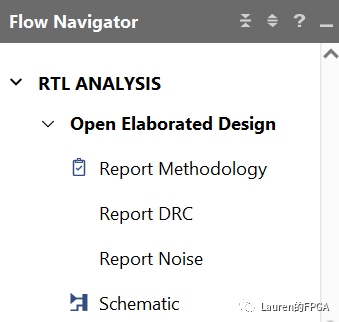

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属于RTL Analysis这一步对应的设计。可能很多工程师都没有使用到,而实际上对于代码优化,它是很有帮助的。

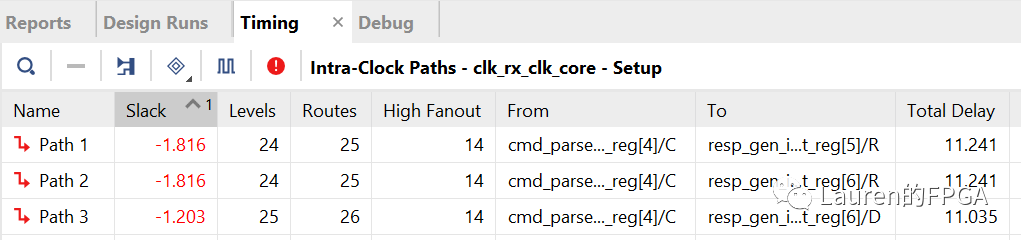

通常情况下,我们总是习惯了打开综合后的设计,执行诸如

report_timing

report_timing_summary

report_design_analysis

等命令分析时序,却忽视了RTL代码层面的优化。通过这些命令找到关键路径之后,一个重要的步骤是检查这些路径上的逻辑单元是否很好地映射到FPGA器件中。如果没有,就要尝试通过修改RTL代码、使用综合属性(Synthesis Attribute)、设置综合选项、使用BlockLevel综合技术或者使用不同的综合策略优化RTL代码,使得在综合之后时序能够达到一个较好的结果。这对于逻辑级数较高的路径尤为重要。因为高逻辑级数的路径会对后期布局布线带来很大的压力,同时成为设计整体性能提升的瓶颈,更明显的是改善高逻辑级数路径的常用且有效的方法是插入流水寄存器以降低逻辑级数,这一工作在设计初期完成最为快捷,越是在设计后期越难以做这一工作。

在Vivado Project模式下,同时打开Synthesized Design和ElaboratedDesign。在Synthesized Design下对设计进行分析,找到设计的关键路径,生成相应的时序报告,如下图所示。选中图中的时序路径,按下F4,会生成该路径对应的Schematic视图,同时还可以看到路径上的逻辑单元(cell)和单元之间的连线(net)都已被选中。此时切换到Elaborated Design,按下F4,可看到这条路径在Elaborated Design下的Schematic视图。这时候就可以检查这条路径的RTL逻辑单元,尤其是注意执行了哪些操作、数据位宽是否合理。

Tcl之$$a 80%的概率......AI Engine到底是什么?

Tcl之$$a 80%的概率......AI Engine到底是什么?

ACAP不可不知的几个基本概念

嵌套的for循环,到底对哪个执行pipeline更好

HLS中循环的并行性(2)

HLS中循环的并行性(1)

HLS优化方法DATAFLOW你用了吗

HLS中如何控制流水程度

Vivado HLS学习资料有哪些

如何查看可综合C代码的中间结果

如何在C代码中插入移位寄存器

HLS IP Library? HLS Math Library:csim ?C/RTL co-sim(2)HLS Math Library:csim ?C/RTL co-sim(1) 如何快速找到组合逻辑生成的时钟并行加法的高效实现加法树还是加法链?两个数相加,三个数相加有什么不同

加法运算很简单?AXI-4 Lite与AXI-4 Memory Mapped有什么区别?深入理解AXI-4 Memory Mapped 接口协议AXI是Interface还是Bus?如何阅读时序报告时序报告要看哪些指标如何使set_max_delay不被覆盖一些小巧的IPIP是用DCP还是XCI?如果使用第三方综合工具,Xilinx IP…IP生成文件知多少IP的约束需要处理吗?IP为什么被Locked?copy_ip你用过吗?IP是XCI还是XCIX 如何降低OSERDES/CLK和CLKDIV的Clock Skew如何获取Device DNA谈谈设计复用过约束到底怎么做时序收敛之Baseline什么情况下要用OOC综合方式异步跨时钟域电路该怎么约束如何复用关键路径的布局布线信息Vivado学习资料有哪些?异步跨时钟域电路怎么设计 ECO都有哪些应用FPGA中的CLOCK REGION和SLR是什么含义FPGA中的BEL, SITE, TILE是什么含义约束文件有哪些 如何高效复用Block的位置信息? 如何复用关键寄存器的位置信息 部分可重配置都生成哪些.bit文件VIO你用对了吗Device视图下能看到什么Schematic视图下能看到什么都是pin,有什么区别都是net,有什么区别 如何快速查找目标cell学习笔记:深度学习与INT8学习笔记:多层感知器学习笔记:单层感知器的局限性 学习笔记:单层感知器基础知识 学习笔记:神经网络学习算法学习笔记:神经网络模型 学习笔记:ReLU的各种变形函数学习笔记:神经元模型(2)学习笔记:神经元模型(1)学习笔记:深度学习之“深” 学习笔记:深度学习之“学习”学习笔记:人工智能、机器学习和深度学习2019文章汇总

文 | Lauren 图 | Lauren

Copyright @ Lauren的FPGA

转载事宜请私信 | 获得授权后方可转载

文 | Lauren 图 | Lauren

Copyright @ Lauren的FPGA

转载事宜请私信 | 获得授权后方可转载