- 1大数据ETL开发之图解Kettle工具(入门到精通)_kettle从入门到精通

- 2浅谈Cesium和Three.js异同及相关技术基本概念

- 3jquery控制元素的隐藏和显示的几种方法_jquery设置css隐藏显示

- 4arcgis for android Geometry获取中心点_arcgis android 获取中心点

- 5可雅白兰地koya白兰地:可雅XO白兰地的悠然人生

- 6[数据结构]优先级队列(最大堆)详解_数据结构介绍优先队列 最大堆

- 7刷简单的编程题也很吃力怎么办,欢迎新手点赞收藏_编程刷题总是感觉自己好笨

- 8通过Docker安装KingbaseES V8并激活开发License

- 9Arduino提高篇(十六)六轴姿态MPU6050_imu6050

- 10android使用adb工具调试sqlite数据库

关于7系列FPGA GT 高速收发器的一些认识(一)_cpll和qpll的区别

赞

踩

一.基本概念

1.对于quad的理解

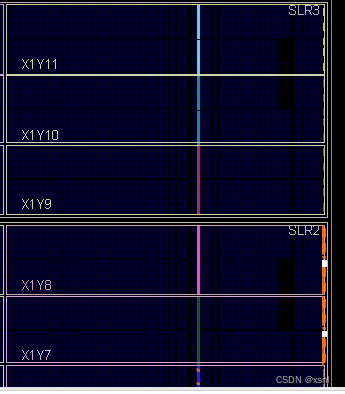

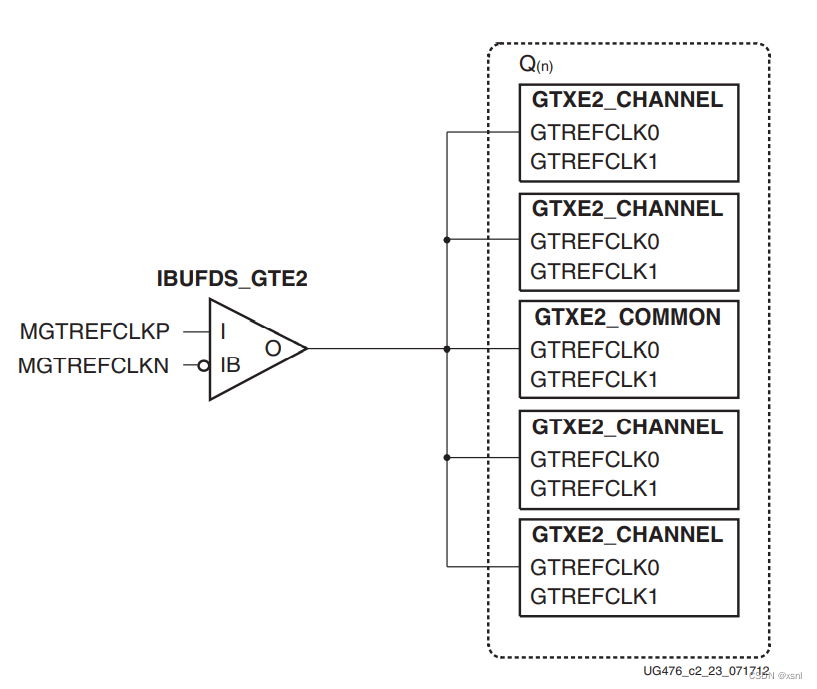

一个quad包括4组GT 高速收发器(GT 高速收发器有四种,差异不大,以下为GTX),基于交换机即是对应4个端口,每一个quad有着2组差分时钟,但是7系列支持南北时钟,也就是除了该quad自身拥有的2组差分时钟,该quad还可以被上下两个quad的总共4组差分时钟驱动。7系列的FPGA中,所有GTX的quad位于模具一侧的单个列中。如图:右边橘黄色部分即为quad。(图中标黄部分有两个quad)

2.bank

每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同,只有相同电气标准的端口才能连接在一起。7系列FPGA中是按照bank来进行划分,而对于quad来说,一个quad相当于一个bank,quad中4个GTX所用的电压驱动一样。图一中的前四组橘黄色块为一个quad,对应117bank(白框)中的4组黄点。网上很多资料都说一个bank为一个quad,其实不完全对,一个bank包括很多接口标准一样的IO口,而quad只是其中一部分,但是平常大家都叫quad为bank。

3.Channel

一个GTX是一个Channel。

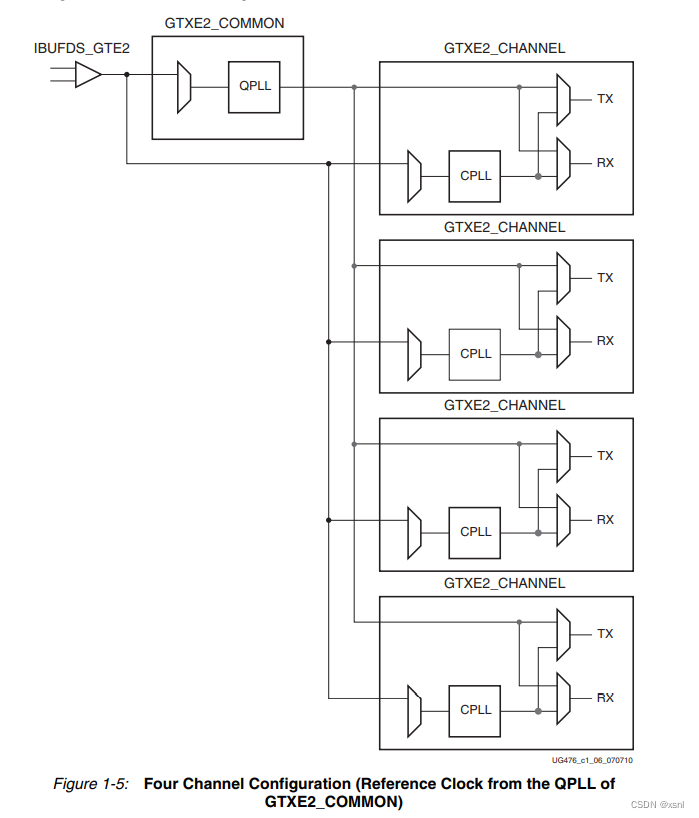

4.QPLL和CPLL

已知4个GTX为一个quad,一个GTX是一个Channel。QPLL是一个quad共用的PLL, CPLL是一个Channel所使用的PLL。前者位于quad的common模块中,后者位于Channel模块中。如下图:

二.由表如里

图一中的一个区域称为Clock region,图二中的一个区域称为一个bank,图三就是一个quad。细品!

1.图三中的COMMON区域

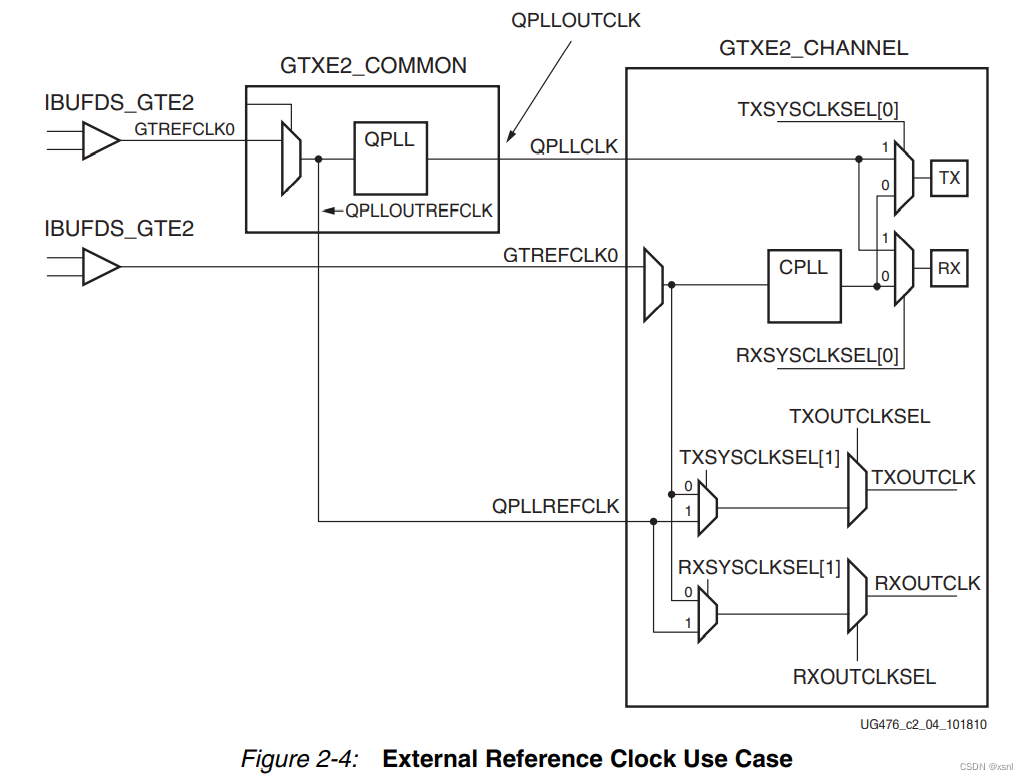

上面说过一个quad可以由6组差分时钟驱动,对应图四中的前六组差分时钟,第七组可以不关注,COMMON可以产生两个时钟,QPLLOUTCLK给GTX的收发端用,QPLLOUTREFCLK的作用下面在讲。

2.图三中的CHANNEL区域

CPLL和QPLL一样,由6组差分时钟的其中一组驱动,当CPLL和QPLL的驱动时钟一样的时候,其实该驱动时钟就是QPLLOUTREFCLK(如图七)。QPLLOUTCLK和CPLLOUTputCLK通过一个由SYSCLKSEL控制的选择器来驱动GTX的收发端。这里就会有人问了,为啥GTX不只用QPLL或者CPLL,而且二者的驱动时钟可以一样,二者到底什么不一样。二者区别在于两者支持的线速率不同,对于CPLL来说,支持的线速率位1.6GHz到3.3GHZ之间,而对于QPLL来说,GTX支持的线速率分两档,Lower Baud支持5.93GHz~8.0GHz,Upper Baud支持9.8GHz~12.5GHz。用户可以灵活使用QPLL或CPLL的不同组合来驱动GTX的收发数据路径。

3.QPLLOUTREFCLK的作用

图中可以看到QPLLOUTREFCLK是用来生成TXOUTCLK和RXOUTCLK的。

4.CPLL和QPLL(图七中CHANNEL和COMMON)用同一个驱动时钟(作者当前做的项目就是这种用法)

5.Note

(1)一个quad只能被最多其他两个quad驱动(南北时钟)

(2)一个时钟引脚(差分时钟)最多驱动12个GTX(当前quad,南北quad)