遇见BUG(3)critical warning也要关注!_common 17-55

赞

踩

在Vivado调试工程时候,是不是有这么一个习惯(至少是我),只要不是error,哪怕再多的critical warning,也不多看一眼,认为与我无关,只是相应的EDA工具多此一举。

嗯,,,有时候固然如此,工具不太智能,但是我们要发挥人为的价值,练就火眼金睛,去察觉哪些会对我们的工程产生影响,哪些有必要解决。

今天的猪脚是如下的critical warning:

[Common 17-55] 'set_property' expects at least one object. [G:/FPGA_ING/FPGA_2/SigPro_Channel/SigPro_Channel.srcs/constrs_1/imports/constrs_1/pins.xdc:262]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

是综合之后跳出的对话框:

拿上条提示为例:

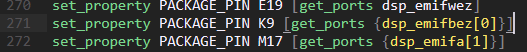

显示了问题的定位在pins.xdc的262行,那就定位到那里:

![]()

类似的提示还有:

271行:

273行:

等

考虑到这些约束怎么会有问题呢?

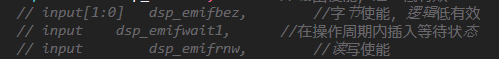

到顶层程序中去查看这些引脚:

发现这些引脚已经被注释掉了,意味着这些引脚在此程序中已经不是输入输出了,可是旧的引脚约束却没有自动更新,我能不能说这是EDA工具不智能或者存在Bug的地方呢?

还有类似的问题是在I/O Planning中约束了某个引脚,却在约束文件里面找不到这个引脚的约束,也就是GUI界面和约束文件不对应,这个问题真是让人头大。

所以不得不细心地查看EDA工具给出的warning,然后手动的解决这些问题。

请删掉这些多余的约束,物是人非!

参考链接:https://www.xilinx.com/support/answers/56169.html