热门标签

热门文章

- 1零基础如何入门深度学习?_从零开始学习深度学习

- 2创始人专访 | Kimi:因为自己淋过雨,所以总想给别人撑把伞_kimi人工智能创始人

- 3人工智能|万字长文!一文带你弄懂AI技术及大模型演进的前世今生_人工智能大模型 需要知识

- 4ChatGLM2 大模型微调过程中遇到的一些坑及解决方法(更新中)_chatglm2微调lora常见错误

- 5人工智能与宇宙探索:寻找宇宙的秘密

- 61、Python微型web框架Bottle简介_bottle框架打开页面自动加载

- 7循环神经网络和自然语言处理介绍||文本情感分类|| 循环神经网络||循环神经网络实现文本情感分类||Pytorch中的序列化容器_pytorch.nn.emebeding的输入形状是什么

- 8es 数据类型

- 9基于预训练语言模型的文本生成研究综述

- 10人工智能——数据分析1_智能数据分析

当前位置: article > 正文

Modelsim仿真基本流程-以半加器的设计为例_modelsim仿真测试文件

作者:小丑西瓜9 | 2024-03-28 19:35:27

赞

踩

modelsim仿真测试文件

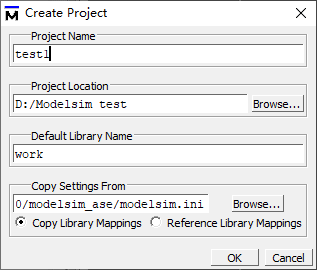

1、打开modelsim,创建新项目,选择项目保存位置,输入项目名称test1,点击OK。注意不要出现中文。

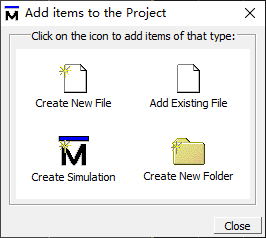

2、弹出对话框,选择新建文件

3、新建源文件,选择文件类型为Verilog,输入文件名half_add,OK。

4、新建测试文件test_bench,以顶层文件名后加_tb命名。

5、双击half_add.v,编辑源文件。

6、双击half_add_tb.v,编辑测试文件。initial中的代码用于初始化信号,只执行一遍,always中的代码则循环执行,用于产生半周期为T的信号b。

7、编译所有文件,并查看错误信息。

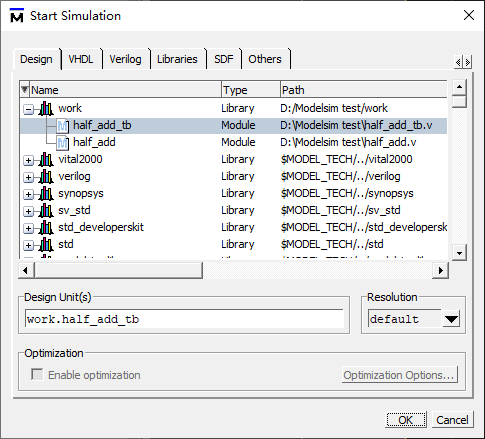

8、点击Simulation,start simulation,启动仿真,选择测试文件half_add_tb,OK。

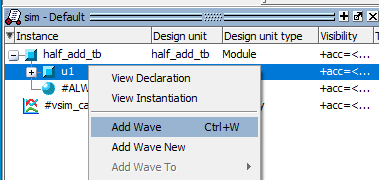

9、右击添加要查看波形的信号。

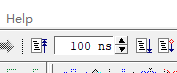

10、设置仿真时间,默认100ns

11、点击运行按钮

![]()

,查看100ns波形,也可多次点击该按钮,查看更长时间的波形,按照_tb代码对照波形。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小丑西瓜9/article/detail/330905

推荐阅读

相关标签