热门标签

热门文章

- 1【NLP】Google BERT详解_bert 精调

- 2ChatGPT强大功能:让 GPT 成为你的编程助手,用 GPT 实现某一特定功能的程序、对代码进行解释、进行代码纠错及修改、回答代码疑问、帮你优化代码、读取本地数据然后写代码、帮你提供完整项目代码_适合编程找错的chatgpt

- 3华为项目管理10大模板 【Word版 (可直接套用)】_华为项目管理十大模板下载百度网盘

- 4【讲解下目标追踪】

- 5vscode安装mysql相关插件_vscode mysql

- 6万兆网、10G ethernet subsystem IP核_万兆以太网ip核的参考时钟

- 7OpenSSL SSL_read: SSL_ERROR_SYSCALL, errno 10054

- 8陀螺仪c语言算法,陀螺仪传感器建模与卡尔曼姿态解算

- 9python代码实现决策树对鸢尾花的分类_鸢尾花决策树代码

- 10Git进阶(八):git stash 与 git add_git stash和git add区别_git stash add

当前位置: article > 正文

QuartusII实现4位加法器_quartus2设计并实现一个4位二进制全加器

作者:菜鸟追梦旅行 | 2024-06-12 11:41:20

赞

踩

quartus2设计并实现一个4位二进制全加器

4位加法器构建

1. 四位加法器基本原理

采用底层逻辑,通过自行构架原件搭建4位加法器: 半加器 -> 1位全加器 -> 4位全加器

逻辑原件构建过程: 1位全机器

一个4位全加器可以由4个1位全加器构成,加法器间的进位可以通过串行方式实现。通过将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接

2. 构建加法器

- 通过总线连接方式,进行加法器的拼接,

对单线进行命名

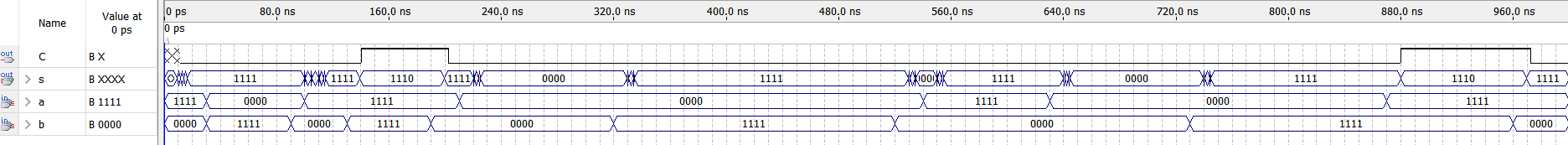

- 时序电路仿真

- 构建波形文件,导入输入输出节点,进行数字仿真

根据波形文件,查看全加器的实现,对于是否存在进借位可以看到明确的波形变化,四位全加器的功能性得到实现 - 构建波形文件,进行时序仿真

在进行基本时序验证过程中,对于波形文件的传输过程中不存在延迟问题,时序功能正常实现

- 构建波形文件,导入输入输出节点,进行数字仿真

- 硬件功能测试

-

引脚输入输出添加

在实现过程中,在硬件机上实现本过程中,调用led灯为3-10,3-6为第一位四位数输入,后四位为第二,同时添加引脚等作为进位输出 -

下载过程见上一贴

-

测试验证

- 测试1:

0001+0001= 0010

- 测试2:

1111+0001 进位1,和为0

- 测试1:

-

总结

- 在进行本次实验中,在实现四位全加器线路中,当

一位全加器中的cin无信号输入过程中,且未进行接地操作,则该过程中该输入端口在进行实物器件操作过程中,会默认输入信号为1,默认为高电平,导致全加器验证出现错误 - 使用总线方式进行线路搭建中,需要对指定的单线进行序号化命名,保证输入信号为正确信号,不会产生累加错误

参考

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/707946

推荐阅读

相关标签