- 1Linux中的vi/vim编译(一)_linux对vi程序编译

- 2Android内存优化13 内存泄漏常见情况4 资源泄漏

- 3SSM 三大框架原理、核心技术,运行流程讲解_ssm技术

- 4鸿蒙网络请求与共享参数的封装(实例演示)cv大法即可_鸿蒙开发网络请求封装

- 5Sift数据集

- 6HarmonyOS基础答疑_harmonyos是基础软件吗?

- 7Python 实现如何把txt文件中的数据(可以是文本型数据,也可以是数值型数据)读取出来放在numpy类型的数组中_将数值型数据写入文本文件时,必须先将数值型数据转化为字符串型数据

- 8虚拟机三种网络模式:桥接模式、NAT模式、仅主机模式_虚拟机网桥模式的功能和方法

- 9rust开发100问?

- 10Arcmap同时选中多个polygon/按要素属性选择/取消选择_gis按属性选择怎么选择多个

数字逻辑-时序逻辑电路二——沐雨先生

赞

踩

一、实验目的

(1)熟悉计数器的逻辑功能及特性。

(2)掌握计数器的应用。

(3)掌握时序逻辑电路的分析和设计方法。

二、实验仪器及材料

三、实验原理

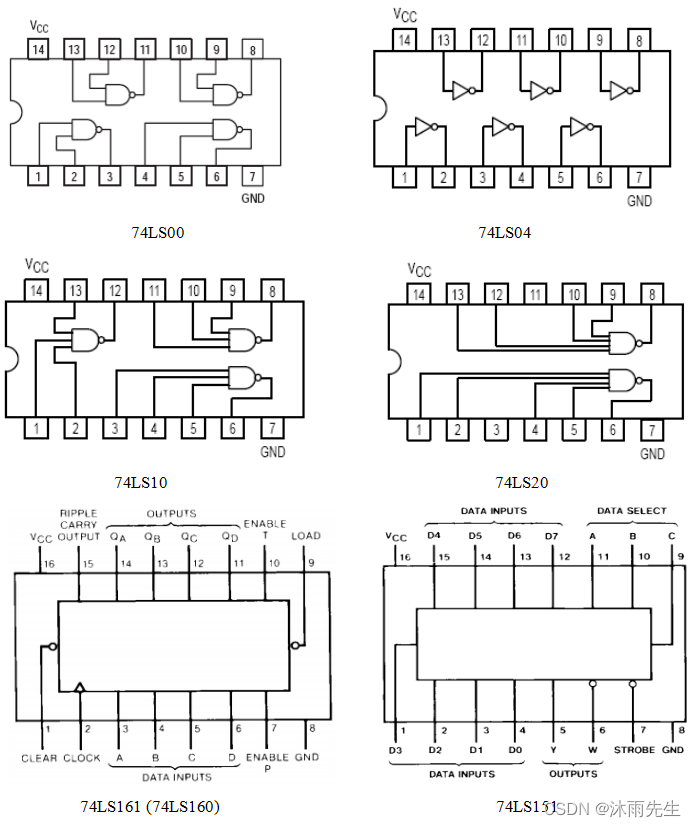

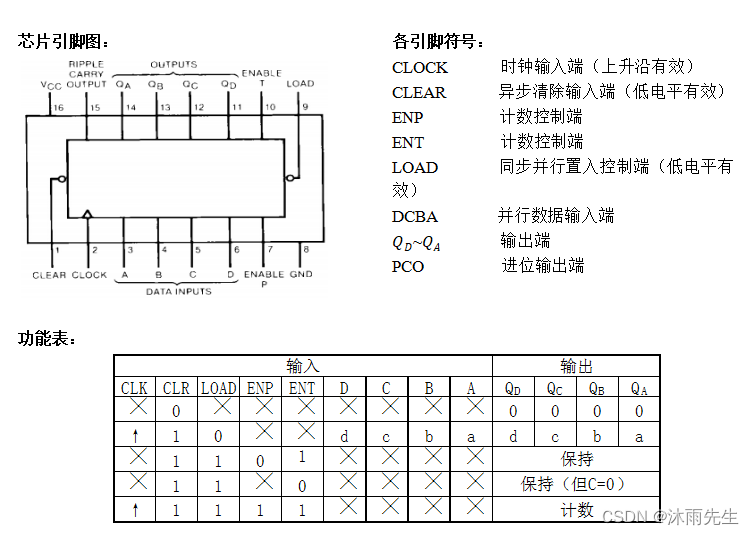

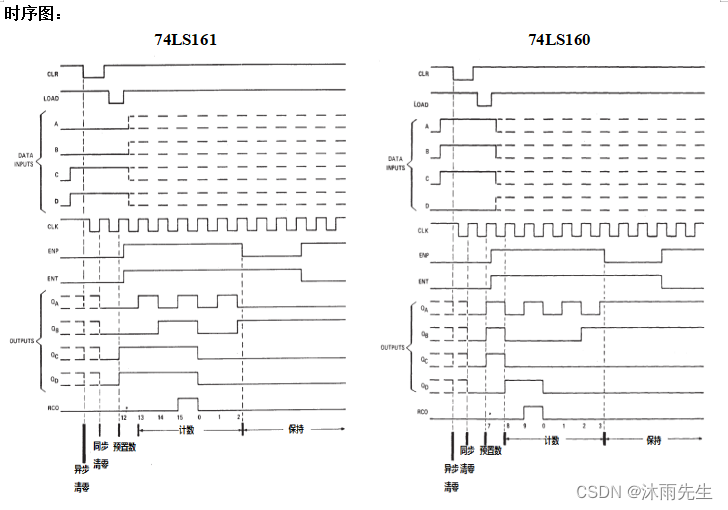

1、集成4位计数器74LS161(74LS160)简介

74LS161是4位二进制计数器, 74LS160是十进制计数器。74LS161和 74LS160芯片引脚排列相同。

(1)异步清零功能

当CLR=0时,无论其他输入端状态如何(包括时钟信号CLK),4位输出~全为零。

(2)同步并行预置数功能

当CLR=1、LOAD=0且有时钟脉冲CLK的上升沿作用时,DCBA输入端的数据将分别被~接收。

(3)保持功能

当CLR=LOAD=1且ENP=0、ENT=1时,计数器将保持原有状态不变(停止计数);

当CLR=LOAD=1且ENT=0时,计数器将保持原有状态不变(停止计数),但这时进位输出C=0。

(4)同步计数功能

当CLR=LOAD=ENP=ENT=1时,计数器处于计数状态。

从0000状态开始,对74LS161连续输入16个脉冲时,电路将从1111状态返回0000状态,进位输出PCO从高电平跳变到低电平。

从0000状态开始,对74LS160连续输入10个脉冲时,电路将从1001状态返回0000状态,进位输出PCO从高电平跳变到低电平。

2、用集成计数器设计N进制计数器的方法

若有M进制计数器,要构成N进制计数器,有两种情况:

(1)M>N,从M个状态中任选N个状态构成N 进制计数器。

(2)M<N,采用多片M进制计数器,构成M’计数器,使M’>N

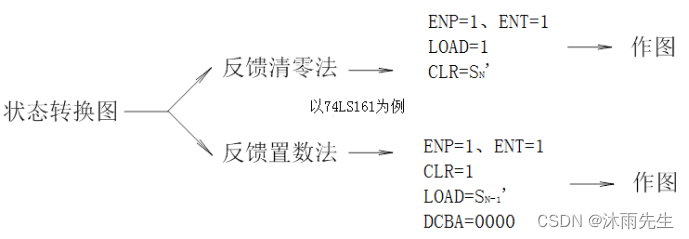

3、设计举例:试用74LS161和适当的门电路构成7进制计数器。

(1)分析:74LS161为4位二进制计数器,M=16,N=7,M>N,因此可以使用反馈清零法或反馈置数法进行设计。

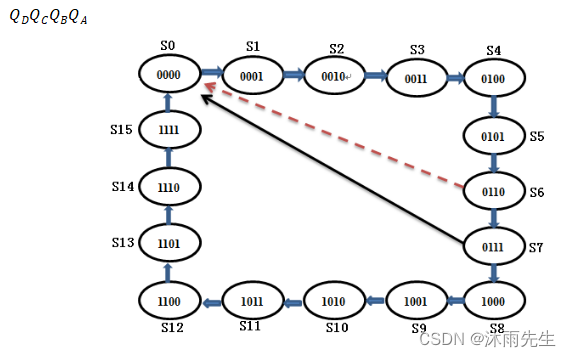

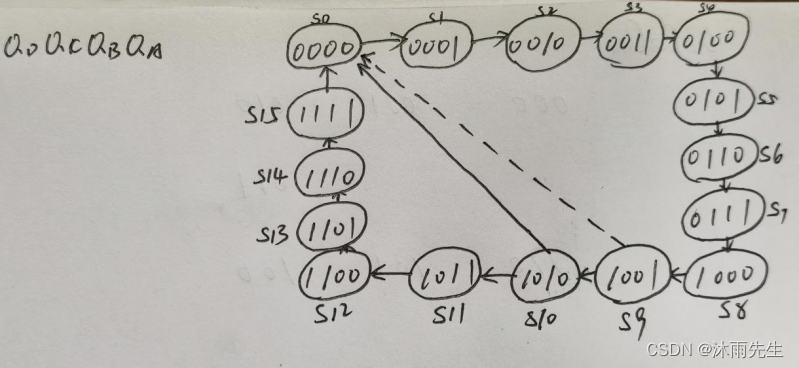

(2)状态转换图:

(3)反馈清零法:

(4)反馈置数法:

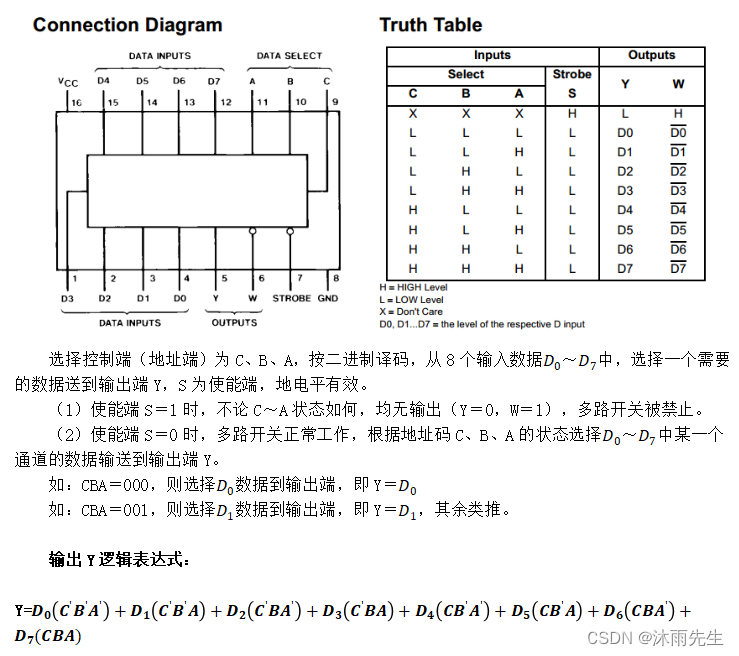

4、74LS151简介

74LS151为互补输出的8选1数据选择器,引脚排列和功能表如图所示。

四、实验内容及步骤

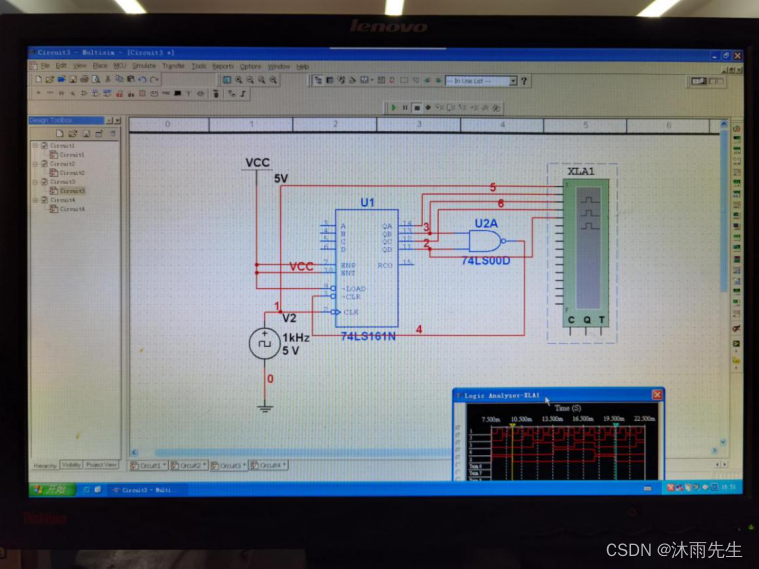

1、用集成4位二进制计数器(74LS161)组成十进制计数器

(1)画出状态转换图

(2)选择具体设计方案(清零法或置数法)

反馈清零法

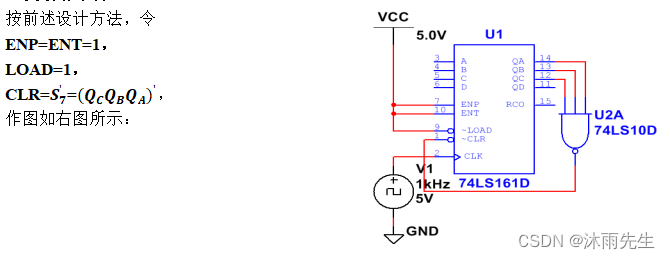

令 ENP=ENT=1,

LOAD=1,

CLR=S10’=(QDQC’QBQA’)’

作图如下图所示:

(3)画出电路图

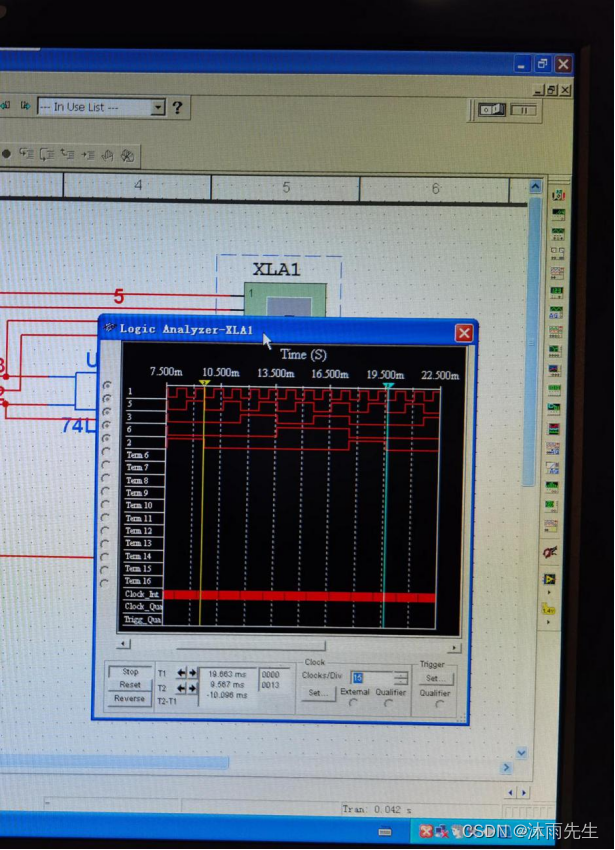

(4)数据测试,用逻辑分析仪观察并记录CLK、 Q A Q_A QA、 Q B Q_B QB、 Q C Q_C QC、 Q D 、 Q_D、 QD、PCO的时序图

用标尺截取N个时钟,观察每个时钟对应的状态,如果状态是按照N进制加法计数器的状态转换图变化,则设计正确,记录时序图。

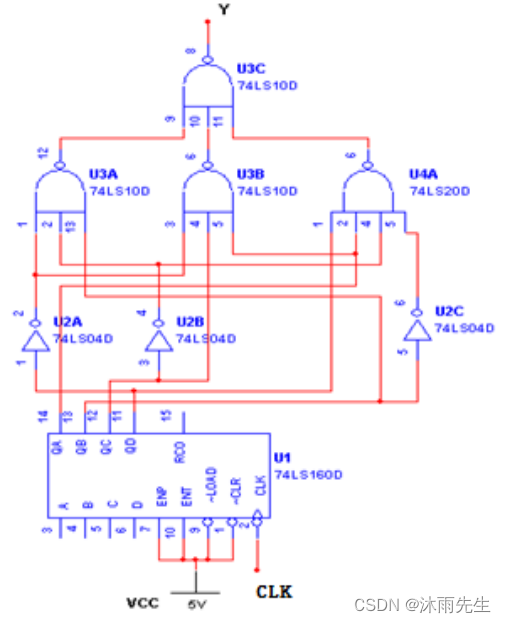

2、序列信号发生器

在数字信号的传输和数字系统的测试中,有时需要用到一组特定的串行数字信号。通常将这种串行数字信号称为序列信号。产生序列信号的电路称为序列信号发生器。

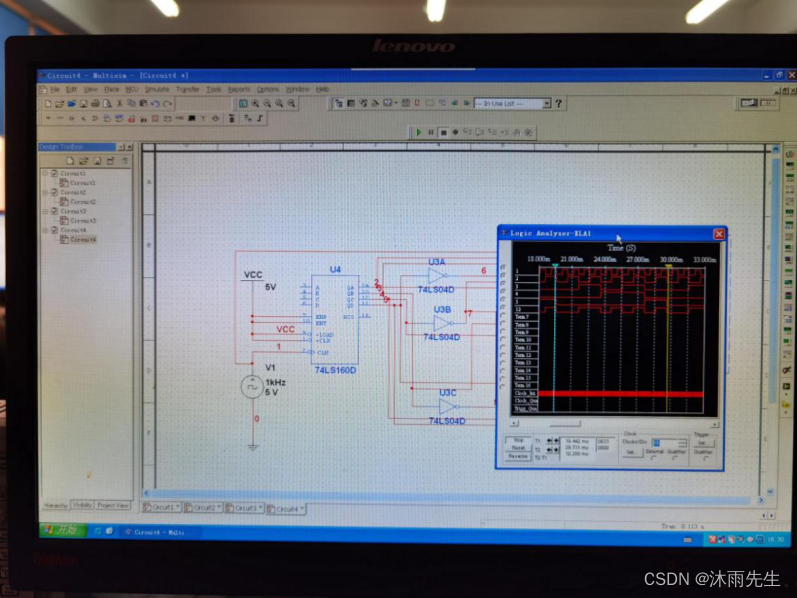

(1)右图所示为一个序列信号发生器电路。图中芯片使用74LS160同步计数器。

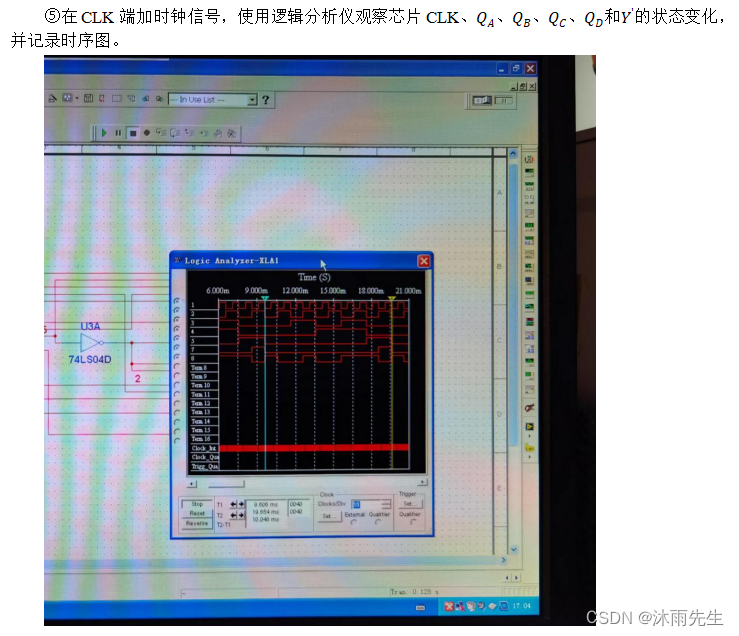

①在CLK端加时钟信号,使用逻辑分析仪观察芯片CLK、

Q

A

Q_A

QA、

Q

B

Q_B

QB、

Q

C

Q_C

QC、

Q

D

Q_D

QD、Y的状态变化,并记录时序图。

②通过观察时序图,说明电路在CLK的作用下Y端能输出什么样的脉冲序列?

Y= 0011010101

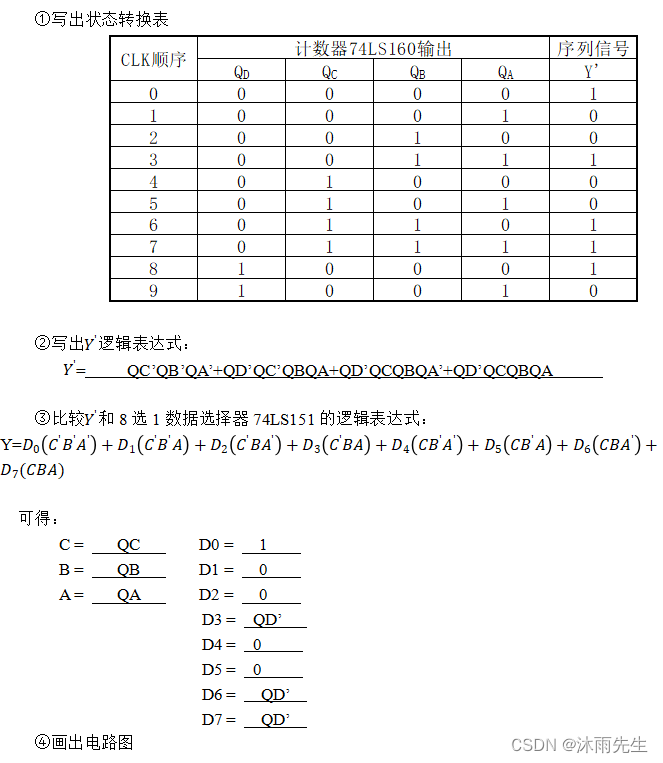

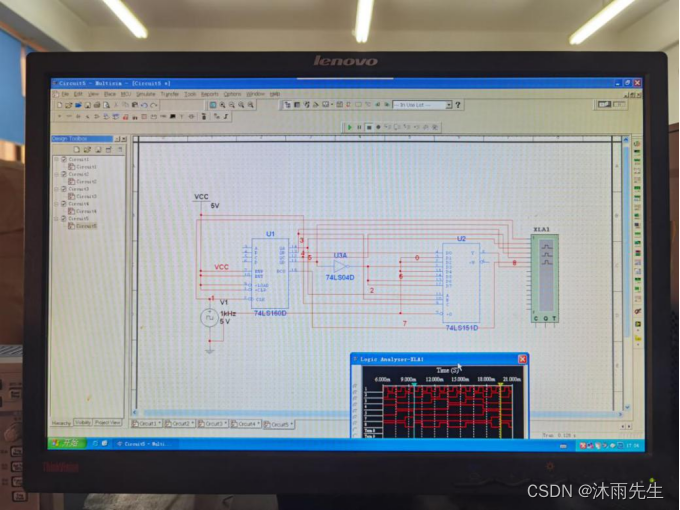

(2)若希望输出端能周期性的输出=1001001110的脉冲序列,则电路应该怎样改接?试实验之。

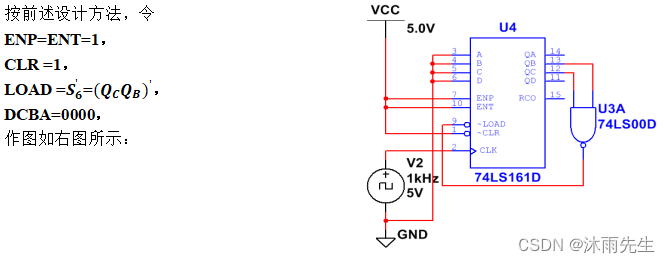

分析:序列信号发生器的构成方法有多种。一种比较简单、直观的方法是用计数器和数据选择器构成。观察的数据可知,序列位数为10,计数器仍然选择十进制计数器74LS160,再搭配一个8选1数据选择器(可选择74LS151)即可完成改接。